Go to

September 19, 2006

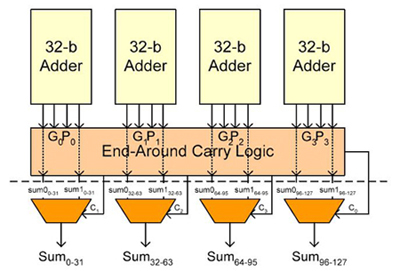

A 5Ghz+ 128-Bit Binary Floating-Point Adder for the POWER6 Processor

Xiao Yan Yu, University of California, Davis, CA - USA

Abstract: A fast 128-bit end-around carry adder is designed and fabricated as part of the POWER6 floating-point unit in a 65nm SOI process technology. Efficient use of static circuits and careful balance of the look-ahead tree enable our floatingpoint design to operate beyond 5GHz with 1.1V supply.

>

About the speaker: Xiao Yan Yu is a member of ACSEL lab directed by Prof. Vojin G. Oklobdzija and as well as a staff arithmetic circuit designer at IBM Poughkeepsie site working on the core design of IBM's next-generation servers. Ms. Yu has received B.S.C.E. and M.S.E.E. degrees from University of California - Davis in 2001 and 2003 respectively and she's currently pursuing her Ph.D. at University of California - Davis.

Download visuals (816 KB pdf)

Secondary navigation

- January 29, 2018

- August 30, 2017

- Past seminars

- 2016 - 2017 Seminars

- 2015 - 2016 Seminars

- 2014 - 2015 Seminars

- 2013 - 2014 Seminars

- 2012 - 2013 Seminars

- 2011 - 2012 Seminars

- 2010 - 2011 Seminars

- 2009 - 2010 Seminars

- 2008 - 2009 Seminars

- 2007 - 2008 Seminars

- 2006 - 2007 Seminars

- August 31, 2007

- June 29, 2007

- June 20, 2007

- June 5, 2007

- May 30, 2007

- May 16, 2007

- May 15, 2007

- April 24, 2007

- March 27, 2007

- March 14, 2007

- February 9, 2007

- February 8, 2007

- January 12, 2007

- December 5, 2006

- November 14, 2006

- October 31, 2006

- October 27, 2006

- October 26, 2006

- October 20, 2006

- September 20, 2006

- September 20, 2006

- September 20, 2006

- September 19, 2006

- 2005 - 2006 Seminars

- August 23, 2006

- August 22, 2006

- June 26, 2006

- June 20, 2006

- June 16, 2006

- June 7, 2006

- June 6, 2006

- May 30, 2006

- May 17, 2006

- May 10, 2006

- April 27, 2006

- April 12, 2006

- March 31, 2006

- March 29, 2006

- March 22, 2006

- March 15, 2006

- February 27, 2006

- February 8, 2006

- January 25, 2006

- January 19, 2006

- January 18, 2006

- January 17, 2006

- January 11, 2006

- November 30, 2005

- November 23, 2005

- November 2, 2005

- October 26, 2005

- October 25, 2005

- October 5, 2005

- September 28, 2005

- 2005 Seminars