Go to

October 5, 2005

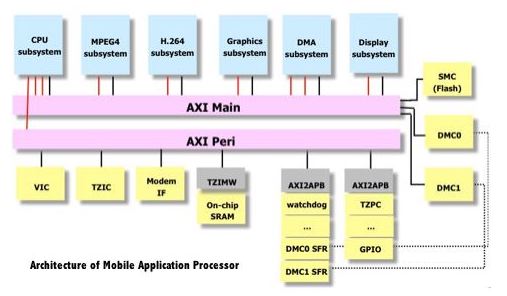

A Case Study of Mobile SoC Architecture Design Based on Transaction-Level Modeling

Eui-Young Chung, Associate Professor at Yonsei University, Seoul, Korea

Abstract: Rapid growth of the mobile application market is strongly driving the semiconductor industry for a cost-effective chip solution. Meanwhile, the design complexity of mobile SoC is rapidly increasing due to high-throughput data processing capability demands.

In this talk, we are presenting a case study of mobile SoC architecture design aiming at supporting high-throughput data processing requirements with reduced design effort. For this purpose, we adopt a Transaction-Level Modeling (TLM) method for fast and accurate system architecture exploration, especially focusing on system on-chip communication architecture. Using this method, we could easily identify the design bottlenecks from many architectural choices and improve and verify the architecture in the early design stage, which in turn reduces the overall design iteration time.

About the speaker: Eui-Young Chung recieved his BS and MS degrees from Korea University, his PhD degree from Stanford University in 1988, 1990, and 2002 respectively. He has worked as principal engineer in Samsung Electronics between 1990 - 2002. Currently, he is an associate professor at Yonsei University, Seoul, Korea.

Chung's research interests include system architecture design and methodology, low power design, VLSI CAD.

Download visuals (344 kB pdf)

Secondary navigation

- January 29, 2018

- August 30, 2017

- Past seminars

- 2016 - 2017 Seminars

- 2015 - 2016 Seminars

- 2014 - 2015 Seminars

- 2013 - 2014 Seminars

- 2012 - 2013 Seminars

- 2011 - 2012 Seminars

- 2010 - 2011 Seminars

- 2009 - 2010 Seminars

- 2008 - 2009 Seminars

- 2007 - 2008 Seminars

- 2006 - 2007 Seminars

- August 31, 2007

- June 29, 2007

- June 20, 2007

- June 5, 2007

- May 30, 2007

- May 16, 2007

- May 15, 2007

- April 24, 2007

- March 27, 2007

- March 14, 2007

- February 9, 2007

- February 8, 2007

- January 12, 2007

- December 5, 2006

- November 14, 2006

- October 31, 2006

- October 27, 2006

- October 26, 2006

- October 20, 2006

- September 20, 2006

- September 20, 2006

- September 20, 2006

- September 19, 2006

- 2005 - 2006 Seminars

- August 23, 2006

- August 22, 2006

- June 26, 2006

- June 20, 2006

- June 16, 2006

- June 7, 2006

- June 6, 2006

- May 30, 2006

- May 17, 2006

- May 10, 2006

- April 27, 2006

- April 12, 2006

- March 31, 2006

- March 29, 2006

- March 22, 2006

- March 15, 2006

- February 27, 2006

- February 8, 2006

- January 25, 2006

- January 19, 2006

- January 18, 2006

- January 17, 2006

- January 11, 2006

- November 30, 2005

- November 23, 2005

- November 2, 2005

- October 26, 2005

- October 25, 2005

- October 5, 2005

- September 28, 2005

- 2005 Seminars