Go to

February 8, 2006

Challenges and Innovations for Development of SoCs

Steve Kang, Dean of Engineering, Department of Electrical Engineering, Professor , UC Santa Cruz, CA - USA (Visiting Professor at EPFL-STI-LSM)

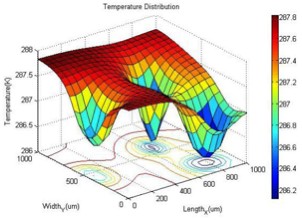

Abstract: In this talk we will review a history of integrated circuits and various technological end engineering challenges in developing a state-of-the-art System-on-a-Chip (SoC). More importantly we will also discuss innovative engineering solutions that help overcome barriers to Moore's Law, especially for development of SoCs. In particular we will discuss the thermal issues and on-chip micro-refrigerator, excessive leakage currents and circuit techniques to reduce leakages, bidirectional I/O circuits for overcoming I/O bottleneck, optical limits in mask pattern transfer, and nonlinear programming based adaptive optical lithography correction for accurate pattern transfer onto silicon surface, circuit-level design optimization through device sizing to minimize circuit's sensitivity to statistical variations for manufacturability, and 3D integration trends.

developing a state-of-the-art System-on-a-Chip (SoC). More importantly we will also discuss innovative engineering solutions that help overcome barriers to Moore's Law, especially for development of SoCs. In particular we will discuss the thermal issues and on-chip micro-refrigerator, excessive leakage currents and circuit techniques to reduce leakages, bidirectional I/O circuits for overcoming I/O bottleneck, optical limits in mask pattern transfer, and nonlinear programming based adaptive optical lithography correction for accurate pattern transfer onto silicon surface, circuit-level design optimization through device sizing to minimize circuit's sensitivity to statistical variations for manufacturability, and 3D integration trends.

About the speaker: Steve Kang obtained his Ph.D. degree from UC Berkeley in 1975, spent about 10 years at AT&T Bell Labs until he joined the ECE faculty of the University of Illinois at Urbana-Champaign (UIUC) in 1985. At UIUC, he served as professor of electrical and computer engineering, associate director of NSF engineering research center for compound semiconductor microelectronics, and department head (1995-2000). In Jan. 2001, he joined the UC Santa Cruz as Dean, Baskin School of Engineering. He was a visiting professor of EPFL in 1989, Univ. of Karlsruhe in 1996 and Technical Univ. of Munich in 1997, and visiting chair professor of KAIST in 2003. He is a fellow of IEEE, ACM, AAAS and has served as President of IEEE Circuits and Systems Society in 1991, Founding Editor-in-Chief of IEEE Trans on VLSI Systems, and on the editorial board of Prof. of the IEEE.

Download visuals (4.9 MB pdf)

Secondary navigation

- January 29, 2018

- August 30, 2017

- Past seminars

- 2016 - 2017 Seminars

- 2015 - 2016 Seminars

- 2014 - 2015 Seminars

- 2013 - 2014 Seminars

- 2012 - 2013 Seminars

- 2011 - 2012 Seminars

- 2010 - 2011 Seminars

- 2009 - 2010 Seminars

- 2008 - 2009 Seminars

- 2007 - 2008 Seminars

- 2006 - 2007 Seminars

- August 31, 2007

- June 29, 2007

- June 20, 2007

- June 5, 2007

- May 30, 2007

- May 16, 2007

- May 15, 2007

- April 24, 2007

- March 27, 2007

- March 14, 2007

- February 9, 2007

- February 8, 2007

- January 12, 2007

- December 5, 2006

- November 14, 2006

- October 31, 2006

- October 27, 2006

- October 26, 2006

- October 20, 2006

- September 20, 2006

- September 20, 2006

- September 20, 2006

- September 19, 2006

- 2005 - 2006 Seminars

- August 23, 2006

- August 22, 2006

- June 26, 2006

- June 20, 2006

- June 16, 2006

- June 7, 2006

- June 6, 2006

- May 30, 2006

- May 17, 2006

- May 10, 2006

- April 27, 2006

- April 12, 2006

- March 31, 2006

- March 29, 2006

- March 22, 2006

- March 15, 2006

- February 27, 2006

- February 8, 2006

- January 25, 2006

- January 19, 2006

- January 18, 2006

- January 17, 2006

- January 11, 2006

- November 30, 2005

- November 23, 2005

- November 2, 2005

- October 26, 2005

- October 25, 2005

- October 5, 2005

- September 28, 2005

- 2005 Seminars