Go to

November 30, 2005

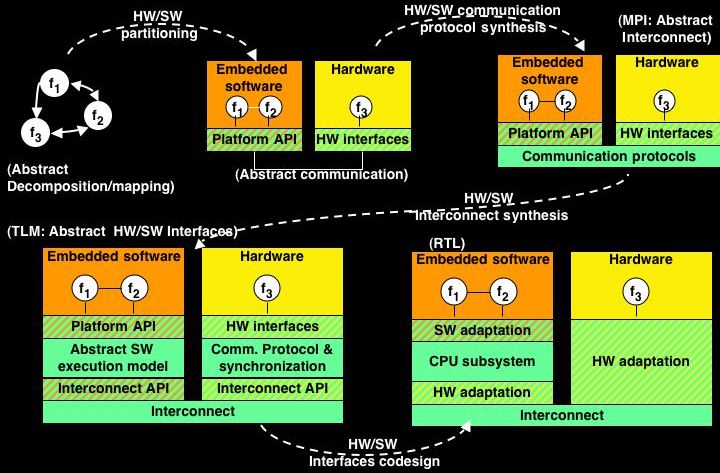

A Unified HW/SW Interface Model to Remove Discontinuities Between HW and SW Design

Ahmed Jerraya, TIMA Laboratory, Grenoble, France

Abstract: Modern SoC (System on Chip) may include one or several CPU sub-systems to execute software and sophisticated interconnect in addition to specific hardware sub-systems. SoC are generally application specific and require efficient HW/SW interfaces design.

Abstract HW-SW Interfaces are extensively used to coordinate software and hardware communities for the design of classic computers. Abstract HW-SW Interfaces allow concurrent design of complex systems made of sophisticated software and hardware platforms. Examples include API at different abstraction levels, RTOS libraries, drivers, typically summarized as hardware dependent software. This abstraction smoothes the design flow and eases interaction between different teams belonging to different cultures, hardware, software and system architecture. In this classical scheme, HW/SW interfaces are modelled twice. HW designers use a HW/SW interface model to test their hardware design, and software designers use a HW/SW interface model to validate the functionality of their software. The use of two separate models induces a discontinuity between hardware and software. This generates cost and performances overheads that are not acceptable for SoC design. A single HW/SW interface needs to be shared between both hardware and software designers since the early stage of SoC design.

HW-SW interfaces abstraction levels

This presentation deals with a unified HW/SW model to describe different parts of HW/SW interface at different abstraction levels. The benefits of using the proposed model are two fold: first, it provides a single model to present system design from abstract specification to mixed HW/SW implementation and second, it enables full system simulation at different abstraction level during refinement flow.

About the speaker: Dr. Jerraya has the grade of Research Director within the CNRS and is currently managing the System-Level Synthesis group of TIMA Laboratory where he is working on application specific multiprocessor System on Chip.

Dr. Ahmed Amine Jerraya received the Engineer degree from the University of Tunis in 1980 and the D.E.A., "Docteur Ingénieur", and the "Docteur d'Etat" degrees from the University of Grenoble in 1981, 1983, and 1989 respectively, all in computer sciences. In 1986, he held a full research position with the CNRS (Centre National de la Recherche Scientifique). From April 1990 to March 1991, he was a Member of the Scientific Staff at Nortel in Canada, working on linking system design tools and hardware design environments.

He served as the General Chair of DATE 2001 and co-founded the International Seminar on Multi-Processor SoC held every year in July. He co-authored 6 books and more than 200 papers in International Conferences and Journals. He received the Best Paper Award at the 1994 ED&TC for his work on Hardware/Software Co-simulation.

Download visuals (1.4 MB pdf)

Secondary navigation

- January 29, 2018

- August 30, 2017

- Past seminars

- 2016 - 2017 Seminars

- 2015 - 2016 Seminars

- 2014 - 2015 Seminars

- 2013 - 2014 Seminars

- 2012 - 2013 Seminars

- 2011 - 2012 Seminars

- 2010 - 2011 Seminars

- 2009 - 2010 Seminars

- 2008 - 2009 Seminars

- 2007 - 2008 Seminars

- 2006 - 2007 Seminars

- August 31, 2007

- June 29, 2007

- June 20, 2007

- June 5, 2007

- May 30, 2007

- May 16, 2007

- May 15, 2007

- April 24, 2007

- March 27, 2007

- March 14, 2007

- February 9, 2007

- February 8, 2007

- January 12, 2007

- December 5, 2006

- November 14, 2006

- October 31, 2006

- October 27, 2006

- October 26, 2006

- October 20, 2006

- September 20, 2006

- September 20, 2006

- September 20, 2006

- September 19, 2006

- 2005 - 2006 Seminars

- August 23, 2006

- August 22, 2006

- June 26, 2006

- June 20, 2006

- June 16, 2006

- June 7, 2006

- June 6, 2006

- May 30, 2006

- May 17, 2006

- May 10, 2006

- April 27, 2006

- April 12, 2006

- March 31, 2006

- March 29, 2006

- March 22, 2006

- March 15, 2006

- February 27, 2006

- February 8, 2006

- January 25, 2006

- January 19, 2006

- January 18, 2006

- January 17, 2006

- January 11, 2006

- November 30, 2005

- November 23, 2005

- November 2, 2005

- October 26, 2005

- October 25, 2005

- October 5, 2005

- September 28, 2005

- 2005 Seminars