Go to

May 18, 2005

Self-Calibrating Networks-on-Chip

Frédéric Worm, PhD Student at EPFL-IC-LAP

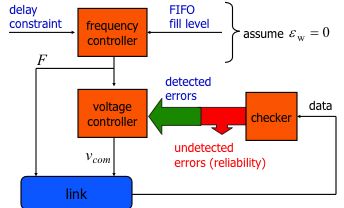

Abstract: Networks-on-chip provide an elegant framework to efficiently reuse pre-designed cores. However, reuse of cores is  jeopardized by new deep sub-micron noise effects that challenge reliability of CMOS technology. Moreover, noise margins are further reduced as supply voltage scale down. We advocate that self-calibrating techniques will be needed to maintain acceptable design trade-off between energy, performance, and reliability. As a result, self-calibrating techniques have to be integrated within networks-on-chip. This paper presents a self-calibrating link and discusses qualitatively the problem of controlling adaptively its voltage and frequency.

jeopardized by new deep sub-micron noise effects that challenge reliability of CMOS technology. Moreover, noise margins are further reduced as supply voltage scale down. We advocate that self-calibrating techniques will be needed to maintain acceptable design trade-off between energy, performance, and reliability. As a result, self-calibrating techniques have to be integrated within networks-on-chip. This paper presents a self-calibrating link and discusses qualitatively the problem of controlling adaptively its voltage and frequency.

Download visuals (pdf 96 KB)

Secondary navigation

- January 29, 2018

- August 30, 2017

- Past seminars

- 2016 - 2017 Seminars

- 2015 - 2016 Seminars

- 2014 - 2015 Seminars

- 2013 - 2014 Seminars

- 2012 - 2013 Seminars

- 2011 - 2012 Seminars

- 2010 - 2011 Seminars

- 2009 - 2010 Seminars

- 2008 - 2009 Seminars

- 2007 - 2008 Seminars

- 2006 - 2007 Seminars

- August 31, 2007

- June 29, 2007

- June 20, 2007

- June 5, 2007

- May 30, 2007

- May 16, 2007

- May 15, 2007

- April 24, 2007

- March 27, 2007

- March 14, 2007

- February 9, 2007

- February 8, 2007

- January 12, 2007

- December 5, 2006

- November 14, 2006

- October 31, 2006

- October 27, 2006

- October 26, 2006

- October 20, 2006

- September 20, 2006

- September 20, 2006

- September 20, 2006

- September 19, 2006

- 2005 - 2006 Seminars

- August 23, 2006

- August 22, 2006

- June 26, 2006

- June 20, 2006

- June 16, 2006

- June 7, 2006

- June 6, 2006

- May 30, 2006

- May 17, 2006

- May 10, 2006

- April 27, 2006

- April 12, 2006

- March 31, 2006

- March 29, 2006

- March 22, 2006

- March 15, 2006

- February 27, 2006

- February 8, 2006

- January 25, 2006

- January 19, 2006

- January 18, 2006

- January 17, 2006

- January 11, 2006

- November 30, 2005

- November 23, 2005

- November 2, 2005

- October 26, 2005

- October 25, 2005

- October 5, 2005

- September 28, 2005

- 2005 Seminars