Go to

September 28, 2005

A Methodology for A-Priori Statistical Analysis of Functional Fault-Tolerance of Nanometer-Scale Digital Systems

Milos Stanisavljevic, PhD Assistant at EPFL-STI-LSM

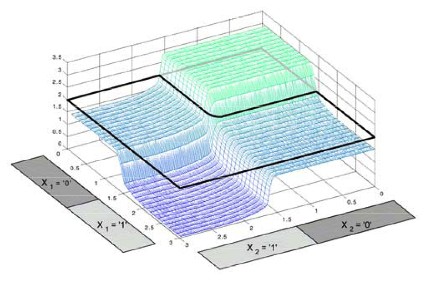

Abstract: This work presents a new approach for monitoring and estimating device reliability of nanometer-scale devices prior to  fabrication. The presented approach is equally applicable to novel nano-scale quantum devices (single-electron transistors and silicon nanowires), as well as to failure-prone nanometer scale CMOS devices. A four-layer architecture exhibiting a large immunity to permanent as well as random failures is used. A complete tool for a-priori functional fault tolerance analysis was developed. It is a conceptually new realization of statistical, Monte Carlo based, tool that induces different failure models, and does subsequent evaluation of system reliability under realistic constraints. Analysis of distinctive cases and topologies is performed. A structured fault modeling architecture is also proposed, which, together with the tool, is part of the new reliability design method representing a compatible improvement of existing IC design methodologies.

fabrication. The presented approach is equally applicable to novel nano-scale quantum devices (single-electron transistors and silicon nanowires), as well as to failure-prone nanometer scale CMOS devices. A four-layer architecture exhibiting a large immunity to permanent as well as random failures is used. A complete tool for a-priori functional fault tolerance analysis was developed. It is a conceptually new realization of statistical, Monte Carlo based, tool that induces different failure models, and does subsequent evaluation of system reliability under realistic constraints. Analysis of distinctive cases and topologies is performed. A structured fault modeling architecture is also proposed, which, together with the tool, is part of the new reliability design method representing a compatible improvement of existing IC design methodologies.

About the speaker: Milos Stanisavljevic graduated from the University of Belgrade with a degree in Electronics Engineering in April 2004. Currently he is a PhD assistant at the Microelectronic Systems Laboratory, EPFL. Milos has received various awards in national competitions on physics and mathematics. Most recently he won the first place in an international electronics competition of students from Yugoslavia and Serbia in 2002. His research interests include reliability of nanometer-scale systems.

Download visuals (2.1 MB pdf)

Secondary navigation

- January 29, 2018

- August 30, 2017

- Past seminars

- 2016 - 2017 Seminars

- 2015 - 2016 Seminars

- 2014 - 2015 Seminars

- 2013 - 2014 Seminars

- 2012 - 2013 Seminars

- 2011 - 2012 Seminars

- 2010 - 2011 Seminars

- 2009 - 2010 Seminars

- 2008 - 2009 Seminars

- 2007 - 2008 Seminars

- 2006 - 2007 Seminars

- August 31, 2007

- June 29, 2007

- June 20, 2007

- June 5, 2007

- May 30, 2007

- May 16, 2007

- May 15, 2007

- April 24, 2007

- March 27, 2007

- March 14, 2007

- February 9, 2007

- February 8, 2007

- January 12, 2007

- December 5, 2006

- November 14, 2006

- October 31, 2006

- October 27, 2006

- October 26, 2006

- October 20, 2006

- September 20, 2006

- September 20, 2006

- September 20, 2006

- September 19, 2006

- 2005 - 2006 Seminars

- August 23, 2006

- August 22, 2006

- June 26, 2006

- June 20, 2006

- June 16, 2006

- June 7, 2006

- June 6, 2006

- May 30, 2006

- May 17, 2006

- May 10, 2006

- April 27, 2006

- April 12, 2006

- March 31, 2006

- March 29, 2006

- March 22, 2006

- March 15, 2006

- February 27, 2006

- February 8, 2006

- January 25, 2006

- January 19, 2006

- January 18, 2006

- January 17, 2006

- January 11, 2006

- November 30, 2005

- November 23, 2005

- November 2, 2005

- October 26, 2005

- October 25, 2005

- October 5, 2005

- September 28, 2005

- 2005 Seminars