Go to

February 8, 2007

Design of Nanometer MOS Current Mode Logic (MCML): basic concepts and perspectives

Massimo Alioto, Department of Computer Engineering, University of Siena, Italy

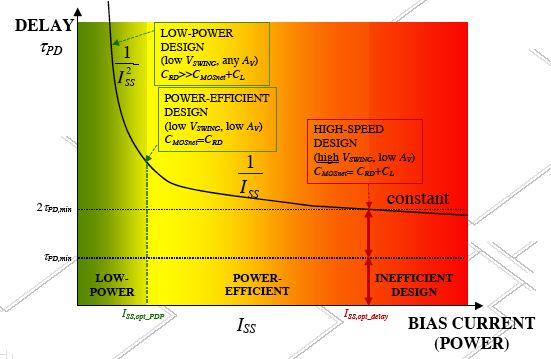

Abstract: In the last years, MOS Current-Mode Logic (MCML) circuits have become increasingly popular in a wide range of applications, from high-accuracy mixed-signal circuits to very high-speed circuits. Since desirable features come at the cost of static power consumption, the power-delay trade-off is a crucial design aspect in the MCML logic style.

In this seminar, simple models developed in the context of sub-100 nm CMOS technologies will be covered. These models are used to manage the power-delay trade-off, as well as to derive practical design guidelines. A deep insight into the properties of MCML circuits is gained, which is essential for both the efficient design of MCML cells and the development of an automated design flow.

Open questions and aspects that require further investigation are finally discussed, along with some new directions in the design of MCML gates in the nanometer regime.

About the speaker: Massimo Alioto was born in Brescia, Italy, in 1972. He received the laurea degree (MS) in Electronics Engineering and the Ph.D. degree in Electrical Engineering from the University of Catania (Italy) in 1997 and 2001, respectively. In 2002, he joined the Dipartimento di Ingegneria dell'Informazione (DII) of the University of Siena, where he is currently Associate Professor.

Since 2001 he has been teaching undergraduate and graduate courses on basic electronics, microelectronics and advanced VLSI digital design. He has authored or co-authored about 90 journals and conference papers. He is co-author of the book Model and Design of Bipolar and MOS Current-Mode Logic: CML, ECL and SCL Digital Circuits (Springer, 2005).

His primary research interests include the design and modeling of nanometer CMOS high-performance digital circuits in terms of high-speed and/or low-power dissipation, as well as arithmetic circuits, circuits for cryptographic applications and bipolar high-speed circuits.

Download visuals (508 KB pdf)

Secondary navigation

- January 29, 2018

- August 30, 2017

- Past seminars

- 2016 - 2017 Seminars

- 2015 - 2016 Seminars

- 2014 - 2015 Seminars

- 2013 - 2014 Seminars

- 2012 - 2013 Seminars

- 2011 - 2012 Seminars

- 2010 - 2011 Seminars

- 2009 - 2010 Seminars

- 2008 - 2009 Seminars

- 2007 - 2008 Seminars

- 2006 - 2007 Seminars

- August 31, 2007

- June 29, 2007

- June 20, 2007

- June 5, 2007

- May 30, 2007

- May 16, 2007

- May 15, 2007

- April 24, 2007

- March 27, 2007

- March 14, 2007

- February 9, 2007

- February 8, 2007

- January 12, 2007

- December 5, 2006

- November 14, 2006

- October 31, 2006

- October 27, 2006

- October 26, 2006

- October 20, 2006

- September 20, 2006

- September 20, 2006

- September 20, 2006

- September 19, 2006

- 2005 - 2006 Seminars

- August 23, 2006

- August 22, 2006

- June 26, 2006

- June 20, 2006

- June 16, 2006

- June 7, 2006

- June 6, 2006

- May 30, 2006

- May 17, 2006

- May 10, 2006

- April 27, 2006

- April 12, 2006

- March 31, 2006

- March 29, 2006

- March 22, 2006

- March 15, 2006

- February 27, 2006

- February 8, 2006

- January 25, 2006

- January 19, 2006

- January 18, 2006

- January 17, 2006

- January 11, 2006

- November 30, 2005

- November 23, 2005

- November 2, 2005

- October 26, 2005

- October 25, 2005

- October 5, 2005

- September 28, 2005

- 2005 Seminars