Go to

GALAXY

GALS interfAce for compleX digital sYstem integration (GALAXY)

Centre SI is participating in a European project accepted for funding by the European commission within the Seventh Research Framework Program (FP7). The project consortium consists of very experienced partners in the areas related to the project; a total of six project partners coming from four different countries. The consortium submitted a STREP (small or medium scale focused research project) proposal for FP7 call ICT-2007.3.3 in Embedded Systems Design, back in May 2007. It includes the German company Innovations for High Performance Microelectronics GmbH (IHP) as the coordinator; Infineon Technologies from Germany, University of Manchester and Silistix Limited from the United Kingdom; University of Bologna from Italy, and Center SI representing EPFL from Switzerland.

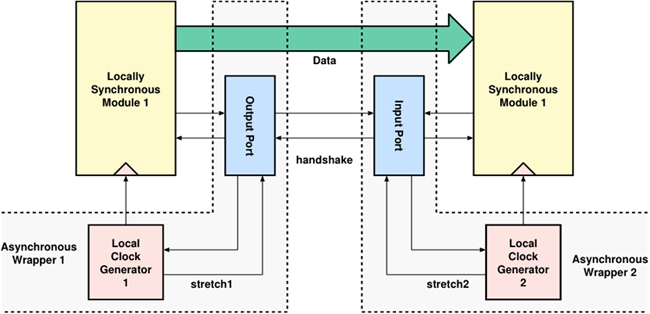

The consortium proposes to provide an integrated GALS (Globally Asynchronous, Locally Synchronous) design flow, together with novel Network-on-Chip capabilities that will materially aid embedded system design for providing an interoperability framework between the existing open and commercial CAD tools that will support development of heterogeneous systems at the different levels of abstraction. The project will evaluate the ability of the GALS approach to solve system integration issues and, by implementing a complex wireless communication system on an advanced 45nm CMOS process, explore the low EMI properties, inherent low-power features and robustness to process variability problems in nanoscale geometries.

Overview:

This project covers several innovative issues that can be summarized as follows:

- Implementation of the automated and integrated Globally Asynchronous, Locally Synchronous (GALS) design flow that is completely missing at present.

- Optimization of GALS interfaces and especially improvements in pausible clocking calibration mechanisms.

- Additionally, in the context of the project, exploration of the EMI and power reduction possible with GALS circuits. Until now, these subjects have been covered just marginally or only at the theoretical level.

- Exploration of the transition from conservative synchronous implementations of NoCs to GALS compliant NoCs.

- GALS design has not previously been explored for deep submicron technologies. The main results of the effectiveness of GALS are based up to now on almost obsolete 0.25 µm processes although some new results were achieved in 0.13 µm CMOS process implementations. The system design in a 45 nm CMOS process will give completely new value to the achieved results.

- Process improvements introduces additional and, up to now, unsolved challenges such as variability and reliability. These issues and how a GALS methodology can solve such challenges will be covered in this project. The elaborated concepts will be proven in practice.

Project Participants:

Two research laboratories from Centre SI will be collaborating in this project:

Integrated Systems Laboratory (LSI - Prof. Giovanni De Micheli)

Microelectronic Systems Laboratory (LSM - Prof. Yusuf Leblebici)