# SCIENTIFIC **REPORTS**

Received: 24 November 2016 Accepted: 27 February 2017 Published: 30 March 2017

## **OPEN** Scaling trends and performance evaluation of 2-dimensional polarity-controllable FETs

Giovanni V. Resta<sup>1</sup>, Tarun Agarwal<sup>2,3</sup>, Dennis Lin<sup>2</sup>, Iuliana P. Radu<sup>2</sup>, Francky Catthoor<sup>2,3</sup>, Pierre-Emmanuel Gaillardon<sup>4</sup> & Giovanni De Micheli<sup>1</sup>

Two-dimensional semiconducting materials of the transition-metal-dichalcogenide family, such as MoS<sub>2</sub> and WSe<sub>2</sub>, have been intensively investigated in the past few years, and are considered as viable candidates for next-generation electronic devices. In this paper, for the first time, we study scaling trends and evaluate the performances of polarity-controllable devices realized with undoped mono- and bi-layer 2D materials. Using ballistic self-consistent quantum simulations, it is shown that, with the suitable channel material, such polarity-controllable technology can scale down to 5 nm gate lengths, while showing performances comparable to the ones of unipolar, physically-doped 2D electronic devices.

Miniaturization of silicon-based CMOS devices has been the main drive of the silicon industry for nearly half a century, and has allowed an exponential increase in computing power, as embodied by Moore's law. With physical gate lengths slowly approaching 10 nm, the limits of current silicon technology are becoming increasingly difficult to overcome, and new semiconductor materials and novel device concepts have been studied, that could ultimately outperform silicon<sup>1,2</sup>. Among the materials that have been studied as a semiconducting channel for charge-based devices, 2-dimensional (2D) materials of the transition-metal-dichalcogenide (TMDCs) family<sup>3</sup> are one of the most exciting and promising opportunities, thanks to their electrical and physical properties<sup>4,5</sup>. The presence of a sizeable bandgap  $(1 \sim 2 \text{ eV})$  makes TMDCs materials appealing for electronics applications, as it allows us to realize devices with low leakage floor and high ON/OFF current ratios<sup>6-10</sup>. Amongst the other remarkable features of TMDCs, their layered structure provides 2D films of controllable uniform thickness with dangling-bonds free interfaces. Moreover, their extreme thinness and low in-plane dielectric constant alleviate short-channel effects (SCE) and drain-induced-barrier-lowering (DIBL)<sup>11,12</sup>, which are detrimental to device performances. The high effective mass of charge carriers (especially with respect to III-V materials) helps reducing direct source-to-drain tunneling at ultra-scaled dimensions<sup>13,14</sup>, providing a better control of the device OFF-state by the gate terminals. Furthermore, 2-dimensional materials are attractive for monolithic integration on top of CMOS or multi-stacking of TMDCs layers<sup>15</sup>, thanks to the low thermal budget needed in the fabrication process.

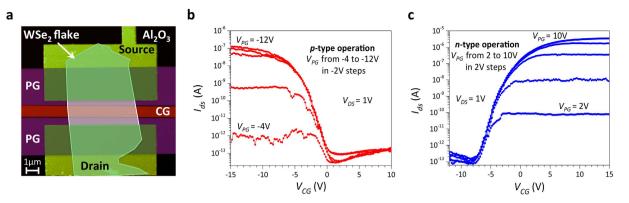

The most studied material of the TMDCs family, MoS<sub>2</sub>, has proven to be a viable solution for the realization of n-MOS transistors<sup>6,7</sup>, and ultra-scaled n-type devices have been recently demonstrated<sup>16,17</sup>. Short channel MoS<sub>2</sub> *p*-type FETs fabricated with doped silicon contacts<sup>18</sup> have also been reported, however, MoS<sub>2</sub> has not experimentally shown any ambipolar behaviour, which is essential for the realization of polarity-controllable devices. Reports of ambipolar contacts to MoS<sub>2</sub> are in fact limited to devices realized on thick flakes on a PMMA substrate<sup>19</sup> or devices gated with ionic liquids<sup>20</sup>. So far, the most promising material for the realization of both n- and p-type devices is arguably tungsten diselenide (WSe<sub>2</sub>), for which high carrier mobility<sup>21</sup>, ambipolar behavior<sup>22</sup> and CMOS devices have been reported experimentally<sup>8,9</sup>. The ambipolar behavior of WSe<sub>2</sub> has recently been exploited to realize polarity-controllable devices, based on undoped Schottky-barrier (SB) double-independent-gate (DIG) FETs<sup>23</sup>, as shown in Fig. 1. The device, presented in Fig. 1a, was experimentally realized on a WSe<sub>2</sub> flake, and buried DIG gates were used to control its polarity and ON/OFF status<sup>23</sup>. The need for physical doping of the devices

<sup>1</sup>Integrated System Laboratory (LSI), School of Engineering, École Polytechnique Fédérale de Lausanne (EPFL), CH-1015 Lausanne, Switzerland. <sup>2</sup>IMEC, Kapeldreef 75, B-3001 Leuven, Belgium. <sup>3</sup>KU Leuven, Celestijnenlaan 200D, B-3001, Leuven, Belgium. <sup>4</sup>Laboratory of NanoIntegrated Systems (LNIS), Department of Electrical and Computer Engineering, University of Utah, Salt-Lake City, Utah 84112, USA. Correspondence and requests for materials should be addressed to G.V.R. (email: giovanni.resta@epfl.ch) or I.P.R. (email: iuliana.radu@imec.be) or P.-E.G. (email: pierre-emmanuel.gaillardon@utah.edu)

Figure 1. Experimental demonstration of polarity-controllable behavior in WSe<sub>2</sub>. (a) AFM topography image of the experimental device, recolored to highlight the device structure. Both the PG and CG were realized as bottom-gates. The thickness of the flake was 7.5 nm. (b) *p*-type transfer characteristics measured sweeping the voltage applied to the control gate ( $V_{CG}$ ) at different negative  $V_{PG}$  voltages. (c) *n*-type transfer curves measured on the same device with positive voltages applied to the PG. The experimental device had 1.5 µm channel length and 5.5 µm channel width.

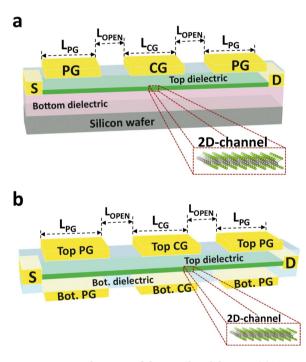

**Figure 2. 3D** schematic of the simulated devices. (a) Topgate (TG) device structure. (b) Double-gate (DG) device structure. In both schematics the semiconducting 2D channel is highlighted, with its atomic structure shown in the dashed boxes.

is eliminated, and the Schottky barriers created at the source and drain contact are tuned by an additional gate, namely program gate (PG), in order to select the charge carriers that can be injected in the channel. This class of devices allows the dynamic selection of the transistor polarity by the use of the PG, acting at the contact interfaces, while the control gate (CG), placed in the central region of the channel, controls the ON/OFF status of the device, as measured in Fig. 1(b,c).

The possibility of using electrostatic doping to control the device polarity avoids any complicated doping step during the fabrication process, to the benefit of fabrication simplicity and device regularity. In fact, no separate fabrication process is needed for *n*- or *p*-type devices, as the polarity can be dynamically controlled at runtime by the PG. Moreover, the device switching properties become more expressive, as each device is now acting as a comparison-driven switch and will allow the realization of compact logic gates, thus improving the computational density in 2D-flatronics<sup>23,24</sup>. However, to date, scaling opportunities with 2D materials have been theoretically explored only in unipolar, physically-doped devices, with Ohmic contacts<sup>11-14,25</sup>. This has been done disregarding the great difficulties that the accurate and controlled doping of the material brings to the fabrication

|                                                | 1L WSe <sub>2</sub> | 2L WSe <sub>2</sub> | 2L MX <sub>2</sub> |

|------------------------------------------------|---------------------|---------------------|--------------------|

| a (Å)                                          | 0.328               | 0.328               | 0.370              |

| E <sub>G</sub> (eV)                            | 1.5                 | 1.1                 | 0.8                |

| ${\pmb \phi}_{\scriptscriptstyle SB}({ m eV})$ | 0.75                | 0.55                | 0.4                |

| m <sub>e</sub>                                 | 0.33                | 0.33                | 0.3                |

| m <sub>h</sub>                                 | 0.45                | 0.45                | 0.4                |

**Table 1.** Material properties used to construct the effective mass Hamiltonian. a is the lattice constant,  $E_G$  the bandgap,  $\phi_{SB}$  the Schottky-barrier height at source and drain and  $m_e$ ,  $m_h$  are the effective masses.

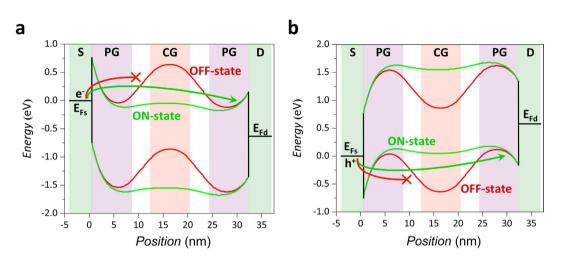

Figure 3. Band-diagrams of the 4 regions of operation extracted from the simulation with monolayer WSe<sub>2</sub> at LG = 8 nm. (a) *n*-type operation, for  $V_{PG} = 1$  V. The program gate (PG) sets the polarity of the device, by thinning the Schottky barrier (SB) for electrons (e<sup>-</sup>) at source and drain, while the control gate (CG) controls the ON/OFF switching of the FET. In the OFF-state ( $V_{CG} = 0$  V), the potential barrier, created in the channel by the CG, blocks electron conduction from source to drain (red crossed line). In the ON-state, with the band diagram extracted at  $V_{CG} = 0.8$  V, the barrier is removed and electron conduction takes place (green arrow). (b) *p*-type operation for  $V_{PG} = -1$  V. In this case, the negative voltage applied to the PG enables holes (h<sup>+</sup>) to be injected in the channel at source (green arrow). In a similar way, as described for *n*-type operation, the potential barrier created by the CG blocks the flow of holes from source to drain (red crossed line).

process, i.e., doping is already one of the major sources of variability in silicon CMOS devices<sup>26</sup>, and that achieving Ohmic contact to 2D materials has, so far, proven to be a challenging task. Here we study, for the first time, scaling opportunities for polarity-controllable devices based on 2D materials of the TMDCs family. To estimate the electrical characteristics of such ultra-scaled devices, we use ballistic self-consistent quantum simulations in the non-equilibrium Green's function (NEGF) formalism, as described in Methods. We first explore scaling for devices based on WSe<sub>2</sub>, the most promising material for which experimental results, presented in Fig. 1, are available<sup>23</sup>, and then focus on the selection of novel 2D semiconductor, for which experimental demonstrations are still lacking, to enhance the performances of the device. We show that such device can achieve performances that are comparable to unipolar doped devices with Ohmic contacts simulated with a similar approach, while bringing considerable simplifications to the fabrication process and bearing the promise of enhanced performances at circuit level.

#### Methodology

Figure 2 shows the 3D schematic structures of the simulated devices with top-gate (TG) and double-gate (DG) geometry (Fig. 2(a,b), respectively). In the top-gate configuration,  $HfO_2$  ( $\kappa = 25$ , equivalent oxide thickness (EOT) = 0.47 nm) was used as top dielectric, while SiO<sub>2</sub> ( $\kappa = 3.9$ , EOT = 30 nm) was considered as bottom dielectric. For the double-gate geometry  $HfO_2$  ( $\kappa = 25$ , EOT = 0.47 nm) was used for top and bottom gate dielectrics. We modeled the 2D semiconducting channel with a 2-band tight-binding (TB) Hamiltonian, created from the material properties shown in Table 1 (see also Methods).

The model was extended to bilayer 2D materials by adding an interlayer hopping parameter in the effective-mass Hamiltonian, to account for coupling between the two layers<sup>27</sup>. We studied the device switching properties performing self-consistent ballistic simulations, iteratively solving Poisson and Schrödinger equation (within the NEGF formalism), with an open-source quantum transport code<sup>28,29</sup>. No doping was introduced at source and drain contacts for both gate geometries and we assumed mid-gap SB contacts, to have symmetric characteristics for the two polarities. We evaluated the device performances at different gate lengths, keeping the same length for both the CG and PG gates ( $L_{CG} = L_{PG}$ ) and fixing the length of the ungated channel region

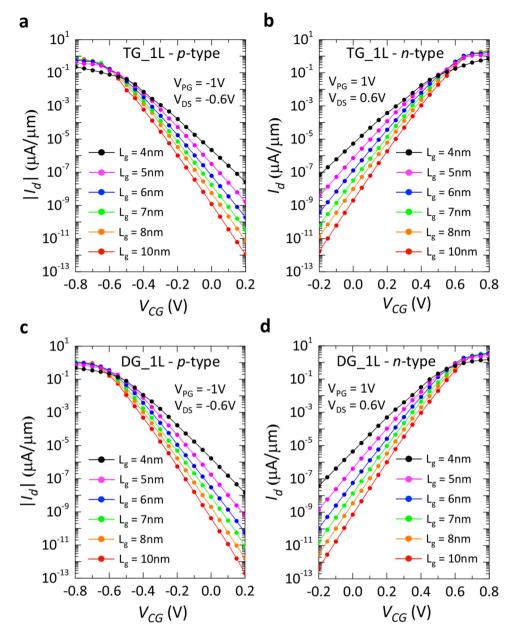

Figure 4. Simulated transfer characteristics for monolayer-WSe<sub>2</sub> polarity-controllable FETs at different gate lengths. Monolayer-WSe<sub>2</sub> was modeled with 1.5 eV bandgap and the hopping parameters of the effective mass Hamiltonian were calculated using an effective mass ( $m_e$ ) of 0.33  $m_0$  for electrons and of 0.45  $m_0$  for holes. The Schottky barrier height ( $\phi_{SB}$ ) was set to 0.75 eV for both charge carriers, simulating a mid-gap Schottky contact. (**a**,**b**) Transfer characteristics of *p*- and *n*-type FET with top-gated geometry. The gate length is varied from 10 nm down to 4 nm. (**c**,**d**) Transfer characteristics of *p*- and *n*-type FET with double-gated geometry. The gate length is varied from 10 nm down to 4 nm.

$(L_{OPEN})$ , separating PG and CG, to  $L_{CG}/2$ , as shown in Fig. 2. Thus, in the remainder of the article, we will refer to  $L_{G}$  as the length of each gated segment. The program gates are placed in close proximity to source and drain contact (an underlap of 0 nm is used in all simulations) in order to provide the most efficient modulation of the Schottky barrier. For each simulated transfer characteristic, the value of the voltage applied to the program gate  $(V_{PG})$  was fixed, thus setting the device polarity, and the switching properties as a function of the control gate voltage ( $V_{CG}$ ) were studied.

#### **Results and Discussion**

The operation principle of the device is shown in Fig. 3 with the help of the band-diagrams extracted from the simulations on monolayer (1 L) WSe<sub>2</sub> at L<sub>G</sub> = 8 nm. The PG controls the device polarity by tuning the effective Schottky barriers height ( $\phi_{SB}$ ) at source and drain (*n*-type behavior at V<sub>PG</sub> = 1 V in Fig. 3a and *p*-type behavior at V<sub>PG</sub> = -1 V in Fig. 3b) while the control gate (CG) determines the ON/OFF state of the FET by controlling the

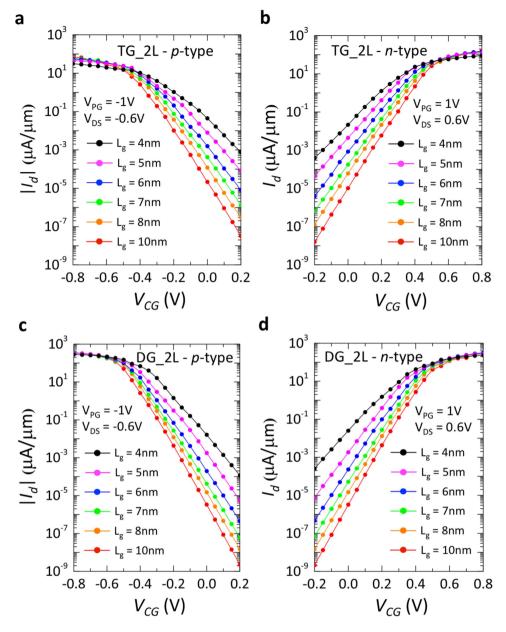

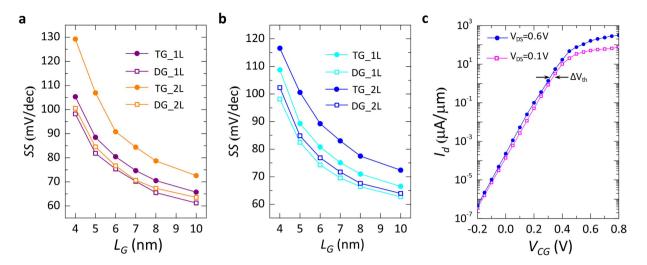

**Figure 5.** Simulated transfer characteristics for bilayer-WSe<sub>2</sub> polarity-controllable FETs. 2L-WSe<sub>2</sub> was modeled with 1.1 eV bandgap and the hopping parameters of the effective mass Hamiltonian were calculated using an effective mass ( $m_e$ ) of  $0.33 m_0$  for electrons and of  $0.45 m_0$  for holes. An interlayer hopping parameter was added to the Hamiltonian to account for interlayer coupling. The Schottky-barrier height ( $\phi_{SB}$ ) was set to 0.55 eV for both charge carriers, simulating a mid-gap Schottky contact. (**a,b**) Transfer characteristics of *p*- and *n*-type FET with top-gated geometry. The gate length is varied from 10 nm down to 4 nm. (**c,d**) Transfer characteristics of *p*- and *n*-type FET with double-gated geometry. The gate length is varied from 10 nm down to 4 nm.

potential barrier in the central region of the channel. Our simulation results show that the polarity of the device can be controlled at ultra-scaled dimensions, down to 4 nm gate lengths, when direct tunneling through the CG potential barrier begins to considerably degrade the device OFF-state.

Figure 4 shows the simulated *p*- and *n*-type transfer characteristics for 1L-WSe<sub>2</sub> channel, with TG (Fig. 4(a,b)) and DG (Fig. 4(c,d)) geometry. The gate length is varied to show the impact of scaling on the device characteristics. It is found that 1L-WSe<sub>2</sub> provides excellent control of the device OFF-state, thanks to the high bandgap  $(\sim 1.5 \text{ eV})^{30}$ , but also severely limits the ON-current of the device due to the high Schottky barrier ( $\phi_{SB} = 0.75 \text{ eV}$ ) present at source, where carriers are injected in the channel. The modulation induced by the PG at ±1 V is enough to show conduction of charge carriers, but the ON-currents only reach values of a few  $\mu A/\mu m$  for DG geometry.

Therefore, to increase the ON current of the devices, bilayer (2 L) WSe<sub>2</sub> was studied as a channel material. In its bilayer form WSe<sub>2</sub> shows a reduced bandgap of  $\sim$ 1.1 eV<sup>31</sup>, which together with the increased mobile charge

density, provided by the additional layer, is predicted to improve the device ON-state. Figure 5 shows the simulated transfer characteristics of 2L-WSe<sub>2</sub> FETs for both polarities and gate geometries, at different gate lengths.

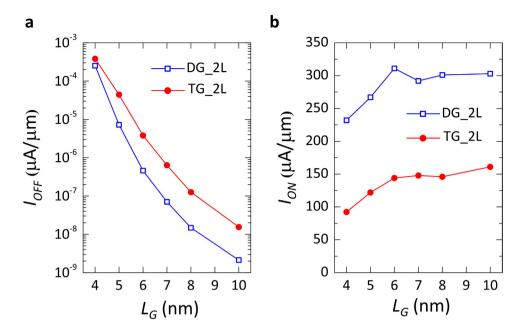

As a result of the decrease in Schottky-barrier height at the contact interface ( $\phi_{SB} = 0.55 \text{ eV}$ ), the ON-currents are increased by 2 orders of magnitude. With the lowering of the semiconducting bandgap, the potential barrier created by the CG in the OFF-state of the device is also decreased, deteriorating the device OFF-current. The I<sub>OFF</sub> is increased by almost 3 orders of magnitude. Nevertheless, the transfer characteristics presented in Fig. 5, show that even at the shortest gate length simulated ( $L_G = 4 \text{ nm}$ ),  $I_{OFF}$  is still on the range of  $10^{-4} \mu A/\mu m$ , providing  $I_{ON}/I_{OFF} > 10^6$ . The use of a DG geometry benefits the electrostatic control of the gates over the channel, and eliminates the charge screening effect between the layers that occurs in the TG structure. The improvement in the device electrostatics, given by the DG configuration, is shown in Fig. 6 where the  $I_{OFF}$  and  $I_{ON}$  (Fig. 6(a,b) respectively), extracted from the transfer characteristics of *n*-type devices with TG and DG structures, are compared. It is found that, until  $L_G = 5 \text{ nm}$ , the OFF-current in the DG configuration is consistently 1 order of magnitude lower with respect to the TG geometry, while the ON-current shows an average  $2 \times$  improvement. For  $L_G = 4 \text{ nm}$ , the potential barrier created by the CG starts to become thin enough to have tunneling effects, deteriorating the OFF-state of the device and thus lowering the positive impact of the double-gate. Similar results can be found for the *p*-type characteristics simulated on the same device.

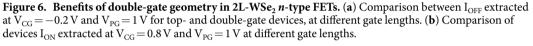

Further analysis is presented in Fig. 7, where the effect of scaling on the sub-threshold slope (SS) and on the drain-induced barrier lowering (DIBL) is analysed. The SS is evaluated as the average slope of the transfer characteristics in the sub-threshold regime (from -0.2 to  $0.2 V_{CG}$ ) for both *p*- and *n*-type operation mode (Fig. 7(a,b) respectively). For both polarities, it is shown that the SS greatly benefits from the double-gate geometry, which is able to mitigate the detrimental effect of increased channel thickness for the bilayer device. The DIBL is calculated as the variation of threshold voltage (V<sub>th</sub>) of the device divided by the variation of applied V<sub>DS</sub> (DIBL =  $\Delta V_{th}/\Delta V_{DS}$ ) and is expressed in mV/V. A threshold voltage shift of ~25 mV can be estimated as the lateral shift, at the end of the subthreshold regime, between the transfer characteristic simulated at  $V_{DS} = 0.1 V$  and 0.6 V (see Fig. 7c). Thus we computed a DIBL of 50 mV/V for L<sub>G</sub> = 6 nm, showing excellent immunity to DIBL effects. The observed immunity to DIBL is an added benefit of the SB polarity-controllable FETs, as the drain voltage drop in the channel is concentrated at the Schottky junction at drain. The change in V<sub>DS</sub> does not affect the height of the potential barrier created by the CG, which is ultimately responsible for the lowering of the threshold voltage of the device.

These analyses showed that the double-gate geometry provides the best electrostatic control and enhances the performances of the device by lowering the  $I_{OFFP}$  while improving the  $I_{ON}$  and SS. Nevertheless, the  $I_{ON}$  reachable with 2L-WSe<sub>2</sub>, in both *n*- and *p*-type operation mode, are still too low to provide a successful scaling path with this material. The Schottky barriers at source and drain ( $\phi_{SB} = 0.55 \text{ eV}$ ) are too high to have efficient tunneling at the contact interface. However, theoretical calculations<sup>32–34</sup> have shown that in the family of 2D-TMDCs, several materials, such as ZrS<sub>2</sub>, HfS<sub>2</sub>, etc., have a lower semiconducting band-gap (0.7–0.9 eV) and could prove to be well suited for application in SB-DIG FETs. For many of these materials experimental evidences are still absent or very limited<sup>35–39</sup>, and even in the theoretical ab-initio calculations there are discrepancies in the computed material properties<sup>32–34</sup> (with great variations). Based on these theoretical analyses, we modeled a 2D-material, according to the properties presented in Table 1, and studied its potential application as a semiconducting channel

**Figure 7.** Evaluation of sub-threshold slope and DIBL. (a) Sub-threshold slope extracted from the transfer characteristics of *p*-type devices, for both mono- and bi-layer WSe<sub>2</sub>. (b) Sub-threshold slope for *n*-type devices. It is shown that for both polarities, the use of the double-gate geometry benefits the sub-threshold behavior by reducing the SS. (c) DIBL evaluation at  $L_G = 6 \text{ nm}$  for DG *n*-type device. A  $V_{th}$  shift ( $\Delta V_{th}$ ) of approximately 25 mV is present, leading to a DIBL of ~50 mV/V.

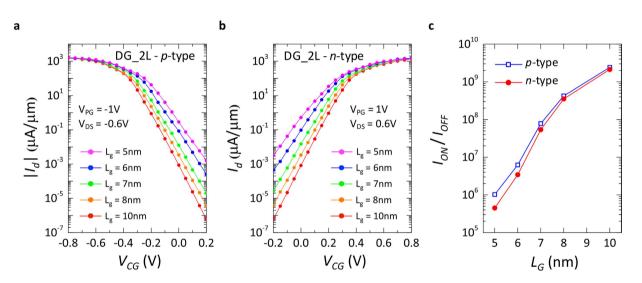

Figure 8. Analysis of performances for double-gate polarity-controllable device with 2L-MX<sub>2</sub> material. The improved MX<sub>2</sub> material was modeled with 0.8 eV bandgap, which results in a Schottky-barrier height ( $\phi_{SB}$ ) of 0.4 eV. The effective masses used were m<sub>e</sub> = 0.3 and m<sub>h</sub> = 0.4. (a) Transfer characteristics for *p*-type behavior, with L<sub>G</sub> varied from 10 nm down to 5 nm. (b) Transfer characteristics for *n*-type behavior, with L<sub>G</sub> varied from 10 nm down to 5 nm. (c) I<sub>ON</sub>/I<sub>OFF</sub> for both *p*- and *n*-type behavior. In both cases, I<sub>ON</sub>/I<sub>OFF</sub> > 10<sup>5</sup> is shown down to L<sub>G</sub> = 5 nm.

in polarity-controllable FETs. We considered a 2L-MX<sub>2</sub> material with an increased lattice constant, a lower bandgap and similar effective masses with respect to WSe<sub>2</sub> (as it is predicted for ZrS<sub>2</sub>, HfS<sub>2</sub>, HfSe<sub>2</sub>). Figure 8(a,b) shows the transfer characteristics at different L<sub>G</sub> for a DG geometry for both *p*- and *n*-type polarities, while the device performances in terms of I<sub>ON</sub>/I<sub>OFF</sub> ratios are presented in Fig. 8c. The lower Schottky-barrier height at source and drain ( $\phi_{SB} = 0.4 \text{ eV}$ ) allow for a greater number of carriers to be injected in the channel, increasing the I<sub>ON</sub> to ~1.5 mA/µm, while keeping I<sub>OFF</sub> well below 10<sup>-2</sup>µA/µm down to L<sub>G</sub> = 5 nm. The lower I<sub>ON</sub>/I<sub>OFF</sub> ratios for *n*-type behaviour shown in Fig. 8c, are caused by the lower effective mass of electrons, which increases the transmission probability of carriers over the potential barrier created by the CG, thus increasing the I<sub>OFF</sub>.

#### Conclusions

We evaluated scaling trends and device performances for 2D polarity-controllable FETs using self-consistent ballistic quantum-transport simulations. The device concept presents the great advantage of using only a single 2D channel material for both device polarities and does not require complex doping techniques. We showed the feasibility of controllable-polarity behaviour at the nanoscale level thanks to the additional program gate

introduced in the device geometry. We first simulated the performances of mono- and bi-layer WSe<sub>2</sub>, as a channel material, and found that the high semiconducting band-gap (~1.5 eV and 1.1 eV respectively) prevents achieving high ON-currents. Thus we studied the benefits of bilayer-MX<sub>2</sub> materials, such as ZrSe<sub>2</sub>, HfS<sub>2</sub>, or HfSe<sub>2</sub>, for which ab-initio simulations have shown the presence of a lower semiconducting bandgap (0.7–0.9 eV). Due to the lack of experimental characterization and the disagreement between different ab-initio simulations, we modeled a bilayer-MX<sub>2</sub> with electrical properties (effective masses and bandgap) within the values reported in literature<sup>32–34</sup>. For the simulated MX<sub>2</sub> material, we showed I<sub>ON</sub> > 10<sup>3</sup>  $\mu$ A/ $\mu$ m and I<sub>ON</sub>/I<sub>OFF</sub> > 10<sup>5</sup> down to L<sub>G</sub> = 5 nm for both *p*-and *n*-type polarities. These performances are comparable with the ones predicted, using ballistic self-consistent transport simulations<sup>7,8</sup>, for conventional doped devices based on 2D-TMDCs, and thus show a feasible scaling path for 2-dimensional polarity-controllable devices for beyond-CMOS flatronics.

#### Methods

**Material properties and Device simulations.** To perform quantum simulations within NEGF formalism, we use a 2-band tight-binding Hamiltonian to model the conduction and valence band of a chosen material<sup>40</sup>. We calculated the hopping parameter  $t_{hop}$ , to be used by the NanoTCAD ViDES<sup>28,29</sup> in the NEGF simulations, as<sup>40</sup>:

$$\left|t_{hop}\right|^2 = \frac{2\hbar E_G}{3a^2 m_p^*}$$

where *a* is the lattice constant,  $E_G$  is the energy band-gap,  $m_R^*$  is the reduced effective mass and  $\hbar$  is the reduced Plank constant. Here, the material parameters such as lattice constant, effective masses and band-gaps are taken from literature<sup>30-34</sup> and reported in Table 1. This approach has been widely used to project performance of nano-scale transistors based on Si, III-V<sup>41</sup> and now 2D materials<sup>11-14</sup>. Further, to model Schottky contacts, we extend our Hamiltonian at the contacts for the zero-bandgap metal and applied Dirichlet boundary conditions. This model provides a good trade-off between accuracy and computational time which is crucial in advanced device design with exotic materials for future technology nodes.

#### References

- 1. Nikonov, D. E. & Young, I. A. Overview of beyond-CMOS devices and a uniform methodology for their benchmarking. *Proceedings* of the IEEE 101(12), 2498–2533 (2013).

- 2. Ferrari, A. C. *et al.* Science and technology roadmap for graphene, related two-dimensional crystals, and hybrid systems. *Nanoscale* 7, 4598–4810 (2015).

- Wilson, J. A. & Yoffe, A. D. The transition metal dichalcogenides: discussion and interpretation of the observed optical, electrical and structural properties. Adv. in Phys. 18, 193–335 (1969).

- 4. Wang, Q. H., Kalantar-Zadeh, K., Kis, A., Coleman, J. N. & Strano, M. S. Electronics and optoelectronics of two-dimensional transition metal dichalcogenides. *Nature Nanotech*. 7, 699–712 (2012).

- Jariwala, D., Sangwan, V. K., Lauhon, L. J., Marks, T. J. & Hersam, M. C. Emerging device applications for semiconducting twodimensional transition metal dichalcogenides. ACS Nano 8, 1102–1120 (2014).

- Radisavljevic, B., Radenovic, A., Brivio, J., Giacometti, V. & Kis, A. Single-layer MoS<sub>2</sub> transistors. Nature Nanotech. 6, 147–150 (2011).

- 7. Wang, H. et al. Integrated circuits based on bilayer MoS<sub>2</sub> transistors. Nano Lett. 12, 4674-4680 (2012).

- Yu, L. et al. High-performance WSe<sub>2</sub> complementary metal oxide semiconductor technology and integrated circuits. Nano lett. 15, 4928–4934 (2015).

- 9. Tosun, M. et al. High-gain inverters based on WSe2 complementary field-effect transistors. ACS nano 8(5), 4948-4953 (2014).

- 10. Fiori, G. et al. Electronics based on two-dimensional materials. Nat. Nanotech. 9, 768–779 (2014).

- Cao, W., Kang, J., Sarkar, D., Liu, W. & Banerjee, K. 2D semiconductor FETs—Projections and design for sub-10 nm VLSI. *IEEE Transactions on Electron Devices* 62, 3459–3469 (2015).

- 12. Mishra, V. et al. Dependence of intrinsic performance of transition metal dichalcogenide transistors on materials and number of layers at the 5 nm channel-length limit. IEEE IEDM (2013).

- 13. Yoon, Y., Ganapathi, K. & Salahuddin, S. How good can monolayer MoS<sub>2</sub> transistors be?. Nano Lett. 11, 3768–3773 (2011).

- 14. Liu, L. *et al.* Performance limits of monolayer transition metal dichalcogenide transistors. *IEEE Trans. Elect. Dev.* **58(9)**, 3042–3047 (2011).

- 15. Kang, K. *et al.* High-mobility three-atom-thick semiconducting films with wafer-scale homogeneity. *Nature* **520(7549)**, 656–660 (2015).

- 16. Desai, S. B. et al. MoS<sub>2</sub> transistors with 1-nanometer gate lengths. Science **354**, 99–102 (2016).

- 17. Nourbakhsh, A. et al. MoS<sub>2</sub> Field-Effect Transistor with Sub-10 nm Channel Length. Nano Lett. 16, 7798–7806 (2016).

- Li, K.-S. et al. MoS<sub>2</sub> U-shape MOSFET with 10 nm channel length and poly-Si source/drain serving as seed for full wafer CVD MoS<sub>2</sub> availability. VLSI Technology, 2016 IEEE Symposium on. IEEE (2016).

- 19. Zhang, Y., Ye, J., Matsuhashi, Y. & Iwasa, Y. Ambipolar MoS<sub>2</sub> thin flake transistors. Nano Lett. 12(3), 1136-1140 (2012).

- 20. Bao, W. et al. High mobility ambipolar MoS<sub>2</sub> field-effect transistors: Substrate and dielectric effects. Appl. Phys. Lett. **102**, 042104 (2013).

- 21. Pradhan, N. R. et al. Hall and field-effect mobilities in few layered p-WSe2 field-effect transistors. Sci. Rep. 5, 8979 (2015).

- 22. Das, S. & Appenzeller, J. WSe<sub>2</sub> field effect transistors with enhanced ambipolar characteristics. *Appl. Phys. Lett.* **103**, 103501 (2013).

- 23. Resta, G. V. *et al.* Polarity control in WSe<sub>2</sub> double-gate transistors. *Sci. Rep.* 6 (2016).

- Gaillardon, P.-E. et al. Advanced system on a chip design based on controllable-polarity FETs. IEEE DATE'14 (2014).

Szabó, A. et al. Ab initio simulation of single-and few-layer MoS<sub>2</sub> transistors: Effect of electron-phonon scattering. Phys. Rev. B

- 92(3), 035435 (2015).

26. Li, Y., Hwang, C. H. & Li, T. Y. (2009). Random-dopant-induced variability in nano-CMOS devices and digital circuits. *IEEE Trans.*

- Elect. Dev. 56(8), 1588–1597 (2009).

27. Fiori, G. et al. Performance analysis of graphene bilayer transistors through tight-binding simulations. IEEE IWCE'09 (2009).

- 28. *NanoTCAD ViDES*, available online at: http://vides.nanotcad.com.

- 29. Fiori, G. & Iannaccone, G. Multiscale Modeling for Graphene-Based Nanoscale Transistors *Proceedings Of The IEEE* Vol. 101, p. 1653–1669 (2013).

- 30. Cao, W. et al. 2D electronics: Graphene and beyond. 43rd European Solid-State Device Research Conference (ESSDERC) 37-44 (2013).

- 31. Zhao, W. et al. Origin of indirect optical transitions in few-layer MoS<sub>2</sub>, WS<sub>2</sub>, and WSe<sub>2</sub>. Nano Lett. 13(11), 5627–5634 (2013).

- 32. Gong, C. et al. Band alignment of two-dimensional transition metal dichalcogenides: Application in tunnel field effect transistors. Appl. Phys. Lett. 103(5), 053513 (2013).

- Rasmussen, F. A. & Thygesen, K. S. Computational 2D materials database: Electronic structure of transition-metal dichalcogenides and oxides. *The Journal of Physical Chemistry C* 119(23), 13169–13183 (2015).

- 34. Zhang, W. *et al.* Two-dimensional semiconductors with possible high room temperature mobility. *Nano Research* **7(12)**, 1731–1737 (2014).

- 35. Li, L. *et al.* Electrical Transport and High-Performance Photoconductivity in Individual ZrS<sub>2</sub> Nanobelts. *Adv. Mat.* **22(37)**, 4151–4156 (2010).

- 36. Wang, X. et al. Large scale ZrS2 atomically thin layers. The Journal of Materials Chemistry C 4(15), 3143-3148 (2016).

- Kang, M. et al. Electrical characterization of multilayer HfSe<sub>2</sub> field-effect transistors on SiO<sub>2</sub> substrate. Appl. Phys. Lett. 106(14), 143108 (2015).

- 38. Xu, K. et al. Ultrasensitive Phototransistors Based on Few-Layered HfS2. Adv. Mat. 27(47), 7881-7887 (2015).

- 39. Kanazawa, T. et al. Few-layer HfS2 transistors. Sci. rep. 6 (2016).

- 40. Agarwal, T. et al. Effect of material parameters on two-dimensional materials based TFETs: An energy-delay perspective. 46th European Solid-State Device Research Conference, ESSDERC (2016).

- 41. Park, S. H. *et al.* Performance comparisons of III-V and strained-Si in planar FETs and nonplanar FinFETs at ultrashort gate length (12 nm). *IEEE Transactions on Electron Devices* **59(8)**, 2107–2114 (2012).

#### Acknowledgements

We acknowledge support from NSF (grant 1644592) and by IMEC core partners CMOS program.

### Author Contributions

G.V.R. performed the NEGF device simulations with contributions from T.A. in the definition of the material properties. D.L., I.P.R, F.C., P.-E.G. and G.D.M. helped interpreting the simulation results. G.V.R. wrote the manuscript with contributions from all authors.

#### Additional Information

Competing Interests: The authors declare no competing financial interests.

How to cite this article: Resta, G. V. *et al.* Scaling trends and performance evaluation of 2-dimensional polarity-controllable FETs. *Sci. Rep.* 7, 45556; doi: 10.1038/srep45556 (2017).

**Publisher's note:** Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

This work is licensed under a Creative Commons Attribution 4.0 International License. The images or other third party material in this article are included in the article's Creative Commons license, unless indicated otherwise in the credit line; if the material is not included under the Creative Commons license, users will need to obtain permission from the license holder to reproduce the material. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/

© The Author(s) 2017