# Polysilicon Nanowire Transistors and Arrays Fabricated With the Multispacer Technique

M. Haykel Ben Jamaa, *Member, IEEE*, Gianfranco Cerofolini, Giovanni De Micheli, *Fellow, IEEE*, and Yusuf Leblebici, *Senior Member, IEEE*

Abstract—In this paper, we demonstrate the ability of the multispacer patterning technique to yield layers of polycrystalline silicon nanowires with a sublithographic pitch, by exclusively using micrometer resolution andCMOS processing steps. We characterize single spacers operating as poly-Si nanowire field effect transistors . We demonstrate also the possibility to lay a spacer perpendicularly to a set of parallel spacers in a crossbar fashion. The extrapolated cross-point density from the small 4 × 1-array is in the range of  $10^{10}$  cm<sup>-2</sup>. We discuss the applications of this technique to improve the density of previously reported poly-SiNW memories and as a future framework for nanowire crossbars and decoders. Then we analyze the limitations and costs of the proposed technique.

*Index Terms*—Crossbar circuits, decoder design, memory, silicon nanowires, spacer technique.

# I. INTRODUCTION

**S** ILICON nanowires (SiNW) are promising candidates for continuing the scaling of CMOS technology. The increasing costs of photolithography motivates the development of lithography-independent nanowire (NW) fabrication processes. These techniques can be divided into bottom-up approaches based on SiNW growth from a catalyst [1] and top-down approaches based on the accurate control of etching and oxidation of Si [2] and deposition of poly-Si [3], [4] (for SiNW and poly-SiNW, respectively).

Even though NWs with subphotolithographic width below 10 nm have been demonstrated, their pitch, which is the sum of their width and spacing, is generally defined by photolithography. The pitch, which is the spacing between two successive NWs in the layer, is more representative of the NW density. Thus, it is highly desirable to develop techniques yielding a photolithography-independent NW pitch in order to increase the overall integration density.

Manuscript received August 19, 2009; revised February 17, 2010 and August 24, 2010; accepted September 6, 2010. Date of publication October 21, 2010; date of current version July 8, 2011. This work was supported in part by the CCMX/MMNS project, in part by the Centre des Systèmes Intégrés Center, and in part by the Swiss Fond National Suisse Research under Grant 200021-109450/1. The review of this paper was arranged by Associate Editor L. Wernersson.

M. H. B. Jamaa is with Commissariat à l'Energie Atomique et aux Energies Alternatives (CEA-LETI), Grenoble 38054, France (e-mail: haykel.ben\_jamaa@a3.epfl.ch).

G. Cerofolini is with the Department of Material Sciences, University of Milano–Bicocca, Milan 20125, Italy (e-mail: gianfranco.cerofolini@mater. unimib.it).

G. De Micheli and Y. Leblebici are with Microelectronic Systems Laboratory, École Polytechnique Fédérale de Lausanne (EPFL), Lausanne 1015, Switzerland (e-mail: giovanni.demicheli@epfl.ch; yusuf.leblebici@epfl.ch).

Color versions of one or more of the figures in this paper are available online

at http://ieeexplore.ieee.org. Digital Object Identifier 10.1109/TNANO.2010.2089532 The paradigm of arranging arrays of parallel NWs perpendicular to each other in a crossbar fashion received the attention of many research groups. The dense crossbars can perform logic or store information at the cross-points, which contain bistable molecules or phase-change materials [5], [6]. To access every NW in the crossbar from the outer CMOS circuit, the utilization of a decoder consisting of a set of access devices operating as SiNW FETs was suggested [7], [8].

The purpose of this paper is to investigate the possibilities offered by the multispacer patterning technique (MSPT) in terms of structural and electrical properties of the fabricated sublithographic structures, to assess the opportunity of arranging them into crossbar arrays and to address the challenges and limitations of the proposed technique.

This paper is organized as follows. Section II surveys the background and previous study related to the spacer technology and introduces the baseline organization of crossbar circuits that can be fabricated with this technology. Section III introduces the fabrication process, and Section IV presents the obtained results including a structural and an electrical characterization of the fabricated structures. Section V explains possible applications of the presented technique, and Section VI discusses its challenges related to the technology and the circuit architecture. The conclusion is given in Section VII.

# II. BACKGROUND AND RELATED WORK

In the following, previously reported study with the spacer technology is surveyed. The interest in applying this technology to NW crossbar circuits is then motivated and the overall architecture of crossbars is explained.

## A. Spacer Technology

The spacer technique has been suggested as a possible fabrication process that yields parallel NWs. In general, NW fabrication techniques can be divided into bottom-up and top-down approaches. Bottom-up techniques are based on the growth of NWs on a silicon substrate from catalyst seeds. The as-grown NWs are then collected in a solution and dispersed on the top of the substrate to be functionalized [9], [10]. In top-down approaches, NWs are directly defined on the functional substrate by accurately controlling the deposition, oxidation, and etching rates [4], [11], or by using nanometer-scale molds whose pattern can be transferred onto another substrate using the nanomold imprint lithography [12].

With the spacer technique, it is possible to control device dimensions below the photolithographic limit [13], [14] yielding

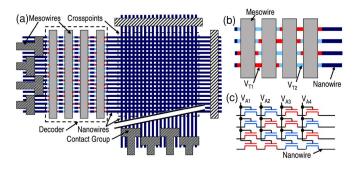

Fig. 1. Baseline architecture of (a) crossbar circuit and highlights of (b) decoder layout and (c) circuit.

sublithographic NWs with a top-down approach. The approach is based on the definition of a spacer by conformally depositing a material at the edge of a sacrificial layer and then anisotropically etching it. The width of the spacer depends on the thickness of the deposited material, which can be controlled accurately, often on the scale length below 1 nm, without any dependence on the photolithographic dimensions. By removing the sacrificial layer, the spacer can be used as a hard mask to define structures in the underlying layers. The spacer technique has been applied in order to fabricate fin field effect transistors (Fin FETs) with shorter gate length and higher performance than lithographically defined MOS FETs [15]–[18]. Devices made with the spacer technique have been deployed in other fields as well, such as optical applications [19], high-frequency transistors [20] and biosensing [21].

The spacer patterning process is maskless and self-aligned, which makes it a very attractive way to shrink dimensions. However, it necessitates additional deposition and etch steps. Interestingly, the spacer patterning can be iterated several times, resulting in the multispacer patterning technique. For instance, every spacer can be used as a sacrificial layer for the following spacer. This iterative approach, called the multiplicative road [22], is a possible way to reduce the lithographic pitch by a factor of  $2^n$ , with n the number of iterations [13], [21]. Another approach based on the iterative definition of successive spacers by alternating semiconducting (poly-Si) and insulting materials  $(SiO_2)$  defined on the edge of the same sacrificial layer [4], is a second way to obtain layers of NWs with a sublithographic pitch, and it is called the additive road [22]. Either approaches have been used in order to define dense NW molds. The pattern of such nanomolds is subsequently transferred onto a different substrate by nanomold imprint lithography in order to define layers of micrometer long and parallel NWs [21], [23].

# B. Baseline Circuit Architecture

The increasing interest in fabricating dense layers of parallel NWs with a sublithographic pitch is motivated by the emergence of the NW crossbar paradigm as a possible architecture for post-CMOS technologies [24]–[26]. The baseline organization of a NW crossbar circuit is depicted in Fig. 1(a). An arrangement of two orthogonal layers of parallel NWs defines a regular grid of intersections called cross-points. Phase-change materials or

molecular switches can fill the separation between the two layers at the cross-points; thus, performing information storage, interconnection or computation at these cross-points [27], [28]. A set of contact groups is defined on top of the NWs. Every contact group has an ohmic contact to a corresponding set of NWs that represents the smallest set of NWs that can be contacted by the lithographically defined lines (mesowires).

Every set of NWs within a contact group is connected to the outer CMOS circuit through the mesowires. A decoder is utilized in order to make every NW within this set uniquely addressable by the outer circuit. It is formed by a series of transistors along the NW body, controlled by the mesowires and having different threshold voltages [29], as shown in Fig. 1(b) and (c). Depending on the distributions of threshold voltages of the series transistors along the NWs and on the sequence of applied voltages in the decoder ( $V_A$ 's), one single NW in the array can be made conductive, which is required for a correct addressing operation.

Many decoders have been suggested for NW arrays. Their design strongly depends on the NW fabrication technology. Axial and radial decoders are proposed for NWs fabricated with a bottom-up approach [30], [31] and they are based on the random dispersion of NWs whose pattern is defined by *in situ* doping. Mask-based decoders [8] are proposed for NWs fabricated with a top-down approach, whose pattern is deterministically defined by using a conventional mask. Random-contact decoders [32] are an alternative approach for top-down NWs, whereby the NW pattern is defined through stochastic contacts. For other bottom-up techniques with a large pitch, a gate-all-around decoder is suggested in [11]. A conceptual approach to fabricate and designing a specific decoder with the spacer technique is presented in [33].

# C. Spacer-Based NW Crossbars

Given the ability of the MSPT to yield parallel NWs, it is therefore interesting to investigate the opportunities of fabricating crossbar circuits with the MSPT. As a matter of fact, despite the additional deposition and etch step, this maskless and selfaligned technique offers an interesting alternative approach to high-resolution lithography (electron beam or ultraviolet lithography), which are slow or/and expensive; and to nanoimprint lithography, which may require special measures to align the nanomold to wafers. Poly-Si spacers can be deposited at 600 °C– 700 °C. Consequently, the integration of crossbars into a CMOS process can be carried out between front- and back-end process steps. Once the metallization is finished, the molecular switches are dispersed onto the wafer, and they attach to the cross-points with self-assembly [34].

However, when the suitability of a technology for crossbar circuits is evaluated, there are two important parts of the circuit to be considered separately: the crossbar and the decoder.

When it comes to the fabrication of crossbars with the MSPT, i.e., crossing NWs, to the best of our knowledge, we notice that only parallel spacers have been demonstrated with the MSPT and used as stand-alone NWs [22] or as nanomold to pattern different substrates [21]. Crossing NWs have not been

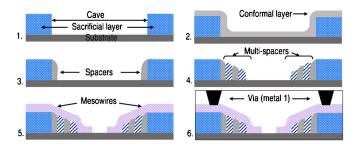

Fig. 2. Main process steps. (1) Definition of sacrificial layers. (2) Conformal deposition of poly-Si. (3) RIE etch. (4) Alternation of poly-Si/SiO<sub>2</sub> spacers. (5) Definition of the gate stack. (6) Passivation and metallization.

demonstrated with the MSPT yet. In this paper, this opportunity is investigated and crossing NWs based on the MSPT are demonstrated. This step is key in achieving the ultimate goal of full crossbar design with the MSPT.

The decoder is a critical part of the circuit, since it bridges the crossbar and the rest of the CMOS circuit. From previously demonstrated or suggested techniques [8], [11], [30]–[33], it has been shown that the decoder fabrication and design techniques highly depend on the existing NW technology. The yield, measured in this context simply as the percentage of NWs that can be addressed, can be low if the technology allows only a stochastic decoder design [30], [32]. On the other hand, the decoder size, measured as the number of mesowires needed in order to address a given number of NWs, may have a considerable overhead depending on the technology. The iterative aspect of the MSPT can be efficiently utilized in order to design a decoder with a compact size [33]. The benefits of the MSPT in designing the decoder is addressed in this paper and the compactness of the decoder compared to other existing approaches is highlighted.

This paper addresses the utilization of the spacer technique for the fabrication of NW crossbars. Unlike previous approaches that used the MSPT to define simple layers of parallel NWs [4], [13], [20], and those that used the MSPT to define nanomolds to pattern NWs [19], [21], [23], this paper demonstrates for the first time 1) that not only layers of parallel NWs, but also dense NW crossbars can be fabricated with the MSPT, and 2) that MSPT-based crossbars can be obtained in a self-aligned and maskless process without the utilization of any nanomold. The scalability of the as-fabricated poly-Si crossbars is studied, and the characterization of the access devices operating as poly-SiNW FETs is performed for the first time.

## **III. FABRICATION PROCESS**

The fabrication process of a single NW layer is described in Fig. 2. The main idea of the process is the iterative definition of thin spacers with alternating semiconducting and insulating materials, which result in semiconducting and insulating NWs. We start by defining a  $1\mu$ m SiO<sub>2</sub> layer on a Boron-doped Si substrate (p-type, 0.1–0.5  $\Omega \cdot$  cm) with wet oxidation. Then, we define a sacrificial layer (step 1) with a height of 500 nm in the wet oxide. Then, we deposit a thin conformal layer of poly-Si with a thickness ranging from 40 to 90 nm by low-pressure chemical vapor deposition (LPCVD), where SiH<sub>4</sub> is

deposited at 600 °C (step 2). Subsequently, we etch this layer with a reactive ion etching (RIE) equipment using  $Cl_2$  plasma, in order to remove the horizontal layer while keeping the sidewall as a spacer (step 3); and we densify the poly-Si spacer at  $700 \,^{\circ}\text{C}$ for 1 h under N<sub>2</sub> flow. Then, we partially oxidize the poly-Si spacer at 900 °C under O<sub>2</sub> flow in order to obtain an insulating layer between the successive poly-Si spacers. Alternatively, we deposit a conformal insulating layer by using a 40–80 nm thin low-temperature oxide (LTO) obtained by LPCVD following the reaction of SiH<sub>4</sub> and O<sub>2</sub> at 425 °C. The deposited LTO is densified at 700  $^{\circ}$ C for 45 min under N<sub>2</sub> flow, then it is etched in a RIE etchant using C<sub>4</sub>F<sub>8</sub> plasma in order to remove the horizontal layer and just keep the vertical spacer. We perform these two operations (poly-Si and SiO<sub>2</sub> spacer definition) one to six times in order to obtain a multispacer with two to 12 alternating poly-Si and SiO<sub>2</sub> NWs (step 4).

In order to address the issue of realizing a crossbar framework, we fabricate the bottom multispacer as explained previously, then we grew 20-nm dry oxide as an insulator between the top and bottom NW layers. The top sacrificial layer is defined with LTO perpendicular to the direction of the bottom sacrificial layer. Then a poly-Si spacer is defined at the edge of the top sacrificial layer in a similar way to the bottom poly-Si spacers. Subsequently, the separation dry oxide and both sacrificial layers are removed in a buffered HF solution in order to visualize the crossing poly-Si spacers realizing a small poly-SiNW crossbar.

In another set of wafers, we address the issue of characterizing a single access device (poly-SiNW FET). In this case, we use a single NW layer with one 67-nm wide poly-SiNW, on top of which we define a gate stack with an oxide thickness of 20 nm and different gate lengths (step 5). The drain and source regions of the undoped poly-SiNW were defined by the electron-beam evaporation of 10-nm Cr and 50-nm nichrome  $Ni_{0.8}Cr_{0.2}$  (step 6). The use of Cr enhanced the adhesion and resistance of Ni to oxidation during the two-step annealing (5 min at 200 °C, then 5 min at 400 °C).

## IV. CHARACTERIZATION OF THE STRUCTURES

This section presents the fabricated devices with the previously introduced process flow. The scalability and ability of the process to yield crossing NWs are demonstrated, and the electrical characterization of access devices, operating as poly-SiNW FET, is reported.

## A. Structural Characterization

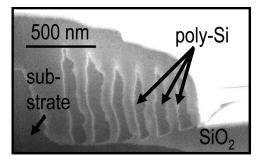

We first assessed the structural properties of arrays of parallel NWs fabricated with the proposed technique. Fig. 3 shows a sequence of six double spacers formed by poly-Si over SiO<sub>2</sub>. Every double spacer was obtained by poly-Si deposition, etch, and then partial dry oxidation at 900 °C. Despite the ability to repeat the spacer definition steps several times, the edge roughness was too high because of the utilization of poly-Si and the subsequent etch and oxidation steps. It is expected that the poly-Si grain size is approximately equal to the thickness of the deposited layer, i.e., about 80 nm in Fig. 3. The etch step increases the surface roughness. The subsequent high-temperature

Fig. 3. SEM image of a focused-ion-beam cross section of  $6 \times$  poly-Si/dry oxide double spacer.

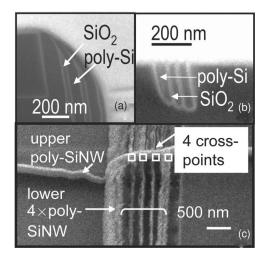

Fig. 4. SEM images of multispacers and a small crossbar. (a) Alternating 54-nm thin poly-Si and LTO spacers. (b) Scaling down to 20-nm thin poly-Si. (c) Small  $4 \times 1$  crossbar with one upper and four lower poly-Si spacers.

oxidation highly intensifies the edge roughness because the oxidation rate is not homogeneous close to the contact locations between neighboring poly-Si grains.

In order to reduce the vertical surface roughness of poly-Si spacers, we utilized LTO instead of the dry oxide. Fig. 4(a) shows a SEM image of three poly-SiNW separated by LTO NWs. All the poly-SiNWs have a uniform thickness of 54 nm, with an improved surface roughness. The height of the first poly-SiNW is about the height of the sacrificial layer and it has a rounded corner due to the conformal poly-Si deposition and the following etching procedure. The rounded corner effect is intensified with the increasing number of spacers resulting in a decrease of the poly-SiNW height with the number of NWs in the multispacer. A NW length of hundreds of micrometers could be achieved, with no NW interruption. Our technique has a high yield: in all samples characterized with SEM (over 100 samples on eight different wafers) no broken NWs have been seen. We also investigated the scalability of this technique by depositing thinner poly-Si layers (40 nm), Fig. 4(b) shows that the obtained poly-SiNW have a width of 20 nm. For the device in this SEM image, we planarized the multispacer after it was defined by chemical mechanical polishing (CMP) in order to remove the rounded corner effect reported in Fig. 4(a). CMP is, therefore, a possible way to remove the rounded corners

Fig. 5.  $I_{\rm ds}-V_{\rm gs}$  curve of an undoped single poly-SiNW with a back-gate and nichrome drain/source ( $L=20\mu{\rm m}$  and  $W=67{\rm nm}$ ).

if they are not desirable. The possible use of the MSPT for the fabrication of two perpendicular layers of crossing NWs is illustrated in Fig. 4(c) with one poly-SiNW crossing four poly-SiNWs underneath it. The first NW to the right is wider than the three others because it was defined with a thicker deposited poly-Si layer. Here again, the length of the NWs in the crossbar could be made as large as desired without any noticeable NW interruption.

# B. Electrical Characterization

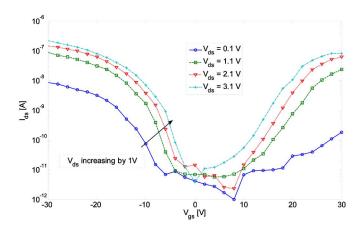

The need to access the NWs and control the current flow through them motivates for the definition of access transistors having a poly-Si spacer as a channel. We characterized undoped poly-SiNW FETs (single poly-Si spacer) with nichrome (Ni<sub>0.8</sub>Cr<sub>0.2</sub>) drain and source contacts and with a NW channel length  $L = 20 \ \mu m$  and a fin width  $W = 67 \ nm$ . We used a back gate formed by p-doped Si substrate (0.1–0.5  $\Omega \cdot cm$ ) and the thick back-gate oxide corresponds to the cave thickness ~0.4  $\mu m$ .

The  $I_{\rm ds}$ - $V_{\rm gs}$  curves show an ambipolar behavior, with a current conductance under either high positive or negative gate voltage (see Fig. 5). The type of metal to poly-Si contact plays a major role in the reported ambipolar behavior. Chromium present in metallic Cr alloys generally migrates to the surface when the alloy is heated. During the two-step annealing, the underlying Cr and the Cr in the nichrome alloy migrate to the metal-to-air surface and protect the contact from oxidation. This was experimentally checked by comparing the oxidation rate of a pure nickel contact to one of the contact used in the measured devices. During the annealing step, the poly-Si is, therefore, in direct contact to the almost pure Ni. At 400 °C, Ni reacts with Si to form a nickel silicide contact [35]. This contact can result in ambipolar devices [36]. The Schottky barrier for electrons with this kind of contact has been reported by some groups as high as 0.57 eV [37], while it is believed to be about 0.61 eV in bulk silicon [38].

In the measured structures, the  $I_{\rm on}/I_{\rm off}$  ratio was  $\sim 2 \times 10^4$ and  $\sim 4 \times 10^3$  for p- and n-branch, respectively. The low  $I_{\rm on} = 0.2 \,\mu\text{A}$  and  $0.1 \,\mu\text{A}$  for p- and n-branches is, respectively,

Fig. 6. Hysteresis of the  $I_{\rm ds}$ - $V_{\rm gs}$  curve shown in Fig. 5 for  $V_{\rm ds}$  = 3.1 V.

explained by the low W/L ratio (NW width W = 67 nm and gate length  $L = 20 \ \mu m$ ) and the low mobility in poly-Si. The Shottky barrier for holes (0.51 to 0.55 eV) may be slightly lower than for electrons (0.61 to 0.57 eV), which explains the higher  $I_{\rm on}$  current in the p-branch. During these measurements, the gate leakage for large positive and negative gate voltages was about two to three orders of magnitude lower than the drain current.

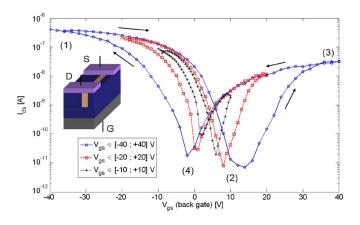

The  $I_{\rm ds}$ - $V_{\rm gs}$  curve showed a hysteretic behavior as depicted in Fig. 6, whereby the labels (1)–(4) indicate the direction of the hysteresis. By enlarging the  $V_{\rm gs}$  sweep range from [–10 V, 10 V] to [–40 V, 40 V], the hysteresis width became larger. This hysteretic behavior confirms the high density of trapped charges in the poly-Si grains and at the interface between the poly-Si channel and the gate oxide. The density of trapped charges depends on the applied field, explaining the dependence of the hysteresis width on the gate voltage range.

The ability to control the devices in a FET fashion proves their possible use as access devices to the NW layer within a decoder [33]. The ambipolarity is due to the intrinsic poly-Si and the midgap contact metal. By using implanted contact regions and metal contact, the unipolar behavior is expected to be achieved [35].

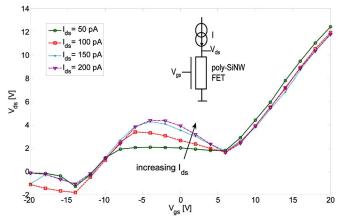

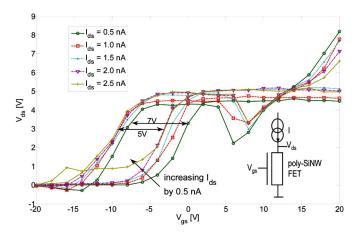

We also plotted the transfer characteristics  $V_{\rm ds}-V_{\rm gs}$  for a fixed  $I_{\rm ds}$  (see Fig. 7), which has a clear negative slope region. The same transfer characteristics have a hysteresis of 5–7 V, which decreases with increasing injected current  $I_{\rm ds}$  (see Fig. 8). The measured hysteresis is in agreement with the behavior of poly-SiNW reported in literature and it can be explored in single NW memories [3].

#### V. POTENTIAL APPLICATIONS

The reported results in the previous section have different application fields. This section explains the possible future utilization of the MSPT as a framework for NW crossbars, dense single NW memories and compact NW decoders.

#### A. Crossbar Framework

A promising application of SiNWs is the fabrication of crossbar structures, which can be functionalized in order to oper-

Fig. 7.  $V_{\rm ds}$ - $V_{\rm gs}$  transfer characteristics for fixed  $I_{\rm ds}$  bias of an undoped single poly-SiNW with a back gate and nichrome drain/source.

Fig. 8. Hysteresis of the  $V_{ds}$ - $V_{gs}$  transfer characteristic in Fig. 7.

ate as a memory or as a computational unit such as a programmable logic array (PLA) [25]. Previous approaches to build NW crossbars achieved either 1) metallic arrays, which do not have any semiconducting part that can be used as an access transistor, or 2) silicon-based crossbars with fluidic assembly, which have a larger pitch in average than the photolithography limit. Table I surveys the reported realized crossbars and shows that our technique has both advantages of yielding semiconducting NWs and a high cross-point density  $\sim 10^{10}$  cm<sup>-2</sup>, as measured in the small crossbar of Fig. 4(c), while using conventional photolithographic processing steps. The use of the densest layers [see Fig. 4(b)] would yield a higher cross-point density of  $\sim 6.3 \times 10^{10}$  cm<sup>-2</sup>.

The demonstrated crossbar framework shows only the NWs. However, a functional crossbar must be functionalized by inserting molecular switches or phase-change materials at the crosspoints in order to perform the function of the circuit: logic, memory, or interconnect. The design of molecular switches is beyond the scope of this paper: the underlying chemistry and the grafting mechanism of molecular switches to NWs were investigated in [34].

TABLE I

Survey of Reported NW Crossbars (Functionalization Means Usage of Molecular Switches)

| Reference                               | [12] | [39]                  | [5]               | [1]              | This work |

|-----------------------------------------|------|-----------------------|-------------------|------------------|-----------|

| NW material                             | Pt   | Ti/Si                 | Ti/Pt             | Si               | poly-Si   |

| NW thickness [nm]                       | 8    | 16                    | 30                | 20               | 54        |

| NW pitch [nm]                           | 16   | 33                    | 60                | >1000            | 100       |

| Cross-point density [cm <sup>-2</sup> ] | 1011 | $9.5 	imes 10^{10}$   | $2.7	imes10^{10}$ | low              | $10^{10}$ |

| NW technique                            | SNAP | SNAP                  | NIL               | Fluidic Assembly | MSPT      |

| Functionalization                       | Ø    | <ul> <li>✓</li> </ul> | ~                 | Ø                | Ø         |

Fig. 9. (a) Poly-SiNW memory cell after [3]. (b) Mapping of logic states onto hyteretic loops. (c) Memory operation principle. (d) Higher density realization concept of poly-SiNW memory cell with the MSPT.

## B. Single Poly-SiNW Memory

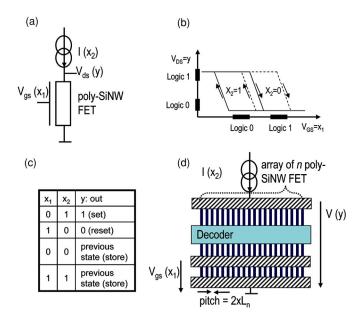

Besides the application as a crossbar array, there is a second conceptual application as poly-SiNW memory based on the hysteresis of the  $V_{ds}-V_{gs}$  transfer characteristic for a fixed  $I_{ds}$ . The idea comes from the demonstrated concept of a poly-SiNW memory cell in [3] and the memory operation was experimentally demonstrated in [3] using  $I_{ds}$  and  $V_{gs}$  as inputs and  $V_{ds}$ as output storing the information. A single poly-SiNW memory cell after [3] is illustrated in Fig. 9(a). For detailed description, the operation was reported in [3] and it is based on the choice of two adjacent  $V_{ds}-V_{gs}$  hysteresis loops corresponding to two distinct  $I_{ds}$  current levels for logic 0 and 1, respectively [see Fig. 9(b)]. The memory state is stored in the output variable  $V_{ds}(y)$ , and it can be set to 0 or 1 by applying the right sequence of input variables  $V_{gs}(x_1)$  and  $I_{ds}(x_2)$  as explained in [3]. A summery of the memory operation is given in Fig. 9(c).

This poly-SiNW memory cell proposed in [3] is based on a single NW. The half pitch separating two adjacent cells is equal to the lithographic half pitch in the best case. Given the fact that the MSPT yields lithography-*in*dependent NW pitch, it is possible to think of combining the MSPT with the idea of poly-SiNW memory cells proposed in [3], in order to reduce the distance between two adjacent cells below the lithographic half pitch. A conceptual scheme of the MSPT-based poly-SiNW memory

cells is depicted in Fig. 9(d). In this conceptual configuration, the pitch of the poly-SiNW is not limited by the lithography anymore, but it rather depends on the MSPT pitch, which can be below the lithography pitch. In order to control the NW corresponding to the cell to be addressed, a decoder is needed and it is included in the cell scheme. More details about the decoder fabrication and design for parallel NWs are presented in the following section.

### C. NW Decoder

Fabricating crossbars with a subphotolithographic pitch raises the question of how to make every NW addressed by the outer CMOS circuit through a decoder. The design of crossbar decoders has attracted a lot of attention and the proposed solutions are either analog [7] or digital. Among the digital decoders, there are stochastic [30]–[32] and deterministic approaches [8], [33].

A possible metrics that can be used to compare decoders is their size given by M, the required number of mesowires needed to address N NWs. Using NWs doped with different doses and the same type (either n or p), the minimal cost is given by  $M = 2 \cdot \lceil \log_2(N) \rceil$  [29]. The minimal cost is just the half of this values, when a complementary logic (using both n- and p-type) is used; however, for technological reasons, this is not expected to be the case for NW decoders [29]. The randomness of stochastic approaches [30]–[32] results in a large overhead in M. Even the deterministic approach in [8] needs a certain overhead due to the dimension mismatch between nano and mesowires. The cost M for these approaches is summarized in Table II.

We have proposed a concept of a deterministic digital decoder for MSPT-based crossbars in [33], which is expected to yield the lowest possible cost for M (see Table II). The multispacer patterning technique has the advantage of enabling the fabrication of a deterministic NW decoder with a minimal size M, which cannot be achieved with other techniques requiring a certain overhead for M. If the MSPT approach is applied for the decoder, then unipolar access transistors are needed, which requires the implantation of source and drain regions instead of using the proposed nichrome contact.

## VI. DISCUSSIONS

Despite the various potential applications of the MSPT, many aspects are challenging the fabrication and the organization of the crossbar circuits. This section explains these challenges and shows possible opportunities to address them.

| Reference        | [30]                                     | [31]                                     | [32]                                                 | [8]                                                  | [33]                                |  |

|------------------|------------------------------------------|------------------------------------------|------------------------------------------------------|------------------------------------------------------|-------------------------------------|--|

| NW technique     | Fluidic Assembly                         | Fluidic Assembly                         | Any Top-Down                                         | NIL/SNAP                                             | MSPT (this work)                    |  |

| NW decoder       | Axial Decoder                            | Radial Decoder                           | Random Contact Decoder                               | Mask-Based Decoder                                   | MSPT Decoder                        |  |

| Decoder type     | Stochastic                               | Stochastic                               | Stochastic                                           | Deterministic                                        | Deterministic                       |  |

| M (Decoder size) | $\lceil 2.2 \cdot \log_2(N) \rceil + 11$ | $\lceil 2.2 \cdot \log_2(N) \rceil + 11$ | $\lceil 4.8 \cdot \log_2(N) \rceil + \mathcal{O}(1)$ | $2.0 \cdot \lceil \log_2(N) \rceil + \mathcal{O}(1)$ | $2.0 \cdot \lceil \log_2(N) \rceil$ |  |

|                  | Caves                                    |                                          | time steps<br>batch 1<br>batch 2<br>batch <i>n</i>   |                                                      | <br><br>ch                          |  |

|                  | (a) Within-die pa                        | rallelization                            | (b) Batch parallelization                            |                                                      |                                     |  |

TABLE II SURVEY OF REPORTED DIGITAL NW DECODERS

Fig. 10. Parallelization of the MSPT. (a) Using many small caves instead of a few large ones minimizes the number of steps, but has a cost in terms of area (within-die parallelization). (b) Any two batches can be processed together during the spacer definition steps, as long as the spacer parameters are identical (batch parallelization).

# A. Process Limitations

The structural characterization reported in Section IV-A shows a high edge roughness due to the utilization of poly-Si. The edge roughness is intensified by the subsequent etch and eventually oxidation steps. The utilization of LTO instead of the dry oxide as a insulating layer between successive poly-Si spacers helped noticeably reduce the vertical edge roughness [Fig. 4(a) versus Fig. 3]. However, the topside of the poly-Si spacers still has a high roughness [see Fig. 4(c)], which requires a planarization of the structure with CMP following the definition of the whole multispacer [see Fig. 4(b)].

The scalability of the fabricated structures is limited by the ability to reduce and control the size of the deposited poly-Si grains in the range of a few tens of nanometer or less. If the ability to deposit thin (below 10 nm) and smooth poly-Si layers is limited, then the MSPT approach becomes less competitive with highly scaled photolithography-based NWs.

Despite the fact that the definition of the spacers is exclusively based on self-aligned steps, the orientation of the crossing spacer planes with respect to each other depends on the alignment of the masks used to define the sacrificial layers. Therefore, a special care has to be taken to accurately align these steps in order to insure that the crossing NWs are perpendicular to each other.

# B. Process Cost

One important question that may arise when it comes to the MSPT is the cost of the additional conformal deposition and RIE etch steps. The fabrication time needed for a  $256 \times 256$  NW crossbar (8 kB memory) would be tremendous if  $2 \times 256$  deposition/etch operations were required. Fortunately, the MSPT has two advantages: 1) it can be parallelized within a single wafer, i.e., by using n parallel sacrificial layers instead of one, the number of deposition/etch steps is divided by n [see Fig. 10(a)]; and 2) the technique allows for parallel batch processing, i.e., any two different batches can be processed together during the deposition/etch steps as long as the thickness of the conformal layers is the same [see Fig. 10(b)].

In general, within-die parallelization should be preferred in order to keep n as large as possible. The factor n is chosen such that the width of every cave is matched by the lithographic dimensions, making the number of NWs in every cave in the range  $\sim 3 \times L_l/L_n$ . The factor three comes from the symmetry of the caves and the possible need for some overhead in order to bridge the lithographic and sublithographic dimensions [29]. For instance, at the 65-nm technology node ( $L_1 = 65 \text{ nm}$ ) and with 20-nm wide NWs ( $L_n = 20 \text{ nm}$ ), n should be chosen such that every cave has  $\sim 10$  parallel NWs. Given the symmetry of the cave, the number of deposition/etch procedures is only five instead of 256. Then, for the full crossbar made of two layers, ten deposition/etch procedures are needed instead of 512.

# C. Circuit Architecture

Another important question about the proposed technique is related to the lower mobility of current carriers in the poly-Si used to define the structure, compared to crystalline Si. The question was generalized previously for any crossbar type: whatever the used NW material is, the structure length and small cross section will induce a slower signal propagation and higher resistance. To address this fact, it is generally believed [40] that the benefit of crossbars is to parallelize memory and computation in a grid with a large number of small crossbars, rather than using a limited number of large crossbars.

## VII. CONCLUSION

Many efforts are concentrated on the scaling of SiNWs, but fewer research studies offered solutions to scale the NW pitch with standard CMOS process steps in an independent way on the photolithography. We used the MSPT in order to fabricate dense and lithography-independent poly-SiNWs with standard CMOS steps and micrometer lithography resolution, achieving a very high yield with a sublithographic density. In contrast to previous approaches, we did not only define parallel NW layers, but we also demonstrated the possibility of having crossing spacers in a crossbar fashion. In addition, we used the MSPT not for the definition of nanomolds as in some previous approaches, rather for the direct definition of the crossing spacers, which makes the process self-aligned and maskless. We characterized the poly-SiNWs fabricated with this technique. We reported their ambipolarity and a hysteresis in their  $V_{\rm ds}$ - $V_{\rm gs}$ transfer characteristic due to the contact and channel types. We also demonstrated the capability of the MSPT to yield crossing spacers with an extrapolated cross-point density of  $10^{10}$  cm<sup>-2</sup>. We explored potential future application fields of the presented technique, such as dense memory arrays of single poly-SiNWs and NW logic decoders, and we analyzed the technological costs

#### ACKNOWLEDGMENT

challenging this technique.

The authors would like to thank CMI staff at École Polytechnique Fédérale de Lausanne for their help with the fabrication.

#### REFERENCES

- Z. Zhong, D. Wang, Y. Cui, M. W. Bockrath, and C. M. Lieber, "Nanowire crossbar arrays as address decoders for integrated nanosystems," *Science*, vol. 302, pp. 1377–1380, Nov. 2003.

- [2] K. Moselund, P. Dobrosz, S. Olsen, V. Pott, L. De Michielis, D. Tsamados, D. Bouvet, A. O'Neill, and A. Ionescu, "Bended gate-all-around nanowire MOSFET: A device with enhanced carrier mobility due to oxidationinduced tensile stress," in *Proc. IEEE Int. Electron Devices Meeting* (*IEDM*), Washington, DC, Dec. 2007, pp. 191–194.

- [3] S. Ecoffey, V. Pott, D. Bouvet, M. Mazza, S. Mahapatra, A. Schmid, Y. Leblebici, M. Declercq, and A. Ionescu, "Nanowires for room temperature operated hybrid cmos-nano integrated circuits," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC), Dig. Tech Papers*, San Francisco, CA, Feb. 2005, vol. 1, pp. 260–597.

- [4] G. F. Cerofolini, "Realistic limits to computation. Part II. The technological side," Appl. Phys. A, vol. 86, no. 1, pp. 31–42, 2007.

- [5] W. Wu, G.-Y. Jung, D. L. Olynick, J. Straznicky, Z. Li, X. Li, D. A. A. Ohlberg, Y. Chen, S.-Y. Wang, J. A. Liddle, W. M. Tong, and R. S. Williams, "One-kilobit cross-bar molecular memory circuits at 30-nm half-pitch fabricated by nanoimprint lithography," *Appl. Phys. A: Mater. Sci. Process.*, vol. 80, no. 6, pp. 1173–1178, 2005.

- [6] Y. Zhang, S. Kim, J. McVittie, H. Jagannathan, J. Ratchford, C. Chidsey, Y. Nishi, and H.-S. Wong, "An integrated phase change memory cell with Ge nanowire diode For cross-point memory," in *Proc. IEEE Symp. VLSI Technol.*, Jun. 2007, pp. 98–99.

- [7] R. Shenoy, K. Gopalakrishnan, C. Rettner, L. Bozano, R. King, B. Kurdi, and H. Wickramasinghe, "A new route to ultra-high density memory using the micro to nano addressing block (MNAB)," in *Proc. Symp. VLSI Technol., Dig Tech. Papers*, 2006, pp. 140–141.

- [8] R. Beckman, E. Johnston-Halperin, Y. Luo, J. E. Green, and J. R. Heath, "Bridging dimensions: Demultiplexing ultrahigh density nanowire circuits," *Science*, vol. 310, no. 5747, pp. 465–468, 2005.

- [9] J. D. Holmes, K. P. Johnston, R. C. Doty, and B. A. Korgel, "Control of thickness and orientation of solution-grown silicon nanowires," *Science*, vol. 287, no. 5457, pp. 1471–1473, 2000.

- [10] D. Whang, S. Jin, Y. Wu, and C. M. Lieber, "Large-scale hierarchical organization of nanowire arrays for integrated nanosystems," *Nano. Lett.*, vol. 3, no. 9, pp. 1255–1259, 2003.

- [11] K. E. Moselund, D. Bouvet, H. H. Ben Jamaa, D. Atienza, Y. Leblebici, G. De Micheli, and A. M. Ionescu, "Prospects for logic-on-a-wire," *Microelectron. Eng.*, pp. 1406–1409, 2008.

- [13] D. C. Flanders and N. N. Efremow, "Generation of [less-than] 50 nm period gratings using edge defined techniques," J. Vac. Sci. Technol. B: Microelectron. Nanometer Struct., vol. 1, no. 4, pp. 1105–1108, 1983.

- [14] Y.-K. Choi, T.-J. King, and C. Hu, "A spacer patterning technology for nanoscale cmos," *IEEE Trans. Electron Devices*, vol. 49, no. 3, pp. 436– 441, Mar. 2002.

- [15] K. Asano, Y.-K. Choi, T.-J. King, and C. Hu, "Patterning sub-30-nm MOSFET gate with i-line lithography," *IEEE Trans. Electron Devices*, vol. 48, no. 5, pp. 1004–1006, May 2001.

- [16] B. Dayole, R. Arghavani, D. Barlage, S. Datta, M. Doczy, J. Kavalieros, A. Murthy, and R. Chau, "Transistor elements for 30 nm physical gate length and beyond," *Intel Technol. J.*, vol. 6, pp. 42–54, 2002.

- [17] Y. Choi, "Spacer FinFET: Nanoscale double-gate CMOS technology for the terabit era," *Solid State Electron.*, vol. 46, pp. 1595–1601, Oct. 2002.

- [18] J. Hallstedt, P. Hellstrom, and H. Radamson, "Sidewall transfer lithography for reliable fabrication of nanowires and deca-nanometer MOSFETs," *Thin Solid Films*, vol. 517, pp. 117–120, Nov. 2008.

- [19] Z. Yu, W. Wu, L. Chen, and S. Y. Chou, "Fabrication of large area 100 nm pitch grating by spatial frequency doubling and nanoimprint lithography for subwavelength optical applications," *J. Vac. Sci. Technol. B: Microelectron. Nanometer Struct.*, vol. 19, pp. 2816–2819, Nov. 2001.

- [20] J. Hållstedt, P.-E. Hellström, Z. Zhang, B. Malm, J. Edholm, J. Lu, S.-L. Zhang, H. Radamson, and M. Östling, "A robust spacer gate process for deca-nanometer high-frequency mosfets," *Microelectron. Eng.*, vol. 83, no. 3, pp. 434–439, 2006.

- [21] Y.-K. Choi, "Sublithographic nanofabrication technology for nanocatalysts and DNA chips," J. Vac. Sci. Technol. B: Microelectron. Nanometer Struct., vol. 21, pp. 2951–2955, 2003.

- [22] G. F. Cerofolini, P. Amato, and E. Romano, "The multispacer patterning technique: A non-lithographic technique for terascale integration," *Semicond. Sci. Technol.*, vol. 23, p. 075020, July 2008.

- [23] S. R. Sonkusale, C. J. Amsinck, D. P. Nackashi, N. H. di Spigna, D. Barlage, M. Johnson, and P. D. Franzon, "Fabrication of wafer scale, aligned sub-25nm nanowire and nanowire templates using planar edge defined alternate layer process," *Phys. E: Low-Dimensional Syst. Nanostruct.* vol. 28, pp. 107–114, Jul. 2005.

- [24] S. Goldstein and D. Rosewater, "Digital logic using molecular electronics," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC), Dig. Tech. Papers*, San Francisco, CA, 2002, vol. 1, pp. 204–459.

- [25] A. DeHon and K. K. Likharev, "Hybrid CMOS/nanoelectronic digital circuits: Devices, architectures, and design automation," in *Proc. IEEE/ACM Int. Conf. Comput.-Aided Des. (ICCAD)*, Pasadena, CA, 2005, pp. 375– 382.

- [26] K. K. Likharev, "Hybrid semiconductor/nanoelectronic circuits: Freeing advanced lithography from the alignment accuracy burden," J. Vac. Sci. Technol. B: Microelectron. Nanometer Struct., vol. 25, pp. 2531–2536, 2007.

- [27] Y. Luo, C. P. Collier, J. O. Jeppesen, K. A. Nielsen, E. DeIonno, G. Ho, J. Perkins, H.-R. Tseng, T. Yamamoto, J. F. Stoddart, and J. R. Heath, "Two-dimensional molecular electronics circuits," *J. Chem. Phys. Phys. Chem.*, vol. 3, pp. 519–525, 2002.

- [28] A. DeHon, "Design of programmable interconnect for sublithographic programmable logic arrays," in *Proc. Int. Symp. Field-Programmable Gate Arrays (FPGA)*, Monterey, CA, 2005, pp. 127–137.

- [29] M. H. B. Jamaa, D. Atienza, K. E. Moselund, D. Bouvet, A. M. Ionescu, Y. Leblebici, and G. De Micheli, "Variability-aware design of multi-level logic decoders for nanoscale crossbar memories," *IEEE Trans. Comput.-Aided Des.*, vol. 27, no. 11, pp. 2053–2067, Nov. 2008.

- [30] A. DeHon, P. Lincoln, and J. Savage, "Stochastic assembly of sublithographic nanoscale interfaces," *IEEE Trans. Nanotechnol.*, vol. 2, no. 3, pp. 165–174, Sep. 2003.

- [31] J. E. Savage, E. Rachlin, A. DeHon, C. M. Lieber, and Y. Wu, "Radial addressing of nanowires," ACM J. Emerging Technol. Comput. Syst., vol. 2, no. 2, pp. 129–154, 2006.

- [32] T. Hogg, Y. Chen, and P. Kuekes, "Assembling nanoscale circuits with randomized connections," *IEEE Trans. Nanotechnol.*, vol. 5, no. 2, pp. 110– 122, Mar. 2006.

- [33] M. H. Ben Jamaa, Y. Leblebici, and G. De Micheli, "Decoding nanowire arrays fabricated with the multispacer patterning technique," presented at the Design Automat. Conf., San Francisco, CA, Jul. 2009.

- [34] G. F. Cerofolini, G. Arena, M. Camalleri, C. Galati, S. Reina, L. Renna, D. Mascolo, and V. Nosik, "Strategies for nanoelectronics," *Microelectron. Eng.*, vol. 81, nos. 2–4, pp. 405–419, 2005.

- [35] W. M. Weber, L. Geelhaar, A. P. Graham, E. Unger, G. S. Duesberg, M. Liebau, W. Pamler, C. Cheze, H. Riechert, P. Lugli, and F. Kreupl, "Silicon-nanowire transistors with intruded nickel-silicide contacts," *Nano Lett.*, vol. 6, no. 12, pp. 2660–2666, 2006.

- [36] A. Colli, S. Pisana, A. Fasoli, J. Robertson, and A. C. Ferrari, "Electronic transport in ambipolar silicon nanowires," *Phys. Status Solidi. (B)*, vol. 244, no. 11, pp. 4161–4164, 2007.

- [37] Y. Ahn, J. Dunning, and J. Park, "Scanning photocurrent imaging and electronic band studies in silicon nanowire field effect transistors," *Nano Lett.*, vol. 5, no. 7, pp. 1367–1370, 2007.

- [38] S. M. Sze, Phys. Semicond. Devices. Hoboken, NJ: Wiley, 1981.

- [39] J. E. Green, J. Wook Choi, A. Boukai, Y. Bunimovich, E. Johnston-Halperin, E. Deionno, Y. Luo, B. A. Sheriff, K. Xu, Y. Shik Shin, H.-R. Tseng, J. F. Stoddart, and J. R. Heath, "A 160-kilobit molecular electronic memory patterned at 10<sup>11</sup> bits per square centimetre," *Nature*, vol. 445, pp. 414–417, 2007.

- [40] International Technology Roadmap for Semiconductors (ITRS). (2007). Tech. Rep. [Online]. Available: http://www.itrs.net/reports.html

**M. Haykel Ben Jamaa** (S'08–M'10) received the M.S. degree in electrical engineering from Technische Universität München, Munich, Germany, and Ecole Centrale Paris, Paris, France, in 2004, and the Ph.D. degree from École Polytechnique Fédérale de Lausanne, Lausanne, Switzerland, in 2009.

He is a Postdoctoral Researcher at Commissariat à l'Energie Atomique et aux Energies Alternatives (CEA-LETI), Grenoble, France. His current research interests include design aspects for nanoelectronics with a tight link to emerging fabrication technolo-

gies, regular logic circuits such as field-programmable gate array, emerging memories, and 3-D integration.

Dr. Jamaa was the recipient of the Electronic Design Automation Outstanding Dissertation Award at the Design, Automation, and Test in Europe (DATE) 2010. He was also engaged in many conferences as the TPC Member or Chair including DATE (2008), Network-on-Chips (2010), and Very Large Scale Integration–System on Chip (2010).

Gianfranco Cerofolini received the Ph.D. degree in physics from the University of Milan, Italy, in 1970. He was with SAES Getters, Telettra, ENI, and STMicroelectronics. He is currently a Lecturer at the University of Milano-Bicocca, Milan. He is author of 300 articles, chapters to books, and encyclopaedic items, two books: *Physical Chemistry of, in and on Silicon*, and *Nanoscale Devices* (both for Springer). He holds a score of patents. His research interests include physical limits of miniaturization and to the "emergence" of higher level phenomena from the un-

derlying lower level substrate (measurement in quantum mechanics, life in biological systems, etc.), adsorption, biophysics, CMOS processing (oxidation, diffusion, ion implantation, and gettering), electronic and optical materials, theory of acidity, nanoelectronics, gettering technique, ST's first silicon-gate CMOS process, a process for low-fluence SOI, a strategy for molecular electronics via a conservative extension of the existing microelectronic technology, the preparation and characterization of ideal p–n junctions, the discovery of a mechanism of pure generation without recombination, a description of the layer-by-layer oxidation of silicon, and mathematical techniques to describe the adsorption on heterogeneous or soft surfaces.

Giovanni De Micheli (S'79–M'79–SM'80–F'94) is currently a Professor and the Director of the Institute of Electrical Engineering and the Integrated Systems Centre, École Polytechnique Fédérale de Lausanne, Lausanne, Switzerland. He is also a Program Leader of the Nano-Tera.ch program. He was a Professor of Electrical Engineering at Stanford University. His research interests include several aspects of design technologies for integrated circuits and systems, such as synthesis for emerging technologies, networks on chips 3-D integration, heterogeneous platform design

including electrical components and biosensors, as well as in data processing of biomedical information.

Prof. De Micheli is the recipient of the 2003 IEEE Emanuel Piore Award. He is a Fellow of the Association for Computing Machinery. He was also the recipient of the Golden Jubilee Medal for outstanding contributions to the IEEE CAS Society in 2000 and the 1987 D. Pederson Award for the best paper on the IEEE TRANSACTIONS ON COMPUTER-AIDED DESIGN OF INTEGRATED CIRCUITS AND SYSTEMS (TCAD/ICAS). He was the Division 1 Director (2008–2009), Co-Founder and the President Elect of the IEEE Council on EDA (2005–2007), the President of the IEEE CAS Society 2003, the Editor in Chief of the IEEE TCAD/ICAS (1987–2001). He has been the Chair of several conferences, including DATE (2010), pHealth (2006), VLSI SOC (2006), DAC (2000), and ICCD (1989).

**Yusuf Leblebici** (M'90–SM'98) received the Ph.D. degree in electrical and computer engineering from the University of Illinois at Urbana-Champaign, Champaign, in 1990.

He was with the University of Illinois at Urbana-Champaign, Istanbul Technical University, Maslak, and Worcester Polytechnic Institute, Worcester, MA. Since 2002, he has been the Chair Professor at the Swiss Federal Institute of Technology, Lausanne, Switzerland, and the Director of Microelectronic Systems Laboratory, Lausanne. He is the coauthor of four

textbooks as well as more than 200 articles published in various journals and conferences. His research interests include the design of high-speed CMOS digital and mixed-signal integrated circuits, computer-aided design of VLSI systems, intelligent sensor interfaces, modeling and simulation of semiconductor devices, and VLSI reliability analysis.

Dr. Leblebic has been elected as Distinguished Lecturer of the IEEE Circuits and Systems Society for 2010–2011. He has been engaged as an Associate Editor of IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS (II), and IEEE TRANSAC-TIONS ON VERY LARGE SCALE INTEGRATED (VLSI) SYSTEMS. He was also the General Co-Chair of the 2006 European Solid-State Circuits/Device Research Conference.