# **Specification and Analysis of Power-Managed Systems**

# ALESSANDRO BOGLIOLO, LUCA BENINI, EMANUELE LATTANZI, AND GIOVANNI DE MICHELI, FELLOW, IEEE

# **Contributed Paper**

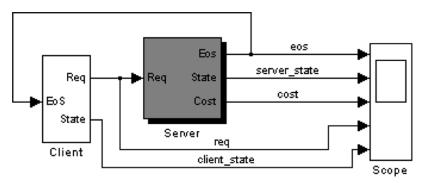

Dynamic power management encompasses several techniques for reducing energy dissipation in electronic systems by selective slowdown or shutdown of components. We present a theoretical framework for explaining and classifying different approaches to power management. Within this framework, we model power-manageable components, workloads, and controllers as discrete-event systems (DESs). The structure of these DESs is specified in terms of physical states (representing operation modes) and events (triggering state transitions), while system behavior is specified in terms of next-event and next-state functions. In particular, nondeterministic next-event and next-state functions are modeled by conditional probability distributions, according to generalized semi-Markov processes (GSMPs).

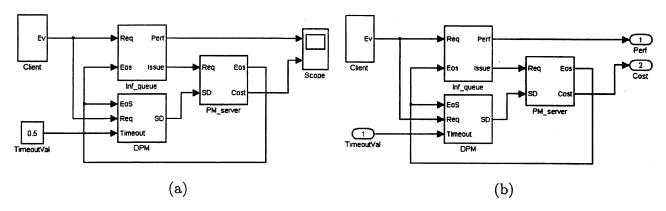

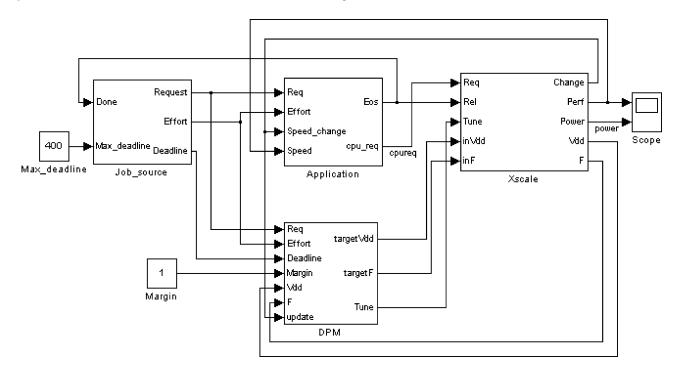

The modeling framework provides a general denotational model for system specification and a rigorous execution semantics that enables event-driven simulation. We introduce a modeling framework, built on top of MathWork's Simulink, supporting the specification and execution of our model. In particular, we present templates for the Simulink simulator to execute GSMP models, and we describe how to use such templates for specifying, analyzing, and optimizing dynamic power-managed systems.

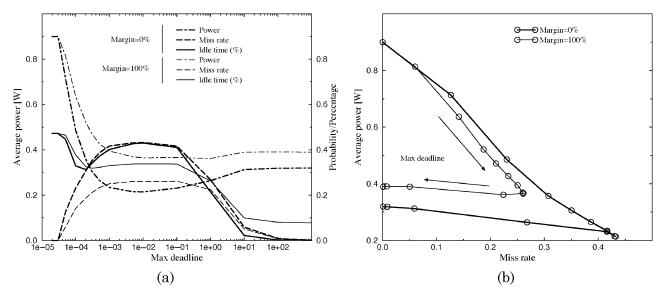

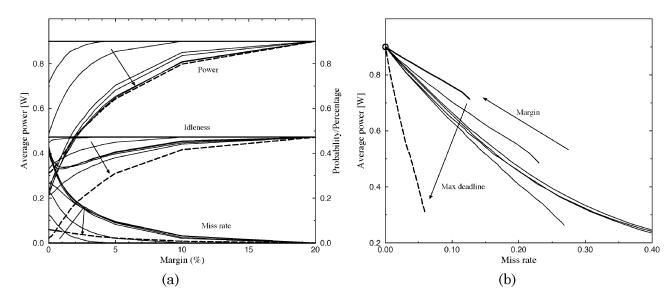

Finally, we demonstrate the expressive power and versatility of the proposed approach by using the modeling framework and the simulator for the analysis of representative real-life case studies, including the Intel Xscale processor architecture, a multitasking real-time system, and a sensor network.

*Keywords*—*Low-energy design, power management, stochastic control, system on a chip.*

#### I. INTRODUCTION

The average citizen of an industrialized country interacts with tens of electronic appliances every day, while working,

Manuscript received December 4, 2003; revised April 12, 2004. This work was supported by the National Science Foundation under Grant CCR-0305718.

A. Bogliolo and E. Lattanzi are with the Information Science and Technology Institute, University of Urbino, Urbino 61029, Italy (e-mail: bogliolo@sti.uniurb.it).

L. Benini is with the Department of Electronics and Computer Science, University of Bologna, Bologna 40127, Italy.

G. De Micheli is with Stanford University, Stanford, CA 94305 USA. Digital Object Identifier 10.1109/JPROC.2004.831207 traveling, and at home. Arguably, the diffusion of electronics is one of the distinctive characteristics of human civilization in the new millennium. All electronic systems consume energy to perform their task and the impact of electronic systems on the power budget of densely populated areas is steadily growing. At the same time, portable, embedded electronics are becoming increasingly pervasive in today's life: cellular phones, electronic organizers, and digital cameras are just a few examples of devices that are considered almost indispensable for work and entertainment. Reducing power consumption in these devices enables aggressive miniaturization, longer time between battery recharges (or changes), and, ultimately, deeper market penetration.

Energy efficiency is a primary design objective for increasingly large classes of electronic systems. While in the past energy efficiency was almost invariably associated with battery-powered operation [20], [21] nowadays it has become a concern also for electric-grid powered equipment, like servers, network switches, routers, etc. [22]. The quest for energy efficiency has two main facets. On one hand, new systems should be designed with clearly specified energy budgets, and energy consumption considerations should percolate through all phases of the design process, from system conception to elementary devices and technology. On the other hand, electronic systems should be managed efficiently from the power viewpoint during their in-field operation. The focus of this work is on power management of electronic systems.

The fundamental rationale for power management is quite intuitive. Systems are generally designed to deliver specified levels of performance under heavy load. During in-field operation, a system is often underutilized and, therefore, it can be operated in a reduced performance mode to save energy. If the entire system, or some of its components, are completely idle, they can be shut down while waiting for some service request. In the past, power management has been more an afterthought than a fully developed design discipline. Unfortunately, when a system has not been designed with energy efficiency objectives, transitions from a fully operational state to low-power, reduced functionality modes of operation are slow and expensive, or, in some cases, simply not possible. Hence, the *power manager* (PM), i.e., the system entity in charge of controlling mode transitions, has limited degrees of freedom. Furthermore, it should carefully weight the costs of mode transitions (which are certain when a transition is made) against the potential energy savings (which depend on the uncertain duration of the idle condition).

Power management strategies (also called *policies*) in the above outlined setting have been studied intensively in the last few years [23]. Substantial energy savings have been achieved when designers have started supporting power management. Recently, the electronic component market has witnessed the announcement of numerous new components with multiple, finely controllable modes of operation that trade off performance with power consumption, e.g., variable-frequency, variable-voltage operation [24], [25]. Components with multiple active states based on dynamic frequency and voltage scaling have created many new opportunities for dynamic power management (DPM). In such a rapidly evolving setting, the modeling, analysis, and optimization techniques developed in the past are not general and powerful enough, and a richer theoretical framework is needed to sustain the development of novel, advanced power management techniques.

The main objective of this paper is to build such a framework in a theoretically sound fashion, leveraging abstractions and techniques from several correlated disciplines, such as stochastic modeling, discrete-event systems (DESs), simulation theory and sensitivity analysis, stochastic optimization, and control. We aim at bridging the gap between electronic system designers and researchers working in the above mentioned fields, in order to facilitate cross fertilization and multidisciplinary research in a strategic area for current and future applications.

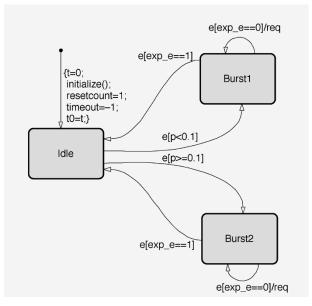

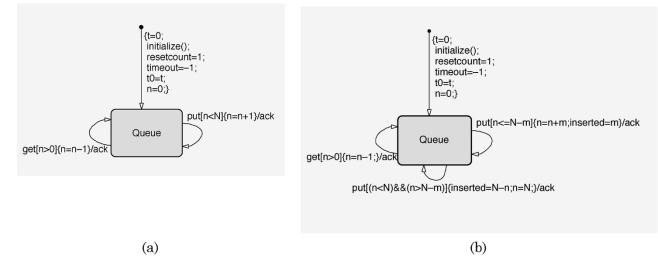

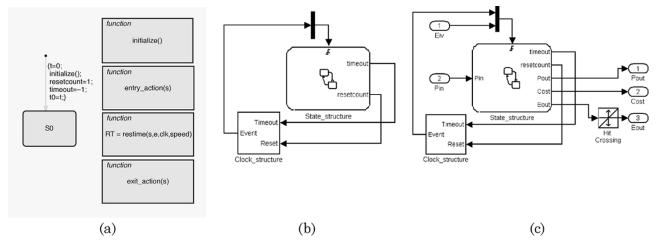

The paper is divided in four parts. First, a general overview is given of technology and architectural trends. The main purpose of this section is to demonstrate the increasing importance of DPM and to contextualize our work. The remaining three sections are the technical core of the paper, focusing on system modeling, simulation, and applications. We will model power-manageable components, workloads, and controllers as DESs [26]. The structure of a DES is specified in terms of physical states (representing operation modes) and events (triggering state transitions), while system behavior is specified in terms of next-event and next-state functions. The modeling framework we propose provides: 1) a general denotational model for system specification (supporting, in particular, composition and abstraction); 2) a rigorous execution semantics that enables event-driven simulation; and 3) a formalism for specifying the probabilistic structure of generalized semi-Markov processes (GSMPs) [27]. The modeling framework provides us with a means of classifying different DPM systems based on the properties of their models.

Next, we present a system modeling infrastructure, built on top of MathWork's Simulink [28], supporting the specification and execution of DES/GSMP models. In particular, we describe templates for the Simulink simulator to execute GSMP models, and we describe how to use such templates for specifying DPM systems of practical interest. Finally we show how to use the simulator to evaluate and optimize system parameters and DPM policies.

In the last part of the paper, we demonstrate the expressive power and versatility of the proposed approach by using the modeling framework and the simulator for the analysis of representative case studies.

#### II. POWER MANAGEMENT: WHY AND HOW

As outlined in the introduction, system designers are faced by an unprecedented *power crisis*, and power management is currently the most effective response to the challenge. To fully motivate this assertion, we first review the trends of evolution of current technologies and architectures, then we analyze the state of the art in power-manageable systems (PMSs) and give a few representative examples.

### A. Technology Trends

The trends in semiconductor technologies are characterized by decreasing feature sizes and increasing device densities. As a result, the energy dissipated per unit area is rising and is posing an unprecedented challenge to designers. To cope with this and other problems (e.g., hot carrier effects), the supply voltage is also reduced. Nevertheless, the downscaling of supply voltages is not sufficient to contrast the increasing power consumption trends in chips.

Indeed, there are three factors that contribute to increasingly higher energy dissipation with downscaled technologies: the energy on global interconnect wires, the aggressive increase of operating frequencies and the dominating contribution of leakage currents. We analyze these three factors next.

First, silicon technology is becoming increasingly interconnect dominated. Since global wire length does not scale down, both delay and energy dissipation on global interconnect dwarf those of computation and storage units. Indeed, while the gate capacitance of minimum-size transistors is decreasing, the interconnect capacitance per unit length is not decreasing at the same speed (because of fringing capacitance contributions) and interconnect length is not decreasing for global wires. Hence, the C factor in the wellknown switching power equation  $P_{sw} = kCV_{DD}^2 f$  (where k represents switching activity) does not scale down as fast as minimum feature size [29], [30].

Second, in order to reap performance benefits (in other words, to satisfy quality of service requirements), chip clock frequency is scaled faster than technology [31], i.e., the percentage increase in frequency in an upgraded technology is higher than the percentage decrease of feature sizes. This result is achieved by clever architectural optimizations that reduce the number of logic stages to be traversed within the clock cycle time. From a power viewpoint, this is clearly a problem, because power is directly proportional to switching frequency f. Performance constraints (or objectives) are also the main reason why supply voltage scaling is not as drastic

as one would desire for power minimization purposes. In fact, transistor switching speed decreases as  $(V_{\rm DD} - V_T)^{\alpha}$ , with  $1 < \alpha < 2$ . This cannot be tolerated if performance is tightly constrained.

Third, deep submicrometer transistors are increasingly leaky in the OFF state. Source-to-drain current due to subthreshold conduction is the dominant cause of leakage, but drain-to-gate currents due to electron tunneling across the gate oxide is also becoming significant. Furthermore, random variations of the number of dopant atoms in the channel region cause poor threshold control, and many transistors have a threshold significantly lower than nominal. Unfortunately, subthreshold conduction is exponentially dependent on threshold voltage and transistors with lower threshold leak exponentially more than nominal transistors. As a result, chip standby power is becoming a significant concern. Clearly, subthreshold leakage is also a heavy limiter to threshold voltage  $V_T$  reduction, with obvious negative impact on supply voltage scaling [31].

In summary, power dissipation will grow significantly in future technologies, unless innovative design techniques are used. Because of the increasing importance of leakage currents, even standby power is expected to increase. Technologists are pointing at power as the one of the most likely show-stoppers to technology scaling if adequate countermeasures are not taken.

# B. Architectural Trends

Technology evolution is not going to solve the power consumption problem. On the contrary, many technologists refer to design innovation at the circuit, logic, architectural level as a way out from the crisis. Unfortunately, trends in this area are not favorable to energy efficiency at all. Even though a significant research effort is being devoted to power minimization, mainstream architectural design is moving toward energy-hungry architectures.

Most electronic systems are nowadays designed with a high degree of programmability. The majority contains one or more core processors, and many instantiate several programmable coprocessors (e.g., very long instruction word (VLIW) units for numerical computations, programmable IO processors, etc.). A few recent designs even embed a significant amount of bit-programmable logic (field-programmable gate array (FPGA) fabrics) [32]. Programmability is a fundamental requirement when designing large-scale systems on chips (SoCs) for three main reasons. First, it ensures functional flexibility, which widens the spectrum of applicability and the potential production volume. Second, it leaves margins for postfabrication bug fixing and tuning, thereby enhancing yield. High yield and volume of sales are required to amortize ballooning mask development and fabrication costs. Third, processor-based architectures reduce design time because they emphasize reuse of hardware modules (e.g., the cores themselves, the memories, etc.) as well as software components (e.g., libraries, operating systems, compilers).

Yet, flexibility and reuse come at a price. The power-performance ratio (i.e., the energy) required by a processor to carry out a given task (e.g., MPEG decoding) is several orders of magnitude (three or more) higher than what could be achieved with an application-specific architecture [21], [33]. Advanced processors, often required to attain performance goals, are even more power-hungry than simple processors, because they rely on various forms of speculative execution to increase the average number of instructions executed in a clock cycle. Well-known performance enhancement techniques, such as speculating past branches, value prediction, and prefetching, imply the execution of redundant operations which increase power consumption.

Fine-grained programmable fabrics can be one or more orders of magnitude more energy efficient than processors [33] for some classes of computations, but they still incur a very significant overhead with respect to dedicated logic. Recent data shows that computation performed by an embedded FPGA fabric in a hybrid FPGA-application-specific IC (ASIC) chip is more than two orders of magnitude more power consuming and more than ten times slower than the same computation in dedicated logic [32]. The overhead in this case is mainly due to communication between fine-grain programmable logic elements, which is performed on massively redundant programmable wiring resembling a multistage network, as opposed to dedicated, instance-specific wires. Additionally, programmable logic blocks are often much more complex than the basic gates they mimic when programmed.

# C. Power-Manageable Hardware

As seen above, programmability is generally adverse to power efficiency. However, there is a way to profitably exploit programmability to reduce power consumption, namely, via power management. Supporting power management requires adding hardware resources that do not have a computational task, but they dedicated to controlling the power level of functional units, detecting and exploiting idleness, and locally trading off performance with power. Power-manageable architectures ultimately aim at reducing idle power (i.e., the power consumed by a hardware component when it is not in use) and active power, through the dynamic control of transistor thresholds and supply voltage, clock activity, and frequency.

To reduce leakage power in idle state, variable-threshold circuits control the threshold voltage of transistors through substrate biasing. When a variable-threshold circuit becomes quiescent, the substrate of NMOS transistors is negatively biased, and their threshold increases because of the well-known *body-bias effect*. A similar approach can be taken for PMOS transistors (which require positive body bias). Variable-threshold circuits can in principle solve the quiescent leakage problem, but they require standby control circuits that modulate substrate voltage [34].

Idle power is not only caused by leakage, but it is also due to unneeded switching activity. Clock switching within idle functional units is the best-known example of this problem. Clock gating [35] is used to eliminate unneeded clock activity. Most low-power processors implement both hardware and software controlled clock gating through dedicated power-down instructions. A radical way to eliminate idle power (both leakage and dynamic) is to disconnect a unit from its power supply [20]. Unfortunately, in this case state information is lost; therefore, relevant state bits must be saved (for instance, in nonvolatile memories) before shutdown and recovered upon restart. State saving and restoring significantly increases the overhead associated with shutdown transitions.

To minimize active power, circuits should be run as slow as possible (within performance constraints) to eliminate slack while at the same time minimizing supply voltage [20]. This translates into cubic power savings (and quadratic energy savings). Variable-voltage circuits [24], [36] offer the possibility of modulating the power supply dynamically during system operation. In practice, the implementation of this technique requires considerable design ingenuity. First, voltage changes require nonnegligible time, because of the large time constants of power supply circuits. Second, the clock speed must be varied consistently with the varying speed of the core logic when supply voltage is changed. Even though slowdown coupled with voltage reduction is more effective than running the circuit at maximum speed and then shutting it down as soon as it becomes idle [36], the two approaches are not mutually exclusive. Clearly, slowing down a circuit reduces its idleness, but in many cases it cannot eliminate it.1

Power-manageable hardware can be abstracted as a state machine where states represents various modes of operation and transitions have a cost [23]. In the remainder of this section, we give a few examples of complex, practical PMSs, and we describe informally their state-based representations. The same examples will be formally described and analyzed in a quantitative fashion in Section V.

1) Multiple Power States: Modern power-manageable processors support multiple shutdown modes, as well as variable-voltage operation. The Intel Xscale processor is an example of an architecture with advanced power management features, namely: 1) user controllable processor speed and voltage supply; 2) multiple sleep states; and 3) performance monitoring hardware. The first prototype Xscale processor [37] could run with core voltage ranging from 0.70 to 1.65 V, the corresponding clock frequencies being 50 and 800 MHz, respectively. At top speed, power consumption is 900 mW and power efficiency is 850 million instructions per second per watt (MIPS/W). At the lowest speed, power consumption is 55 mW, with a corresponding power efficiency of 4500 MIPS/W. Supply voltages could be varied without stopping or resetting the processor, with a maximum slew rate of 4 mV/ $\mu$ s. However, clock frequency changes require 20  $\mu$ s. to relock and stabilize the clock generator. Three inactive states are supported, namely, *idle*, drowsy, and sleep. In idle state, the clock distribution is gated off, but the clock generator keeps running. Power is reduced to approximately 10 mW, and exit from the idle state requires a single clock cycle. In drowsy, or standby mode, the phase-locked loop (PLL) clock generator is turned off, reducing power consumption to 100  $\mu$ W. Exit from the drowsy state requires approximately 20  $\mu$ s. Finally, in sleep mode, the core is completely powered down, reducing power virtually to zero (with the exception of pin power), and internal state is lost. Resuming operation from sleep requires a complete processor reset sequence and context recovery (several thousand cycles).

The first commercial component derived from the Xscale architecture, the Intel 80 200 core processor, is very similar to the research prototype described above, with a few exceptions. First, clock speed changes are quantized. Clock speed is set by writing to a special control register. Ten different speeds are supported and lock speed changes require approximately 1000 clock cycles. Even though the processor could in principle run at ten different supply voltages, one for each available clock speed, a maximum of four voltage levels is recommended. Hence, we have two different speeds for each supply voltage. Furthermore, the drowsy state is not supported (only idle and sleep are available). Exit from idle takes approximately ten cycles, and resuming from sleep requires a few milliseconds, depending of the amount of state information that must be saved and restored. Probably the most important extra feature available in the commercial component is a large number of hardware monitoring registers that provide accurate counts of many significant runtime parameters, such as cache misses, table look-aside buffer (TLB) misses, exceptions, etc. These counters can be very useful in determining actual processor performance at runtime, thereby facilitating the implementation of "closed-loop" policies, where power management decisions are based on runtime performance estimates [15].

Xscale is only a single design point. Several variable-voltage processors have been announced, and some are available on the market [24]. Furthermore, with the diffusion of multiprocessor SoCs (MPSoCs) for embedded multimedia and signal processing applications, the number of variable-frequency/variable-voltage cores integrated onto a single chip is going to increase very rapidly. Thus, there are ample and growing opportunities for DPM schemes exploiting the additional degrees of freedom offered by variable-voltage operation.

Variable-voltage processors are not the only electronic components supporting multiple active and sleep states. Wireless network interfaces are another important family of devices with similar characteristics. For the sake of illustration, let us focus on IEEE802.11b (WIFI) cards [16], [17]. WIFI cards have multiple inactive states, whose precise definition is implementation and vendor specific. In general, most cards support an "off" state, where power dissipation is negligible and association with the wireless network is lost. A card in this state is not responsive and cannot be located by the base station. A transition out of the off state is very time-consuming (a few hundreds of milliseconds), mainly because it involves not only hardware activation, but also network reassociation. Other inactive states ("doze") are

<sup>&</sup>lt;sup>1</sup>Consider, for instance, an MP3 player. When the device is active, it operates under tight performance constraints (namely, real-time playback), and obviously it is not possible to stretch execution time beyond the duration of a music track, even if after it has been played out, the player remains idle for hours.

supported, where the card does not lose association with the network, but it does not explicitly transmit or receive data. This behavior is enabled by a feature of the IEEE802.11 protocol family, which provides for periodic synchronization frames (beacons). When idle, the card is activated very briefly only to deal with beacons. Doze states have small reactivation time of a few milliseconds and do not imply any packet loss (thanks to buffering at the base station). Power consumption is a factor of five to ten lower than that in receive state, but it is not negligible (in the order of tens of milliwatts).

The most power consuming state for WIFI cards is the transmit state. When transmitting, the output RF amplifier is active, and significant power is radiated through the antenna, in addition to the power consumed for baseband processing. Power consumption in this state can exceed 1 W, a factor of two higher than the receive power. Advanced cards support output power control to allow fine tuning of transmit power consumption to environment and network conditions. Output power can usually be selected from a finite set of available values; transitions among power levels are fast (a few milliseconds).

Clearly, wireless network interface cards are very flexible in terms of available power states. Optimal power management for these devices is a complex task, which is often tackled with distributed policies, as discussed in the next section.

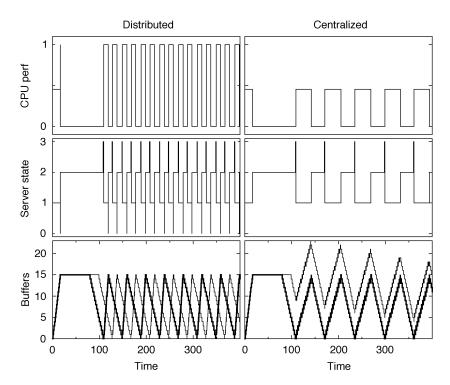

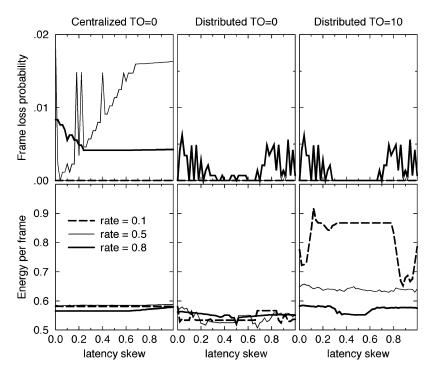

2) Interacting Power-Manageable Devices: Complex systems can contain multiple power-manageable devices. In this case, power management requires fine-grain decision on state transitions for multiple interacting devices. If devices are closely coupled (e.g., on the same die or board), power management can be performed either by a single centralized controller or by local interacting controllers [56]. As coupling becomes weaker, centralized power management becomes increasingly hard, mainly because is difficult and expensive to collect information and issue commands to many distributed, loosely coupled components.

Wireless networks are perhaps the most well-understood example of distributed PMSs. A huge amount of research has focused on power management for wireless networks, especially for widespread technologies like IEEE802.11a/b [5], [7], [12], [14]. Even though most of the seminal work in this area was theoretical in nature, it has propelled the development of advanced network cards (like the ones described in the previous section) with a high level of power controllability. Thus, many approaches developed in the past are likely to find practical application in the near future. We can coarsely classify power management schemes in two broad classes: those focusing on transmit power reduction [13], and those aiming at minimizing the power spent in receive mode [2], [11], by intelligent exploitation of low-power inactive states (like the "doze" and "off" states described in the previous section). The first class of techniques is particularly relevant in *ad hoc* configurations, where base stations are very sparse or absent, and power-constrained clients have to transmit significant amount of data because of node-to-node forwarding. The second class of techniques has general applicability, since the percentage of idle time for wireless network interfaces is significant for many application scenarios.

Power management policies have been developed at various levels of the network stack, starting from the medium access control (MAC) layer [8], [9] up to the application layer [1], [10]. In general, the proposed techniques imply some form of coordination among multiple network cards and/or the base station, which requires some extra communication. Recurring themes are: 1) minimization of the extra traffic caused by power management (distributed and weakly coordinated policies [4]) and 2) exploration of the computation and storage versus communication power tradeoff (e.g., data compression or caching to reduce the amount of data to be communicated [6], buffering to enable network shutdown [3]).

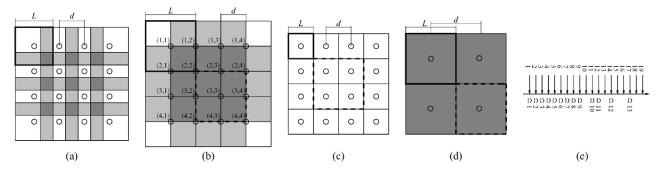

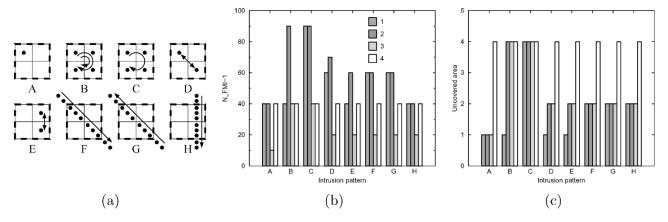

An extreme example of loosely coupled PMS is a wireless *sensor network* [19], [38]. Sensor networks have gained importance in numerous civil and military applications. They can be used to continuously monitor the environment for various types of events, and they operate in a reconfigurable and adaptable fashion under extremely tight power constraints [39]. The node of a sensor network consists of one or more embedded sensors, analog-to-digital converters, a processor with memory, and an RF section for communication with other nodes. Each node is power manageable. Nodes are distributed in a target area often in an irregular fashion and they are usually required to have reduced size (a few cubic centimeters). They are battery operated or self-powered (with a variety of energy-scavenging techniques).

The first practical sensor networks are emerging from research laboratories. A large-scale sensor network with 800 tiny nodes (the size of a quarter), has been recently demonstrated [40]. The node contain a 4 MHz low-power microcontroller (ATMEGA 163) providing 16 KB of flash instruction memory, 512 B of static RAM, analog-digital converters (ADCs), and various simple peripheral interfaces. A 256-KB electrically erasable programmable ROM serves as secondary storage. Sensors, actuators, and a radio network serve as the I/O subsystem. The network utilizes a low-power radio (RF Monolithics T1000) operating at 10 kb/s. The node contains four types of sensors: light, temperature, battery level, and radio signal strength. It can actuate two LEDs, control the signal strength of the radio, and transmit and receive signals. By adjusting the signal strength, the radio cell size can be varied from a couple of feet to tens of meters, depending on the physical environment. A second microcontroller is provided to allow all cores to be reprogrammed over the network. The entire system consumes about 5 mA when active. The radio and the microcontroller consume as much power as a LED. In passive (sensing) mode, they consume only a few microamps while still checking for radio or sensor stimuli that can wake them up.

Power management for networks, primarily targeting sensor networks, is a rapidly developing research area, which spans all layers of the communication protocol stack [41], as well as operating systems and hardware abstraction layers [40], [42]. Needless to say, there are ample opportunities for reducing power consumption in sensor networks, which are characterized by high redundancy and extreme levels of node idleness [18] (nodes are often idle for 99% of the operation time). One of the critical challenges in this area is to minimize idle receive power while at the same time maintaining adequate levels of responsiveness. Another key open issue is the definition of aggregate quality of service and energy efficiency metrics for an entire network, which can be quite different, and often in contrast with single-node metrics.

3) Energy Sources: In many battery-operated mobile applications the ultimate objective of power minimization is ensuring long battery lifetime. It has been shown in [23] that average power reduction and battery lifetime extension may be numerically far apart. This implies that optimizations for minimum average power may not be equally effective in extending battery lifetime, and vice versa.

Charge storage in a battery can be modeled as a capacitor with capacitance  $C = 3600 \cdot \text{CAP}$ , where CAP is the nominal capacity in ampere  $\cdot$  hours, which is usually provided in the battery's data sheet. By setting the initial voltage across the capacitor  $V_C = 1$ , we initialize the battery to its fully charged state. Unfortunately, the simple linear capacitor model is not accurate enough to model complex phenomena observed during battery discharge. In fact, the following three major effects must be taken into account.

- Battery voltage depends nonlinearly on its state of charge: voltage  $V_{\rm Batt}$  decreases monotonically as the battery is discharged, but the rate of decrease is not constant.

- The actual usable capacity of a battery cell depends on the discharge rate: at higher rates, the cell is less efficient at converting its chemically stored energy into available electrical energy.

- The "frequency" of the discharge current affects the amount of charge the battery can deliver: the battery does not react instantaneously to load changes, but it shows considerable inertia, caused by the large time constants typical of electrochemical phenomena.

- Batteries operated at high discharge rate for a short period can recover available charge if the current load is temporarily reduced.

Various approaches have been proposed [43] to model nonideal batteries. An interesting state-based model has been formulated by Chiasserini and Rao [44]. A battery is modeled as a finite-state system, where states represent various charge conditions of the battery, characterized by different voltages. Transitions are caused by current load (to model dependency of discharge rate from load current). The recovery effect can be modeled as a nonzero transition probability toward higher charge states when load current drops to zero. The low-pass filtering effect can be modeled taking the running average of current load.

#### D. A Fragmented Landscape

Concluding this section, observe that the examples we described are representative of large classes of PMSs, and they demonstrate the variety of embodiments of power

management problems in practice. Even though researchers have devised effective techniques in many of these areas, the whole field is characterized by significant fragmentation, which often leads to pitfalls (such as unrealistic assumptions and lack of experimental validation on real-life PMSs) and multiple rediscoveries of the same concepts and techniques.

One of the most striking examples of fragmentation is between shutdown-based and variable-voltage-based power management [also called dynamic voltage scaling (DVS)]. Two largely nonoverlapping groups of researchers have worked on the two themes in the past (refer to [45], [46] for an overview of DVS and to [23] for a survey on shutdown-based DPM), and many have also claimed the superiority of one approach over the other. However, shutdown and voltage scaling are two facets of the same problem: a power-manageable device can have multiple sleep states and multiple active states, characterized by different supply voltage and clock frequency values. Devising an effective power management policy for such a device requires deciding not only transitions between multiple voltages but also when to shut down the device and into which sleep states. Decoupling the two problems can only lead to suboptimal solutions.

Furthermore, many new power management problems are emerging. For instance, several researchers have recently focused on leakage power reduction, which has become a serious concern for large memories in deep submicrometer technologies [47]–[49]. Memory leakage power can be reduced by transitioning unused memory banks to a sleep state from which they can be reactivated with some extra penalty (in terms of activation time and/or stored content loss). This is a power state transition cost versus benefit, which is the core issue in DPM policies and algorithms. It is then possible (and desirable) to leverage the large body of knowledge developed in the area of shutdown-based power management to devise effective memory leakage reduction techniques.

These two examples provide additional evidence of the need for unification of the many flavors of DPM under a common formal modeling framework. This is the main objective of the following sections.

#### III. MODELING

Abstract models are required to formally analyze the properties of physical systems. In the case of power-managed systems, the main challenge is to strike the balance between a high level of detail, including functionality and focusing exclusively on power consumption models. As seen in the previous section, real-life power-manageable components are characterized by a number of different states of operation (power states), trading off power for performance and/or reactivation latency. Hence, a state-based model appears to be a natural abstraction. Furthermore, power state transitions are triggered in an enumerable set of time instants. Therefore, the most natural formal framework for studying the evolution in time of these systems is a DES model [50]. DESs have been extensively studied in the operation research and control systems communities, where DES simulation and simulation-based optimization are among the most widely adopted analysis and optimization approaches [51]. One of the distinctive characteristics of DES models is the presence of sources of nondeterminism (i.e., random events) that represent both modeling uncertainty and the uncertainty caused by the environment (e.g., the workload). For our specific application domain, we wanted to specialize the highly generic DES model in an effort to emphasize the following key characteristics.

- State-based component models, which naturally match the characteristics of real-life power managed components.

- Formally defined composition rules to allow hierarchical composition of complex power managed systems from simpler ones without losing the properties of the model.

- Formally defined sources of nondeterminism, to clearly decouple the parts of the system that are deterministically characterized from the sources of uncertainty.

Among many state-based stochastic DES formalisms, we chose to model PMSs as GSMPs, applied to DESs by Glynn in 1989 [27]. As detailed in the following sections, GSMPs satisfy all the requirements listed above. On the other hand, in contrast with less expressive state-based stochastic models (e.g., Markov or semi-Markov processes), GSMPs are general and powerful enough to model realistic power managed systems. Moreover, GSMPs provide both a rigorous denotational framework that drives system taxonomy and formal analysis, and an executable semantics compatible with event-driven simulation [52].

In the rest of this section, we first introduce a denotational model, a compositional rule, and an execution semantic for generic DESs, then we specialize our model for GSMPs. The combination of DESs with GSMPs is the major contribution of this section, and it provides a framework for analyzing a power-managed system from a formal standpoint.

#### A. Denotational Model

We denote by S the set of *physical states* (i.e., operation modes) of a system and by E the set of *events* that can trigger state transitions. All events compete to trigger state transitions: at each state, the event that comes first wins and is called the *triggering event*. The arrival times of triggering events are called *decision epochs*, since they are the time instants at which next states are chosen. State transitions are instantaneous.

We call annotated physical state a triple  $(s, \lambda, e)$ , where s is the physical state,  $\lambda$  the decision epoch at which s was entered, and e the event that triggered the transition. The sequence of annotated physical states visited by the system up to the *n*th decision epoch is its *physical trajectory* at n, denoted by  $x_n$ . In general, we use subscript n to denote the *n*th decision epoch  $(\lambda_n)$  and all quantities referred to that epoch. The set of all possible n-step trajectories is denoted by  $X_n$ .

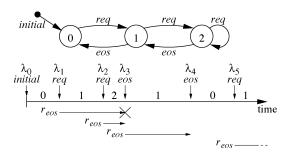

**Fig. 1.** State diagram and possible trajectory of a server with queue of length 2.

Clearly,  $x_n \in X_n$ . At decision epoch  $\lambda_0$ , the only feasible trajectory is empty:  $x_0 = \emptyset$ .

At decision epoch  $\lambda_{n+1}$ , the next state  $(s_{n+1})$  depends on the trajectory at time n, on current time  $(\lambda_{n+1})$  and on the triggering event  $(e_{n+1})$ . We call *initial state*  $s_0$  the state entered at decision epoch  $\lambda_0 = 0$  upon arrival of an implicit *initial* event.

We call the *next-state function* a black-box function F taking as input a trajectory, a decision epoch, and a triggering event and returning a target next state

$$s_{n+1} = F(x_n, \lambda_{n+1}, e_{n+1}).$$

According to our assumptions, if the input trajectory is empty, the decision epoch is  $\lambda_0 = 0$  and the triggering event is  $e_0 = initial$ , then the next-state function returns the initial state  $s_0$

$$s_0 = F(\emptyset, 0, initial).$$

In general, state transitions can be triggered by both *internal* and *external* events. We denoted by  $E_I$  and  $E_E$  the sets of internal and external events, respectively  $(E = E_I \cup E_E)$ . While the system has no direct control on external events, it directly generates internal events depending on its history, represented by the trajectory at current decision epoch  $\lambda_n$ . We call the *next-event function* a black-box function G that takes in input the current trajectory  $x_n$  and returns a candidate triggering event  $e \in E_I$  together with its residual time  $r_e$ .

$$(e, r_e) = G(x_n).$$

Function G is reevaluated at each decision epoch. If no external event arrives between  $\lambda_n$  and  $\lambda_n + r_e$ , then e will be the next triggering event  $(e_{n+1} = e)$  at decision epoch  $\lambda_{n+1} = \lambda_n + r_e$ . Otherwise, the state transition will be triggered by the external event at decision epoch  $\lambda_{n+1} < \lambda_n + r_e$ , and event e will be canceled. If no internal events are defined, or the system has entered a waiting state where it has to stay until a given external event occurs, then G returns  $(none, \infty)$ .

*Example 1:* Consider a server with a queue of length 2. The system has three states, corresponding to the number of enqueued processes. The first process in the queue represents

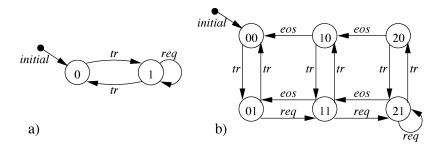

**Fig. 2.** (a) State transition graph of the two-state client of Example 2. (b) State transition graph of a system composed of the client of Example 2 and the server of Example 1.

the process being served. Triggering events are incoming requests (req) and end of services (eos). Incoming requests are external events, while ends of services are internal events. (See the equation at the bottom of the page.)

The residual service time can be computed based on  $x_n$ . For instance, assuming that the service time is one for all requests, the residual service time can be expressed as  $r_s = 1-t_{elapsed}$ , where the elapsed time  $t_{elapsed}$  is computed since the last decision epoch at which either state 0 was exited or a request was serviced (i.e., since the decision epoch at which the server started servicing the current request). The state diagram and a possible trajectory of the system are shown in Fig. 1.

DESs require the number of events occurring in a limited time period to be finite. This property is assumed to be verified by external (input) events, while it has to be guaranteed by next-event function  $G(x_n)$  for internal events. A finite number of events are allowed to occur simultaneously. Simultaneous events are treated as subsequent events with infinitesimal distance in time. This execution semantic is selfconsistent if and only if system evolution does not depend on the order simultaneous events are processed.

#### B. Compositional Model

Consider two interacting DESs A and B for which a representation is provided according to Section III-A. We model interaction by making A sensitive to (some of) the internal events of B and vice versa. We use superscripts (A) and (B) to refer to the two systems. We say that A and B interact with each other if either  $E_E^{(A)}\cap E_I^{(B)}\neq \varnothing$  or  $E_E^{(B)}\cap E_I^{(A)}\neq \varnothing$  or both.

*Example 2:* Consider a nonblocking client generating requests for the server of Example 1. The client has two states: active (1) and inactive (0). State transitions are triggered by an external event (tr). When active, the client issues service requests (represented by an internal event req) with exponentially distributed interarrival times, when inactive it does not. We denote by  $\exp(\mu)$  an exponentially distributed random variable with mean  $\mu$

$$S = \{0, 1\}$$

$$E_{I} = \{\text{req}\}$$

$$E_{E} = \{\text{tr}\}$$

$$s_{n+1} = F(x_{n}, \lambda_{n+1}, e) = 1 - s_{n} \quad \text{if } e = \text{tr};$$

$$= s_{n} \quad \text{if } e = \text{req};$$

$$= 0 \quad \text{if } e = \text{initial};$$

$$= s_{n} \quad \text{otherwise.}$$

$$(e, r_{e}) = G(x_{n}) = (\text{req}, \exp(\mu)) \quad \text{if } s_{n} = 1;$$

$$= (\text{none, } \infty) \quad \text{if } s_{n} = 0.$$

The client interacts with the server by means of event req. The state diagram of the client is shown in Fig. 2(a).

The representations of interacting systems can be merged to obtain a global representation of the entire system, with

$$S = S^{(A)} \times S^{(B)}$$

$$E = E^{(A)} \cup E^{(B)}$$

$$E_I = E_I^{(A)} \cup E_I^{(B)}$$

$$E_E = E - E_I$$

$$\begin{split} S &= \{0,1,2\} \\ E_I &= \{\mathrm{eos}\} \\ E_E &= \{\mathrm{req}\} \\ s_{n+1} &= F(x_n,\lambda_{n+1},e) = s_n + 1 & \text{if } e = \mathrm{req}, s_n < 2 \\ &= s_n - 1 & \text{if } e = \mathrm{req}, s_n < 2 \\ &= s_n - 1 & \text{if } e = \mathrm{eos}, s_n > 0 \\ &= 0 & \text{if } e = \mathrm{initial}; \\ &= s_n & \text{otherwise.} \\ (e,r_e) &= G(x_n) = (\mathrm{eos}, \mathrm{residual \ service \ time}) & \text{if } s_n > 0; \\ &= (\mathrm{none}, \infty) & \text{if } s_n = 0. \end{split}$$

Example 3: The system composed of the server of Example 1 (subsystem A) and the client of Example 2 (subsystem B) can be described as

$$S = \{(0,0), (0,1), (1,0), (1,1), (2,0), (2,1)\}$$

$$E_I = \{eos, req\}$$

$$E_E = \{tr\}.$$

The corresponding state transition graph is shown in Fig. 2(b).

Notice that the trajectories of two interacting systems at a given time  $\overline{t}$  may be composed of a different number of steps, since a system may not be sensitive to some of the triggering events of the other one. We denote by n the number of steps in the trajectory of the global system, and by  $n_A$  and  $n_B$  the number of steps in the trajectories of A and B, respectively. In general,  $n_A \leq n$  and  $n_B \leq n$ . The current state of the system is  $s_n = (s_{n_A}^{(A)}, s_{n_B}^{(B)})$ .

Suppose that event  $e_{n+1} = e \in E$  occurs at decision epoch  $\lambda_{n+1} = t$ , causing a new step to be added to the trajectory of the system:  $(s_{n+1}, \lambda_{n+1}, e_{n+1})$ . If event  $e \in$  $E^{(A)} \cap E^{(B)}$ , it causes state transitions in both subsystems at time t, bringing their trajectories to  $(s_{n_A+1}^{(A)}, \lambda_{n_A+1}, e_{n_A+1})$ and  $(s_{n_B+1}^{(B)}, \lambda_{n_B+1}, e_{n_B+1})$ . In this case, the relation between the annotated state of the system and those of the subsystems is the following:

$$s_{n+1} = \left(s_{n_A+1}^{(A)}, s_{n_B+1}^{(B)}\right)$$

$$\lambda_{n+1} = \lambda_{n_A+1} = \lambda_{n_B+1} = t$$

$$e_{n+1} = e_{n_A+1} = e_{n_B+1} = e.$$

Now consider the case of subsystem B being insensitive to event e (i.e.,  $e \notin E^{(B)}$ ). In this case, event e causes a state transition in subsystem A, but it does not cause any transition in B. Hence, time t is a decision epoch for A (and for the entire system) but it is not for B. The relation between the annotated state of the system and those of the subsystems becomes

$$s_{n+1} = \left(s_{n_A+1}^{(A)}, s_{n_B}^{(B)}\right)$$

$$\lambda_{n+1} = \lambda_{n_A+1} = t$$

$$e_{n+1} = e_{n_A+1} = e.$$

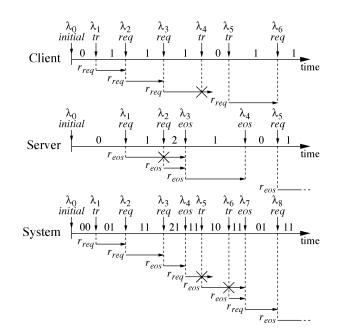

Example 4: A possible trajectory for our client-server system is shown in Fig. 3, together with the corresponding trajectories of the two subsystems. Notice that the decision epochs of the system are the union of those of all subsystems.

Fig. 3. Trajectory showing the interaction between a two-state client and a three-state server.

For instance, decision epoch  $\lambda_4$  in the system trajectory corresponds to decision epoch  $\lambda_3$  in the server trajectory, while it does not appear in the trajectory of the client.

The next-state function of the system (F) can be obtained from those of the subsystems in the following way:

$$s_{n+1} = F(x_n, \lambda_{n+1}, e_{n+1}) = \left(s^{(A)}, s^{(B)}\right)$$

where

$$\begin{split} s^{(A)} &= s^{(A)}_{n_A+1} = F^{(A)} \left( x^{(A)}_{n_A}, \lambda_{n+1}, e_{n+1} \right) & \text{if } e_{n+1} \in E^{(A)}; \\ &= s^{(A)}_{n_A} & \text{if } e_{n+1} \notin E^{(A)}, \\ s^{(B)} &= s^{(B)}_{n_B+1} = F^{(B)} \left( x^{(B)}_{n_B}, \lambda_{n+1}, e_{n+1} \right) & \text{if } e_{n+1} \notin E^{(B)}; \\ &= s^{(B)}_{n_B} & \text{if } e_{n+1} \notin E^{(B)}. \end{split}$$

Composition of next-event functions is even simpler

$$(e, r_e) = G(x_n) = \text{first} \left\{ G^{(A)} \left( x_{n_A}^{(A)} \right), G^{(B)} \left( x_{n_B}^{(B)} \right) \right\}$$

where first { } selects the event that occurs first, and the nextevent function of each subsystem is assumed to be evaluated at the last decision epoch for the subsystem.

*Example 5:* Next-state function F of the client-server system of Example 3 is represented by the state transition graph of Fig. 2(b). Its next-event function G is specified in the equation at the bottom of the page.

$$\begin{array}{ll} (e,r_e) = G(x_n) = \text{first} \left\{ (\text{eos, residual service time}), (\text{req}, \exp(\mu)) \right\} & \text{if } s_{n_A}^{(A)} > 0, s_{n_B}^{(B)} = 1; \\ = (\text{eos, residual service time}) & \text{if } s_{n_A}^{(A)} > 0, s_{n_B}^{(B)} = 0; \\ = (\text{req}, \exp(\mu)) & \text{if } s_{n_A}^{(A)} = 0, s_{n_B}^{(B)} = 1; \\ = (\text{none}, \infty) & \text{if } s_{n_A}^{(A)} = 0, s_{n_B}^{(B)} = 0. \end{array}$$

(D)

Fig. 4. Example of hierarchical interfaces.

In the following we use the symbol  $\odot$  to denote the composition of DESs. A system composed of subsystems A and B will be denoted by  $A \odot B$ . Composition is an associative and commutative operation: the resulting system does not depend on the order in which subsystems are composed. From a denotational point of view, however, the representation of the physical state of the system as an ordered n-tuple of the physical states of its subsystems depends on the order in which Cartesian products are performed.

The dynamics of a system consisting of interacting subsystems is the result of the composition of the dynamics of its components, each of which evolves based only on its own trajectory, that can be viewed as the projection of the system trajectory on the state and event sets of the subsystem. Subsystems have no visibility of the internal states of other subsystems, so that their evolution is a local (rather than global) phenomenon. Subsystems interact with each other only by means of some shared events.

On the other hand, the evolution of a generic DES may be based on its entire trajectory. If this is the case, the system cannot be obtained by means of composition. A system that can be expressed as the composition of interacting subsystems is called a *decomposable* system. DESs are not always decomposable.

1) Abstraction: In the previous section we said that two DESs A and B interact if there is at least an internal event (say, e) of a system (say, A) that is an external event for the other one (B). In symbols,  $e \in E_I^{(A)} \cap E_E^{(B)}$ .

Even if intersection of event sets is the key mechanism for interaction, it is impractical, since it imposes consistent naming conventions to be used when defining the event sets of each system: A and B communicate through event e if and only if it appears with the same name in  $E_I^{(A)}$  and  $E_E^{(B)}$ . If different names were used when defining the event sets of A and B, no interaction would be allowed. On the contrary, if the same name was carelessly assigned to different events in A and B, their interaction is enforced. In practice, in order to use intersection for modeling the interaction between DESs, consistent names should be assigned with all the event sets of the components of a complex system, thus avoiding the reuse of a component specification within different systems.

To overcome the above-mentioned drawbacks, we need to make composition independent of the names used within the specification of each subsystem. To this purpose, we associate an interface with each DES that maps local event names onto input and output ports to be used for compositional purposes. The specification of a system, together with its interface, is treated as a macro that can be repeatedly instantiated as a system component. When designing a system, each component has to be assigned with a unique name. Component ports are uniquely identified within a system by using the name of the instance as a prefix for the name of the port. Interaction between two components is explicitly specified by connecting their input–output ports.

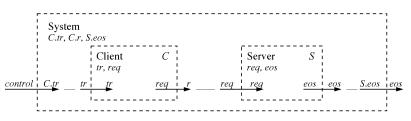

*Example 6:* Interfaces are used in Fig. 4 to represent the client–server interaction of our example system. Interfaces are represented as dashed boxes. The name of the macro is reported on the top-left corner, together with the list of local events. The name of the instance is reported on the top-right corner. Input and output ports are denoted by incoming and outgoing arrows. External and internal labels associated with each port represent the mapping between port names and local event names. Internal event req generated by the client C is made available at output port r. External event req is taken by the server S from input port req. Client–server interaction is represented by the connection between output port C.r and input port S.req

$$C.r \longrightarrow S.req.$$

Interfaces provide a mechanism for abstraction, in that they hide system specification focusing only on compositional properties. Moreover, interfaces hide all internal events that are not mapped to output ports.

*Example 7:* In Fig. 4, an interface is also associated with the entire system, viewed as a macro called *System*. Local events for the entire system are the events of its components that are mapped onto output ports and unconnected input ports, namely, *C.tr, C.r, S.*eos. The system interface maps *C.tr* onto primary input port control and *S.*eos onto primary output port eos, while it hides internal event C.r.

To provide additional flexibility to the compositional model, advanced port mappings can be introduced that combine and duplicate events. Event *combination* maps a set of events  $e_1, \ldots, e_N$  onto a single event e that occurs whenever one of the events in the set occurs. In practice, event combination provides a mechanism for simplifying the representation of equivalent events: a system that reacts to event e reacts to any of the events mapped to e.

Event *duplication* maps a single event e into multiple events  $e_1, \ldots, e_N$  that occur whenever event e occurs. Duplication represents fan-out points: an event needs to be duplicated to drive different components. Examples of event combination and duplication are provided in the following example.

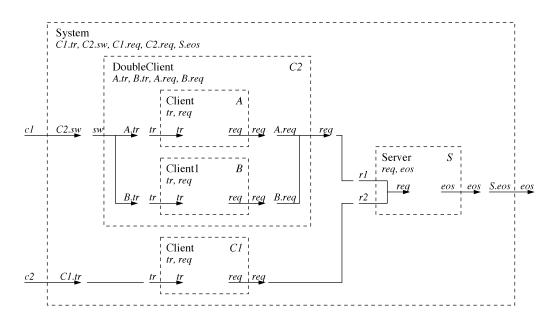

*Example 8:* Fig. 5 shows the hierarchical representation of a system composed of three independent clients issuing service requests for the same server. Leaf components are an instance (S) of the server in Fig. 5, two instances (C2.A and

Fig. 5. Example of abstraction.

```

void processEvent(trigEv) {

nextState = F(x,trigEv.time,trigEv.event); // chose next state

x = addStep(x,nextState,trigEv.time,trigEv.event); // update trajectory

if ((nextEv != NULL) && (nextEv != trigEv))

cancel(nextEv); // cancel candidate triggering event

nextEv = G(x); // generate new candidate triggering event

schedule(nextEv); // schedule candidate triggering event

n = n+1; // increment decision epoch counter

}

```

Fig. 6. Procedure for the event-driven execution of a generic DES model.

C1) of the client in Fig. 5, and an instance (C2.B) of a different client with initial state 1 (rather than 0). Components C2.A and C2.B are wrapped together to form a new macro (called DoubleClient) acting in its turn as a client whose interface exhibits a single input port (sw) and a single output port (req). The interface duplicates input event sw to control both subsystems, and combine their requests to generate output events on req. Since C2.A and C2.B start from opposite initial states and have simultaneous state transitions (triggered by the same external event), they are alternatively active. Hence, DoubleClient represents a bimodal workload controlled by an external event. As for the server, it has two input ports, r1 and r2, driven by C1 and C2. However, the two ports are combined by the interface in the same input event, making requests from the two clients indistinguishable for the server.

A global interface is provided for the system, hiding internal events C2.req and C1.req.

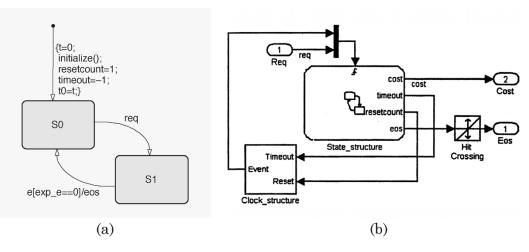

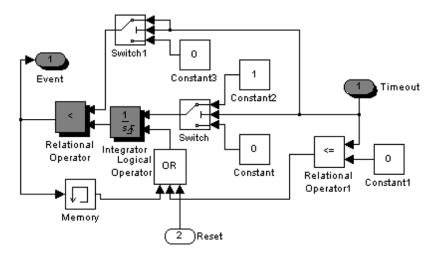

# C. Executable Model

An executable model for a DES is a model that provides executable specifications for next-state function F and next-event function G. Without loss of generality, we assume that the executable description is to be executed by an event-driven simulator developed in a procedural programming language. System specification is provided by implementing the processEvent function that is

called by the scheduler whenever a triggering event has to be processed. We also assume that the scheduler supports schedule and cancel functionalities to allow the system to add to the event queue the internal triggering events it generates and to remove from the queue triggering events overcome by external events. The pseudocode of a general processEvent procedure is shown in Fig. 6. Events are treated as structures containing both the event type and the occurrence time. The pseudocode refers to global variables of the system: the trajectory x, initialized to NULL, the candidate next triggering event nextEv, initialized to NULL, and the counter of decision epochs n, initialized to zero.

The triggering event is passed to processEvent as input parameter trigEv. Next-state function F is called to chose the target nextState for the current transition and the corresponding step is added to system trajectory x (using function addStep). If trigEv is an external event, then the internal candidate event scheduled at last iteration (stored in variable nextEv) needs to be removed from the event queue. This is done by invoking the cancel procedure. A new candidate event is then generated by next-event function G, stored in variable nextEv, and scheduled by calling function schedule. Finally, the counter of decision epochs n is incremented and execution control returned to the scheduler.

The system description is specialized by defining functions F and G that implement next-state and next-event functions, respectively.

```

nextState F(x, time, event) {

nextState = getNextState(x,event,time);

// chose next state

// get current state

s = getLastState(x);

deltaT = time - getEnterTime(x);

// evaluate elapsed time

for each event e {

// update clock readings

if (e is active in nextState) {

if ((e.clk == -1) || (e == event)) e.clk = 0;

else e.clk += deltaT * speed[s][e];

} else e.clk = -1;

}

return(nextState);

// return next state

}

```

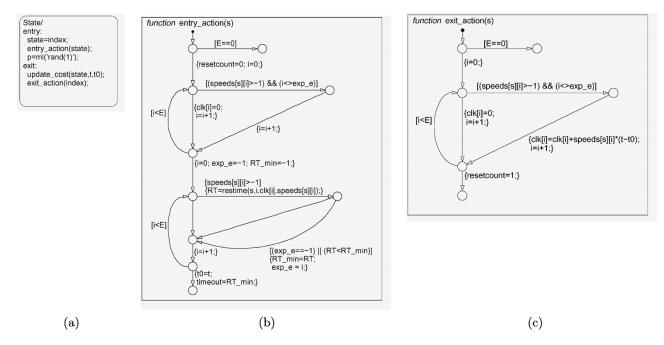

Fig. 7. Implementation of the next-state function of a GSMP.

```

nextEvent G(x) {

nextTime = INFTY;

for each active event e

r = getResTime(x,e);

// generate residual time for event e

if (r < nextTime) {</pre>

nextTime = r;

// update next time

nextEventName = e;

// update next event name

}

if (nextTime < INFTY)

nextEvent = newEvent(nextTime,nextEventName); // generate nextEvent

else nextEvent = NULL;

return(nextEvent);

// return nextEvent

}

```

Fig. 8. Implementation of the next-event function of a GSMP.

#### D. GSMPs

GSMPs are DESs with nondeterministic next-state and next-event functions based on conditional next-state probabilities and residual-time distributions, respectively.

Conditional next-state probability  $p(s': x_n, e_{n+1}, \lambda_{n+1})$ represents the probability of entering state s' at decision epoch  $\lambda_{n+1}$ . In general, such probability may depend on the entire history of the system, represented by its current trajectory  $x_n$ , by current decision epoch  $\lambda_{n+1}$ , and by the event  $e_{n+1}$  that triggered the current state transition. We introduce a random variable s, defined on the physical state set S, and we define a *next-state distribution*

$$\mathcal{F}(s:x_n, e_{n+1}, \lambda_{n+1}) = \operatorname{Prob}\{s' \le s: x_n, e_{n+1}, \lambda_{n+1}\}.$$

Distributions are more general than probability functions, in that they can be defined for both finite and infinite state spaces. As long as a family of next-state distributions is available, the evaluation of the next-state function reduces to the selection of the distribution associated with the current history and to the generation of a random next-state from such a distribution. This is done by the first row of the pseudocode of Fig. 7, where getNextState() returns a pseudorandom value from a distribution possibly dependent on the system trajectory x, on the triggering event event, and on the current time time.

Residual-time distributions are associated with each internal event. Whenever a physical state is (re)entered, residual times are generated for all internal events according to their distributions. The internal event with the smallest residual time is then chosen as candidate triggering event. Residual-time distributions may be conditioned to the history of the system, that is entirely represented by its trajectory up to the decision epoch at which current state has been entered. We denote by  $r_e$  the residual time of event e and by  $\mathcal{G}_e$  its distribution

$$\mathcal{G}_e(t:x_n) = Prob\{r_e \le t:x_n\}.$$

(1)

The general pseudocode of a next-event function based on residual-time distributions is shown in Fig. 8. Residual times are generated for all active events by calling the getResTime function. The event with the lowest residual time is then generated and returned to be scheduled as nextEvent.

Any system obtained by composition of GSMPs is a GSMP.

1) Clock Structure: Equation (1) provides the flexibility required to specify arbitrary GSMPs, since it allows residual-time distributions to depend on the trajectory of the system, that represents its entire history. However, expressing residual times as stochastic functions of  $x_n$  is often unnatural. In most cases, simpler data structures, carrying only partial information about the past, provide a more natural support for the specification of residual-time distributions. Such a natural support is provided by *clocks*, introduced by Glynn as part of the GSMP formalism [27].

A clock  $c_e$  can be associated with event e to measure the amount of time elapsed since a past decision epoch chosen as

a (temporary) reference for that event. At any decision epoch, the clock is either restarted (thus updating the time reference for the event) or incremented of a quantity proportional to the last state-holding time. In practice, the value of  $c_e$  (called *clock reading* and denoted by the same symbol used for the corresponding clock,  $c_e$ ) provides a partial view of the history of the system tailored on event e.

Clocks are associated with all internal events. For each state  $s \in S$ , a set  $E_I(s) \subset E_I$  of internal *active events* is defined. Active events for state s are those internal events that may trigger transitions from s. A *clock speed* v(s, e) is associated with each pair (s, e), with  $s \in S$  and  $e \in E_I(S)$ . Clock speed v(s, e) is used to scale the time spent in state s when updating  $c_e$ . Clock  $c_e$  is restarted either when event e becomes active (i.e., when a state s' is entered from state s, with  $e \in E_I(s')$  and  $e \notin E_I(s)$ ) or when event e occurs (i.e., when event e is the triggering event). Hence,  $c_e$  represents the time elapsed from the last occurrence/activation of event e. When event e is inactive, clock reading  $c_e$  is undefined.

Figs. 7 and 8 show the pseudocode of next-state and next-event functions of general GSMPs. Clock readings and speeds are treated as fields of the data structures used to represent events. When the event is inactive, the corresponding clock is set to conventional value -1. Since clock readings are updated whenever a state is exited, this is done by F(), which implements the next-state function. Notice that clock readings do not appear explicitly in function G() of Fig. 8, since they are passed to the genResTime function as fields of data structure *e*.

It is worth noting that clocks are not necessary. All clock readings at decision epoch  $\lambda_n$  could be computed from trajectory  $x_n$  and clock speeds v(s, e). In practice, clocks are nothing but event-specific partial views of the history of the system that can be used to simplify the specification of residual-time distributions. In most cases of practical interest, in particular, current clock readings and present state  $s_n$  retain all the information about the past that may affect the dynamic of the system, thus completely replacing trajectory  $x_n$ . In this case (1) can be rewritten as

$$\mathcal{G}_e(t:s_n, c_e) = Prob\{r_e \le t: s_n, c_e\}$$

(2)

and the pseudoalgorithms of Figs. 7 and 8 can be simplified accordingly.

In the following, we implicitly refer to GSMPs whose memory of the past is completely represented by clock readings and current state. We will show in the application section that this assumption does not limit the modeling power of GSMPs, allowing us to model with no approximation real-world systems with arbitrary event distributions.

2) Dealing With Infinite States and Infinite Events: The implementation of next-state and next-event functions described so far implicitly assume that both the event set and the state set are finite. If this not the case, infinite conditional distribution functions should be specified in order to fully describe the GSMP, and next-state and next-event functions would never exit their inner loops.

On the other hand, many real-world systems do have infinite states and infinite events. Consider, for instance, a digital system whose clock frequency can be dynamically controlled by an external command in a continuous interval from  $f_{\rm min}$  to  $f_{\rm max}$ . In this case, infinite input events are required to represent external commands, and infinite states are required to represent the operation state of the system. However, all external events representing dynamic control of the clock frequency differ only for a parameter that is the target clock frequency. Similarly, all active states of the system differ only for their operation frequency. This suggests that the entire set of events (states) could be represented as a single event (state) associated with a continuous parameter.

In general, we are interested in GSMPs with a finite set of (possibly parameterized) states, a finite set of (possibly parameterized) external events, and a finite set of (possibly parameterized) internal events. Parameterization provides an implicit finite representation of both finite and infinite (continuous or discrete) state/event sets, depending on the nature of the parameters.

We call *state class* (*event class*) any subset of states (events) represented by a unique parameterized state (event).

The actual state of the system is represented by its current state class and by the current configuration of all parameters associated with it. Similarly, any triggering event is represented by the event class it belongs to and by a unique configuration of the parameters associated with it. We also assume a unique clock to be associated to an entire event class, meaning that all events belonging to the same class share the same clock readings and that the clock is reset upon the occurrence of any event of the class.

The pseudocodes of next-state and next-event functions reported in Figs. 7 and 8 can be simply extended to handle parameterized states and events by representing parameters as fields of states and events structures. In particular, function getNextState that appears in Fig. 7 will return a random value according to a distribution depending not only on the current state and triggering event, but also on their parameters. In other words, the next-state distribution may be parameterized as well. Moreover, the returned value will be not only a value, but a data structure representing the destination state class together with the configuration of all parameters possibly associated with it.

As for the next event, function getResTime returns for each event class a residual time from a distribution that may depend on the configuration of the parameters associated with the current state. However, the residual-time distribution is unique for all events of class e. This means that the residual time returned by the function represents the first occurrence of any event of the class. The actual triggering event (i.e., the configuration of the parameters associated with the event class with the minimum residual time) will be selected by function newEvent, according to a given event distribution that is a property of the event class and that may depend on the residual time.

This implementation is consistent to the GSMP semantics, since both the residual-time distribution and the event distri-

bution for a given event class could in principle be obtained from the residual-time distributions of each event in the class

$$\mathcal{G}_{e}(t:s_{n},c_{e}) = Prob\{r \leq t:s_{n},c_{e}\}$$

$$= 1 - \prod_{\epsilon \in event \ class \ e} (1 - \mathcal{G}_{\epsilon}(t:s_{n},c_{e})) \ (3)$$

$$\mathcal{E}_{e}(e:s_{n},t) = Prob\{\epsilon \leq e:s_{n},t\}.$$

(4)

However, when dealing with infinite state sets, it is more practical and intuitive to directly specify  $\mathcal{G}$  and  $\mathcal{E}$  for the entire class.

We remark that in many cases, parametric states/events may be useful not only to provide a finite representation of infinite sets, but also to provide a compact representation of finite sets. This is the case, for instance, of a finite queue of length N, whose N states could be represented by a unique state class with an integer parameter ranging from zero to N.

#### E. System Taxonomy

The GSMP formalism introduced in the previous section allows us to describe very general systems. Since our goal is to model realistic DPM systems, we can make several simplifying assumptions to restrict the modeling space. Some of these assumptions were already mentioned and discussed in the previous sections, but we list them here for the sake of completeness. Namely, we assume GSMP models with:

- 1) a finite set of state classes;

- 2) a finite set of internal event classes;

- 3) a finite set of external event classes;

- next-state distributions depending only on the current state and on the triggering event;

- 5) clocks associated with each event class;

- residual-time distributions defined for each event class, depending only on the current clock readings and on the current state;

- event distributions defined for each event class as functions of the current state and of the triggering time.

In the following, we provide a classification of DESs directly induced by the proposed modeling framework. With respect to the state structure, a system is said to be:

- continuous state if there is at least a continuous parameter associated with one of its state classes;

- discrete state if there are no continuous parameters associated with state classes;

- *finite state* if none of the parameters associated with state classes may take an infinite set of values.

A similar classification is induced by the event set. A system is:

- continuous event if there is at least a continuous parameter associated with one of its event classes;

- *discrete event* if there are no continuous parameters associated with event classes;

- *finite event*, if none of the parameters associated with event classes may take an infinite set of values.

Depending on the number of internal events made observable from the external interface, a system/component may be *unobservable*, *partially observable*, or *totally observable*. Also, the system can be either *controllable* or *autonomous* depending on its sensitivity to external events.

A system composed of multiple interacting GSMPs is said to be *decomposable*, while it is *monolithic* otherwise. Notice that subsystems communicate only by means of events: the current state of a subsystem is not visible to other subsystems unless specific events are used to notify state changes. Hence, observability and controllability are key properties for intercomponent communication. The interactions between the subsystems of a decomposable GSMP can be represented by means of a dependency graph with nodes associated with GSMPs and directional arcs associated with event-passing communication. The dependency graph has an arc from component A to component B if an only if A is observable from B and B is controlled by A. Autonomous and unobservable components are represented as source and sink nodes in the dependency graph.

In general, GSMPs may be either *stationary* or *nonstationary* depending on whether conditional distributions depend on time or not. We are mainly interested in modeling stationary systems. As for the timing model, discrete events may occur at any point in time, provided that a finite number of events occur in a limited period. Hence, in general, events may be associated with continuous residual-time distributions. Nevertheless, slotted-time systems can be modeled by means of discrete residual-time distributions. A system has a *slotted-time* model if and only if all external and internal events are associated with discrete residual-time distributions with a common discretization step.

GSMP systems are inherently nondeterministic, since both next-event and next-state functions are specified by means of conditional probability distributions. However, deterministic decisions can be taken according to deterministic distributions, returning always the same value. A system is said to be *deterministic* if its model has only deterministic nextstate and residual-time distributions; it is said to be *nondeterministic* if its model has at least a nondeterministic distribution. A deterministic GSMP may have nondeterministic input events, but it cannot generate nondeterministic internal events.

A nondeterministic GSMP model is a *Markov* model if and only if all residual times have exponential distributions depending only on the present state.

*Example 9:* A variable-frequency digital system has a continuous state space if the clock frequency can take any value in a given range, while it has a finite state space if it can work at a finite number of clock frequencies. In both cases, the system is controllable if frequency adjustments are triggered by external events. The input events are either continuous or finite, according to the state space of the system. An unlimited first-in, first-out (FIFO) queue has an infinite discrete state set and a finite event set. A nonblocking client can be modeled as an autonomous system (since it is not sensitive to any external event). The simple server of Example 1 is completely observable, since it has a unique internal event (eos) that is made observable through an output port. A server with constant service time is deterministic, while a server with exponential service time is a Markov process.

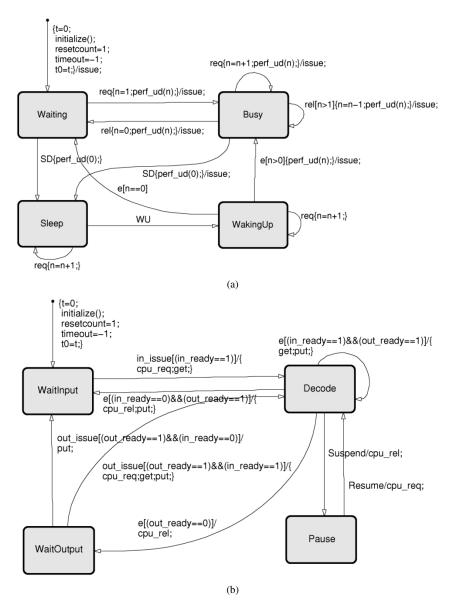

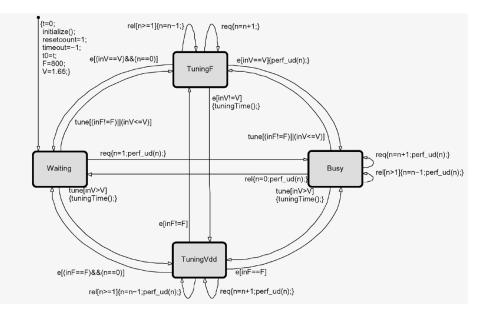

### F. DPM

DPM entails the interaction between (at least) a PMS and a PM. According to our taxonomy, any PMS has a controllable model, since it reacts to external events representing DPM commands issued by the PM. On the other hand, the PMS is usually (at least partially) observable from the PM, so that their interaction can be represented by a cyclic dependency graph. In most cases, the system is also controlled by a workload that can be modeled as an additional component. The model of the workload can be either autonomous or controlled in its turn by the system. For instance, a nonblocking client can be modeled as an autonomous GSMP, while a blocking client is controlled by the end-of-service events issued by the system. The workload may or may not be observable from the PM.

1) Design Metrics: The PM implements a control policy aimed at optimizing a system metric (e.g., average power consumption, energy per task, etc.) while meeting the constraints possibly imposed to other metrics (e.g., performance, quality of service, etc.). We call *metric* any function of the system trajectory that does not affect the evolution of the system. Hence, metrics are not conceived to be visible to system components. Rather, they can be used by the designer to evaluate/optimize the control policy implemented by the PM. According to an event-driven execution paradigm, metrics are evaluated (i.e., updated) only at decision epochs.

Any function of system metrics is also a system metric. Our definition of metrics is very general. Hence, we can use our framework to deal with system objectives and constraints of different types, including, but not limited to, average values, worst case values, variances, etc. The expressive power and flexibility of our approach stems from two specific factors. First, the simulation-based approach can incorporate arbitrary functions (for instance, we are not constrained to linearity as in the case of linear-programming optimization of Markov decision processes [53]). Second, the evaluation of the metrics does not affect system trajectory, so that metrics are not subject to constraints possibly imposed by the modeling framework.

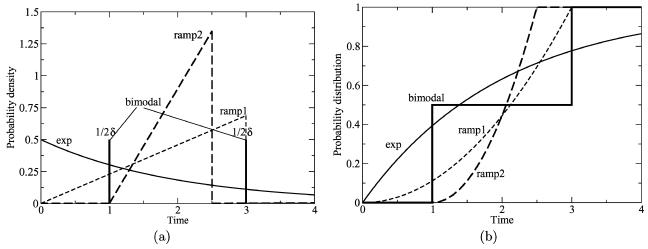

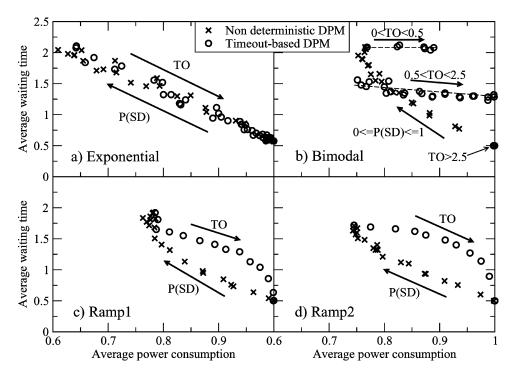

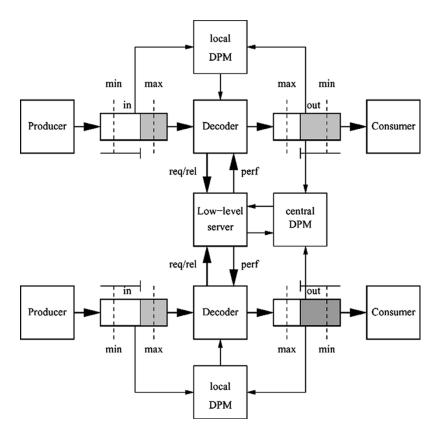

2) Optimum Control: The degrees of freedom exploitable for DPM are represented by the external events the PMS is sensitive to. Similarly, all information available for taking DPM decisions are provided by the observable internal events of all system components, possibly including the workload.