# Algorithms for Technology Mapping Based on Binary Decision Diagrams and on Boolean Operations

Frédéric Mailhot, Member, IEEE, and Giovanni De Micheli, Senior Member, IEEE

Abstract—We describe new algorithms and a new computer-aided design tool, called Ceres, for technology mapping of both completely specified and incompletely specified logic networks. The algorithms are based on Boolean techniques for matching, i.e., for the recognition of the equivalency between a portion of a network and library cells. A novel matching algorithm, using ordered binary decision diagrams, is described. It exploits the notion of symmetry for achieving higher computational efficiency. We also describe a matching technique that takes advantage of don't-care conditions, by means of a compatibility graph. We then present a strategy for timing-driven technology mapping, based on iterative improvement. Experimental results indicate these techniques generate good-quality solutions, and require short run times and limited memory space.

#### I. Introduction

Logic SYNTHESIS has been shown to be an effective means of designing logic circuits, especially for semicustom designs. The computer-aided synthesis of a logic circuit involves two major steps: the optimization of a technology-independent logic representation, using Boolean and/or algebraic techniques, and technology mapping. Logic optimization is used to modify the structure of a logic description, such that the final structure has a lower cost than the original [1], [2]. Logic optimization has traditionally been done before technology-dependent operations, and is assumed to have already taken place in the following.

Technology mapping is the task of transforming an arbitrary multiple-level logic representation into an interconnection of logic elements from a given library of elements. Technology mapping is a very crucial step in the synthesis of semicustom circuits for different technologies, such as sea-of-gates, gate arrays, or standard cells. The quality of the synthesized circuits, both in terms of area and performance, depends heavily on this step.

The technology-mapping transformation implies two distinct operations: recognizing logic equivalence be-

Manuscript received August 15, 1991; revised July 2, 1992. This work was supported in part by the National Science Foundation under Grant MIP-8719546; by DEC, AT&T, and NSF under a PYI award; by ARPA under Grant J-FBI-88-101; by the Natural Sciences and Engineering Council of Canada; and by the Quebec Fonds F.C.A.R. This paper was recommended by Associate Editor R. K. Brayton.

F. Mailhot is with Synopsys, Mountain View, CA 94043. This work was performed when the author was at Stanford University.

G. De Micheli is with the Center for Integrated Systems, Stanford University, Stanford, CA 94305.

IEEE Log Number 9209622.

tween two logic functions, and finding the best set of logically equivalent gates whose interconnection represents the original circuit. The first operation, called *matching*, involves equivalence checking and input assignment. Checking for logic equivalence can be expressed as a *tautology*, which has been proven to be coNP-complete [3]. Input assignment is also computationally complex. The second operation, called *covering*, involves finding an alternate representation of a Boolean network using logic elements that have been selected from a restricted set.

The two operations intrinsic to technology mapping, matching and covering, are computationally difficult. For this reason, several approaches to technology mapping have been pursued and implemented in research and commercial mapping tools. Rule-based technology mappers [4], [5] and heuristic algorithms have been proposed [6]–[11].

In this paper, we consider an algorithmic approach to the technology-mapping problem that extends the pioneering work of Keutzer on Dagon [8] and of Detjens [7] and Rudell [12] on MIS. To put our work in perspective, we briefly summarize their approach.

Most algorithmic approaches to technology mapping attack the problem by dividing it into sub-tasks. First, Boolean networks are partitioned into an interconnection of single-output sub-networks, with the property that each internal vertex has unit outdegree (i.e., fan-out). Then, each sub-network is decomposed into an interconnection of two-input functions (e.g., AND, OR, NAND, Or NOR). Each sub-network is modeled by a directed acyclic graph (DAG), called a *subject graph*. Finally, each subject graph is then covered by an interconnection of library cells, to produce the final circuit.

Finding a cover of a subject graph that optimizes area or timing is a difficult problem. Keutzer proposed to represent library functions by trees and to use a dynamic programming technique for optimal covering, based on fast tree matching algorithms. A similar approach was used by Rudell and Detjens [7], [12]. Note that the overall area (and timing) of a mapped network depends on the partitioning, decomposition, and covering tasks. However, good results were achieved by this approach, and extensions based on DAG matching presented by Detjens [7] did not show substantial improvements.

In this paper, we consider an approach to technology mapping that uses network partitioning and decomposition techniques similar to those used in [8], bit with dif-

ferent matching and covering algorithms. The covering algorithm described in this paper does not use a tree-based representation. Instead, it used Boolean matching techniques based on binary decision diagrams [13], [14] to recognize whether a logic function can be implemented by a library cell. The rationale for this choice is that the representation of single-output networks by trees makes cumbersome (and in some cases impossible) the efficient mapping of logic functions that have multiple occurrences of some variables into networks of gates that also have multiple occurrences of some variables (e.g., exclusive or's or majority functions). Boolean techniques uniformly support the description and matching of any single-output library cell, independent of cell functionality. In addition, Boolean matching techniques can take advantage of don't-care information.

This paper is organized as follows: We first give a brief overview of the overall approach to technology mapping. We describe partitioning, decomposition, and covering. We then present an algorithm for Boolean matching, followed by a description of the Boolean techniques used during matching. The Boolean techniques use both completely specified and incompletely specified logic functions. We then show how the *don't-care* sets are derived, and their use in technology mapping. We comment on performance-oriented mapping using iterative improvement techniques. Finally, we present implementation issues and results.

#### II. TECHNOLOGY MAPPING

In this section, we present the major tasks in technology mapping. We briefly overview partitioning and decomposition, and then present our network-covering algorithm.

#### 2.1. Partitioning

Partitioning is a heuristic step that transforms the technology-mapping problem for multiple-output networks into a sequence of sub-problems involving single-output networks. Partitioning is performed during the initial setup phase and as a part of the iterative improvement of a mapped network. We comment here briefly on the former case. The latter is described in Section IV.

The initial partitioning scheme is achieved by grouping vertices into single-output sub-networks, with the property that each outgoing edge of an internal vertex reconverges at or before the output vertex of the sub-network. Partitioning is also used to isolate the combinational portion of a network from the sequential elements and from the I/O's, where *ad hoc* techniques for mapping are used. Therefore, the circuit connections to the sequential elements are removed during the partitioning step.

After the partitioning step, the circuit is represented by a set of combinational circuits that can be modeled by subject graphs [8]. These graphs are single-output Boolean networks.

#### 2.2. Decomposition

Decomposition is applied on each subject graph after partitioning. It yields an equivalent subject graph, where each vertex is a base function, e.g., a two-input AND/OR/NAND/NOR function. Decomposition provides a mapping solution for libraries that include the base functions (i.e., almost all libraries). We assume in the sequel that the library under consideration includes the base functions. Decomposition also increases the granularity of the network, which is beneficial to the covering step.

#### 2.3. Network Covering

At this point, the logic circuit to be mapped has been partitioned into subject graphs  $[\Gamma_1, \dots, \Gamma_k]$ , that have been decomposed. We denote by  $\Gamma_f$  a subject graph whose single-output vertex is  $v_f$ . We consider here the covering of a subject graph  $\Gamma_f$  that optimizes some cost criteria (e.g., area or timing). For this purpose we use the notions of cluster and cluster function.

A cluster is a connected sub-graph of the subject graph  $\Gamma_f$ , having only one vertex with zero out-degree  $v_j$  (i.e., a single output). It is characterized by its depth (longest directed path to  $v_j$ ) and number of inputs. The associated cluster function is the Boolean function obtained by collapsing [1] the Boolean expressions associated with the vertices into a single Boolean function. We denote all possible clusters rooted at vertex  $v_j$  of  $\Gamma_f$  and their functions by  $\{\kappa_{j,1}, \cdots, \kappa_{j,n}\}$ .

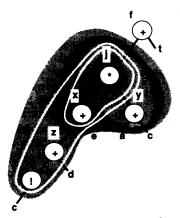

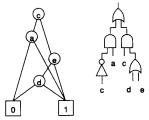

As an example, consider the Boolean network (after an AND/OR decomposition)

$$f = j + t$$

$$j = xy$$

$$x = e + z$$

$$y = a + c$$

$$z = \overline{c} + d.$$

There are six possible cluster functions containing the vertex  $v_i$  of the subject graph  $\Gamma_f$  (Fig. 1):

$$\kappa_{j,1} = xy$$

$\kappa_{j,2} = x(a+c)$

$\kappa_{j,3} = (e+z)y$

$\kappa_{j,4} = (e+z)(a+c)$

$\kappa_{j,5} = (e+\overline{c}+d)y$

$\kappa_{i,6} = (e+\overline{c}+d)(a+c).$

The covering algorithm attempts to match each cluster function  $\kappa_{j,k}$  to a library element. A cover is a set of clusters matched to library elements that cover the subject graph. A cover may optimize the overall area and/or timing. The area cost of a cover is computed by adding the cost of the clusters corresponding to the support variables in the cluster function  $\kappa_{j,k}$  to the cost of the library

Fig. 1. Graph of all possible covers of j.

```

/* Reached search depth: stop recursive expansion */

/* First recursion on vertex 'top' */

/* Copy equation defining top originally */

/* Copy original support variables of the equation defining top */

Start expanding the equation */

/* Covering of top is done */

/* Expand all input variables sequentially */

list is not empty {

/* Inputs need to be mapped for evaluating the best cost */

if (vertex(list) is not mapped) {

/* Map input if it's not mapped already */

cover(vertex(list), NULL, NULL, depth) }

if (vertex(list) is a primary input) skip this one

else if (any fanout(vertex(list)) does not reconverge at top) {

/* Do not try to expand primary inputs */

/* Do not expand non-reconverging multi-fanout vertices */

r(vertex(list),NULL,NULL,depth) }

/* Expand the current input variable */

/* Get the support of the equation for the current variable */

new_list = get_support_from(equation(vertex(list))

Augment the current list of support variables */

replace current list element by new_list

/* The current variable is eliminated into the current equation */

n = merge(equation, vertex(list))

/* Recurse on the new (expanded) equation */

/* Get back the input variable list before expan

Get next input variable */

ext element from(list)

Verify if current equation is equivalent to a library element */

if in library(top,equation, list)

```

Fig. 2. Algorithm for network covering.

element corresponding to the cluster  $\kappa_{j,k}$  under consideration. For each vertex  $v_j$  in a subject graph  $\Gamma_f$ , there is always at least one cluster function  $\kappa_{j,k}$  that matches, because the base functions (e.g., AND/OR) exist in the library and the network as decomposed accordingly in the initial step phase. When matches exist for multiple clusters, then for any tree-like decomposition the choice of the match of minimal area cost guarantees minimality of the total area cost of the matched sub-graph [8], [7].

The cost of the required inverters is also taken into account at this stage. Each vertex  $v_j$ , when mapped, is initially annotated with two library elements: the first one,  $C_{\rm ON}$ , gives the best cost for generating the on set  $f_j$ , and the second one,  $C_{\rm OFF}$ , gives the best cost for generating the off set  $f_j$ . As soon as variable j is used as an input to a gate that is being mapped, then  $C_{\rm ON}$  or  $C_{\rm OFF}$  is selected according to the required polarity of j. If the same variable j is needed at a later stage with the opposite polarity, then an inverter is automatically taken into account.

The timing cost of a cover can be computed in a similar way, by considering a constant delay model. The propagation delay through a cluster is added to the maximum of the arrival times at its inputs, to compute the local time at the vertex  $v_j$  [12]. When matches exist for multiple clusters, then for any tree-like decomposition the choice of the match of minimal local time guarantees minimality of the total timing cost of the matched sub-graph.

The covering algorithm is implemented by procedure cover shown in Fig. 2.

#### III. BOOLEAN MATCHING

We consider now the *matching* step. Matching is used during the covering stage, to verify if a particular cluster is logically equivalent to an element of the library. Matching can be formulated as checking the tautology between a given Boolean function, the *cluster function* introduced in Section 2.3, and the set of functions representing a li-

brary element, for any permutation of its variables. We also consider the polarity problem in connection with the matching problem, because they are closely interrelated in affecting the cost of an implementation. In addition, we exploit the *don't-care* conditions of the *cluster function* in the matching step.

We denote the cluster function by  $\mathfrak{F}(x_1, \dots, x_n)$ . It has n inputs and one output. We denote the polarity of variable  $x_i$  by  $\phi_i \in \{0,1\}$ , where  $x_i^{\phi_i} = x_i$  for  $\phi_i = 1$ ,  $x_i^{\phi_i} = \overline{x_i}$  for  $\phi_i = 0$ . We denote the don't-care set of the cluster function by  $\mathfrak{DC}(x_1, \dots, x_n)$ . We denote the library by  $\mathfrak{L}: \{g_1, \dots, g_m\}$ . Its elements g are multiple-input single-output functions. We define the matching problem as follows:

Given a cluster function  $\mathfrak{F}(x_1, \dots, x_n)$ , its don't-care set  $\mathfrak{DC}(x_1, \dots, x_n)$ , and a library element  $\mathfrak{G}(y_1, \dots, y_n)$ , find an ordering  $\{i, \dots, j\}$  and a polarity  $\{\phi_1, \dots, \phi_n\}$ , of the input variables of  $\mathfrak{F}$ , such that either equation (1) or (2) is true:

$$\mathfrak{F}(x_i^{\phi_i}, \cdots, x_i^{\phi_j}) = \mathfrak{G}(y_1, \cdots, y_n) \tag{1}$$

$$\overline{\mathfrak{F}}(x_i^{\phi_i}, \cdots, x_j^{\phi_j}) = \mathfrak{G}(y_1, \cdots, y_n)$$

(2)

for each value of  $(y_1, \dots, y_n)$  and each *care* value of  $(x_i^{\phi_i}, \dots, x_j^{\phi_j}) \notin \mathfrak{DC}$ ; i.e., equation (1) or (2) holds for all minterms in the *care* set.

If no such ordering and polarity exist, then the element  $\mathcal{G}$  does not match the *cluster function*  $\mathcal{F}$ . Furthermore, if no element in the library  $\mathcal{L}$ :  $\{\mathcal{G}_1, \dots, \mathcal{G}_m\}$  matches  $\mathcal{F}$ , then  $\mathcal{F}$  cannot be covered by the library  $\mathcal{L}$ . Note that when the library contains the base function, then any vertex v of the Boolean network has always at least one associated *cluster function* that is covered by a library element: the base function into which v is initially decomposed.

Let us define the NPN-equivalent set of a function  $\mathfrak F$  as the set of all the functions obtained by input-variable negation, input-variable permutation, and function negation [15]; we say that a function  $\mathfrak F$  matches a library element  $\mathfrak G$  when there exists an NPN-equivalent function that is tautological to  $\mathfrak G$  modulo the don't-care set.

For example, any function  $\mathfrak{F}(a,b)$  in the set  $\{a+b, \overline{a}+b, a+\overline{b}, \overline{a}+\overline{b}, ab, \overline{a}b, a\overline{b}, \overline{a}\overline{b}\}$  can be covered by the library element  $\mathfrak{G}(x_1, x_2) = x_1 + x_2$ . Note that in this example,  $\mathfrak{G}(x_1, x_2)$  has n = 2 inputs, and can match  $n! \cdot 2^n = 8$  functions [11].

#### 3.1. Use of Binary Decision Diagrams

1

The matching algorithms presented here are all based on Boolean operations. The advantage of using Boolean operations is that logic equivalence can be established regardless of the representation. For example,  $f_1 = ab + ac + bc$  and  $f_2 = a(b\overline{c} + \overline{b}c) + bc$  are logically equivalent, but structurally entirely different. Previous approaches used matching on trees or graphs representing the AND/OR (or equivalent) decomposition of a Boolean factored form (BFF). These algorithms could not detect logic equivalence, since no graph operation can transform the BFF of  $f_1$  into  $f_2$  without taking advantage of Boolean

properties. It is important to note that different representations of Boolean functions arise because factoring is not unique, and therefore different forms (e.g., factored forms, sum of products) can represent the same function. Therefore a covering algorithm recognizing matches independently from the representations can yield matches of better (or at worst equal) quality than those obtained by structural matching techniques.

Our alogrithms use binary decision diagrams (BDD's) as the basis for Boolean comparisons. BDD's are based on Shannon cofactors. A logic function f is iteratively decomposed by finding the Shannon cofactors of the variables of f[13], [14]. We use BDD's in the form proposed by Bryant, where a fixed ordering of the variables is chosen during Shannon cofactoring [14]. Elsewhere, these have been called ordered binary decision diagrams, or OBDD's for short [16]. Bryant also introduced procedures to reduce the size of BDD's. For the purposes of technology mapping, where a BDD representation of a portion of the circuit to map is to be used only once, the computational cost of reducing BDD's is comparable to the cost of doing one single comparison between unreduced BDD's. Therefore we exploit a simple way of comparing unreduced, ordered BDD's.

#### 3.2. A Simple Boolean Matching Algorithm

A Boolean match can be determined by verifying the existence of an assignment of the input variables such that the cluster function  $\mathfrak F$  and the library element  $\mathfrak G$  are a tautology. Tautology can be checked by using recursive Shannon cofactors [17]. The two Boolean expressions are recursively cofactored generating two decomposition trees. The two expressions are a tautology if they have the same logic value for all leaves of the recursion that are not in the don't-care set. This process is repeated for all possible ordering of the variables of  $\mathfrak F$ , or until a match is found.

The matching algorithm is described by the recursive procedure simple\_boolean\_match shown in Fig. 3, which returns TRUE when the arguments are a tautology for some variable ordering. At level n of the recursion, procedure simple\_boolean\_match is invoked repeatedly with arguments the cofactors of the nth variable of G and the cofactors of all the variables of F until a match is found. in which case the procedure returns TRUE. If no match is found, the procedure returns FALSE. The recursion stops when the arguments are constants; in the worst case, when all variables have been cofactored. The procedure returns TRUE when the corresponding values match (modulo the don't-care condition). Note that when a match is found, the sequence of the variables used to cofactor F in the recursion levels 1 to n represents the order in which they are to appear in the corresponding library element. The algorithm is shown in Fig. 3.

Note that in the worst case all permutations and polarities of the input variables are considered. Therefore, up to  $n! \cdot 2^n$  different ordered BDD's may be required for

```

simple_boolean_match(f,g,dc,var_list_f,var_list_g,which_var_g) {

/* If leaf value of DC = 1, local match */

if (dc = 1) return(TRUE)

/* If leaf value of f and g, matches if f == g */

if ( f and g are constant 0 or 1) return ( f = g )

gvar = pick_a_variable(var_list_g,which_var_g)

/* Choose the next variable from the list of variables of g */

remaining_var_g = get_remaining(var_list_g, which

/* Get list of unexpanded variables of g */

/* Starting pointer for variables of f */

which_var_f = 1

/* Try all unexpanded variables of f in turn */

while ( which_var_f < size_of(var_list_f)) {

/* Get next variable to expand */

fvar = pick_a_variable(var_list_f,which_var_f)

/* Undate the list of unexpanded variables of f */

remaining_var_f = get_remaining(var_list_f,which_var_f)

/* Find Shannon cofactor of f with (fvar = 0) */

f0 = shannon.decomposition(f,fvar,0)

f1 = shannon_decomposition(f,fvar,1)

/* Find Shannon cofactor of f with (fvar = 1) */

/* Find Shannon cofactor of g with (gvar = 0) */

g0 = shannon_decomposition(g_gvar_0)

/* Find Shannon cofactor of g with (gvar = 1) */

g1 = shannon_decomposition(g,gvar,1)

dc0 = shannon.decomposition(dc,fvar,0)

/* Find Shannon cofactor of dc with (fvar = 0) */

dc1 = shannon_decomposition(dc,fvar,1)

/* Find Shannon cofactor of dc with (fvar = 1) */

/* Verify that the cofactors of f and g */

if (simple_boolean_match(f0,g0,dc0,

/* are logically equivalent */

remaining var_f_remaining_var_g_which_var_g+1)

and simple_boolean_match(f1,g1,dc1,

remaining_var_f,remaining_var_g,which_var_g+1)) {

return(TRUE) }

else if (simple_book

/* If the previous check failed, */

ean.match(fl,g0,dc0,

remaining_var_f,remaining_var_g,which_var_g+1)

/* verify that f is equivalent to the complement of g */

and simple_boolean_match(f0,g1,dc1,

remaining_var_f,remaining_var_g,which_var_g+1)) {

return(TRUE) }

which var_f = which_var_f + 1

return(FALSE) }

```

Fig. 3. Simple algorithm for Boolean matching.

each match. Furthermore, all library elements with n or less inputs need to be considered in turn, since don't-care information might reduce the effective number of inputs. The worst-case computational complexity of the algorithm make it practical only for small values of n. Fortunately symmetry information can be used to reduce the search space significantly. Therefore the average computational complexity is much lower than the above bound. Experimental results have shown that Boolean matching is highly efficient, as shown in Section V.

## 3.3. Matching Completely Specified Functions

In this section we consider the matching problem for completely specified functions; i.e., we neglect the don't-care set. This simplification makes possible the use of some properties of Boolean functions that otherwise would not be usable. In particular, there are invariants in completely specified functions that are not in the presence of don't-cares. Unateness and symmetry are two such properties. We propose to use these two properties of Boolean functions to speed up the Boolean matching operation, without hampering the accuracy or completeness of the results. In the following sections, we introduce the two properties as key elements to search-space reduction. Matching techniques with don't-care conditions will be dealt with in Section 3.4.

#### 3.3.1) Search-Space Reduction

1

The simple Boolean matching algorithm presented in Section 3.2 is computationally expensive for two reasons. First n! permutations of n inputs are needed before two functions can be declared non-equivalent. Second, for each permutation, all  $2^n$  input polarities are required before logic equivalence is asserted. Since all input permu-

tations and polarities must be tried before two logic functions are declared different, then for any arbitrary n-input cluster function, this implies that  $n! \cdot 2^n$  comparisons are necessary in the worst case, i.e., whenever a match to a library element fails.

We now look into methods for reducing both the number of permutations and the number of polarities during the process of determining logic equivalence. The number of required polarities is reduced by taking the unateness property into account. The number of input permutations is reduced by using symmetry information. Note that the computational complexity is intrinsic to the Boolean matching problem; therefore, the worst-case number of comparisons is still  $n! \cdot 2^n$  for any arbitrary cluster function. However, we will show that the upper bound on complexity is related to the functionality of the library elements, and the most commercially available libraries are constituted of elements that imply much-smaller upper bounds. Therefore, for most cluster functions, the worstcase bound is much less than  $n! \cdot 2^n$ . In addition, the average cost of Boolean matching is much lower than the worst-case bound and it is shown experimentally to be competitive with other matching techniques.

## 3.3.2) Unateness Property

To increase the efficiency of the Boolean matching process, we take advantage of the fact that the polarity information of unate variables is not needed to determine the logic equivalence. Therefore we define a transformation  $\Upsilon$  that complements the input variables that are negative unate. For example, any function  $\Im (y_1, y_2)$  in the set  $\{y_1 + y_2, \overline{y_1} + y_2, y_1 + \overline{y_2}, \overline{y_1} + \overline{y_2}, y_1 y_2, \overline{y_1} y_2, y_1 \overline{y_2}\}$  can be represented by the set  $\{y_1 + y_2, y_1 y_2\}$ . Note that the polarity information must be kept for binate vari-

ables, where both the positive and negative phases are required to express F. By using the transformation T, we reduce the information required for the matching and therefore also reduce its computational cost.

As a result of using the unateness property, we redefine the matching problem as follows:

Given a cluster function  $\mathfrak{F}(x_1, \dots, x_n)$  and a library element  $\mathfrak{F}(y_1, \dots, y_n)$ , find an ordering  $\{i, \dots, j\}$  and a polarity  $\{\phi_k, \dots, \phi_l\}$  of the binate variables  $\{k, \dots, l\}$  of  $\mathfrak{F}$ , such that either (3) or (4) is true:

$$\mathbf{T}(\mathfrak{F}(x_{i}, \cdots, x_{k}^{\phi_{k}}, \cdots, x_{i}^{\phi_{i}}, \cdots, x_{j}))

\equiv \mathbf{T}(\mathfrak{G}(y_{1}, \cdots, y_{n}))$$

$$\mathbf{T}(\overline{\mathfrak{F}}(x_{i}, \cdots, x_{k}^{\phi_{k}}, \cdots, x_{i}^{\phi_{i}}, \cdots, x_{j}))

\equiv \mathbf{T}(\mathfrak{G}(y_{1}, \cdots, y_{n}))$$

(4)

The unateness property is also important for another aspect of search-space reduction. Since unate and binate variables clearly represent different logic operations in Boolean functions, any input permutation must associate each unate (or binate) variable in the cluster function to a unate (or binate) variable in the function of the library element. This obviously affects the number of input-variable permutations when assigning variables of the cluster function to variables of the library element. In particular, it implies that if the cluster function has b binate variables, then only  $b! \cdot (n - b)!$  permutations of the input variables are needed. Therefore, the worst-case computational cost of matching a cluster function with b binate variables is  $b! \cdot (n - b)! \cdot 2^b$ .

#### 3.3.3) Logic Symmetry

One additional factor can be used to reduce the number of required input permutations. Variables or groups of variables that are interchangeable in the cluster function must be interchangeable in the function of the library element. This implies that logic symmetry can be used to simplify the search space.

Variables are symmetric if they can be interchanged without affecting the logic functionality [18]. Techniques based on using symmetry considerations to speed up algebraic matching were also presented by Morrison in [11], in a different context. Reeves also used partial logic symmetry, as a filter during verification [19]. His technique uses BDD's to extract the Chow parameters [20], which can be used to express partial logic symmetry.

**Definition:** Logic symmetry is represented by the binary relation  $SR_{\mathfrak{F}}$  on the set of inputs  $\{x_1, \dots, x_n\}$  of  $\mathfrak{F}$ , where  $SR_{\mathfrak{F}} = \{\{x_i, x_j\} \mid \mathfrak{F}(x_1, \dots, x_i, x_j, \dots, x_n) \equiv \mathfrak{F}(x_1, \dots, x_j, \dots, x_i, \dots, x_n)\}$ . In the following, we write  $SR_{\mathfrak{F}}(x_i, x_j)$  to indicate that  $\{x_i, x_j\}$  belongs to  $SR_{\mathfrak{F}}$ .

The symmetry property of the completely specified functions is an equivalence relation (it is reflexive, symmetric, and transitive) [21], hence if  $\{x_i, x_j\}$  and  $\{x_i, x_k\}$  are two symmetry sets, then  $\{x_j, x_k\}$  is also a symmetry set. Being an equivalence relation, the symmetry property

1

of variables in logic equations implies a partition of the variables into disjoint subsets.

A symmetry set of a function  $\mathfrak F$  is a set of variables of  $\mathfrak F$  that belongs to the binary relation  $\mathfrak S \mathfrak R_{\mathfrak F}$ . Two variables  $x_i$  and  $x_j$  of  $\mathfrak F$  belong to the same symmetry set if  $\mathfrak S \mathfrak R_{\mathfrak F}(x_i,x_j)$  holds. Let us consider for example function  $\mathfrak F=x_1x_2x_3+x_4x_5+x_6x_7$ . The input variables of  $\mathfrak F$  can be partitioned into three disjoint sets of symmetric variables:  $\{x_1,x_2,x_3\}$ ,  $\{x_4,x_5\}$ , and  $\{x_6,x_7\}$ .

Symmetry sets are further grouped into symmetry classes. A symmetry class  $C_i$ ,  $i \in \{1, 2, \cdots \}$ , is an ensemble of symmetry sets with the same cardinality i and  $S_i = |C_i|$  is the cardinality of a symmetry class  $C_i$ . In the previous example, there are two symmetry classes:  $C_2 = \{\{x_4, x_5\}, \{x_6, x_7\}\}$  and  $C_3 = \{x_1, x_2, x_3\}$ , with  $S_2 = 2$ ,  $S_3 = 1$ . Note that all the other symmetry classes are empty, and therefore  $\forall_{i \neq 2,3} S_i = 0$ .

The symmetry properties are exploited in technology mapping as follows. Before invoking the mapping algorithm, the symmetry classes of each library element are calculated once. Symmetry classes are used in three different ways to reduce the search space during the matching phase. First, they are used as a filter to quickly find good candidates for matching. A necessary condition for matching a cluster function F by library element G is that both have exactly the same symmetry classes. Hence only a small fraction of the library elements need be checked by the computationally intensive Boolean comparison to see if they match the logic equation. The symmetry classes for each library element are calculated once before invoking the mapping algorithm.

Second, symmetry classes are used during the variable ordering. Once a library element G that satisfies the previous requirement is found, the symmetry sets of G are compared to those of G. The only assignments of variables belonging to symmetry sets of the same size can possibly produce a match. Since all variables from a given symmetry set are equivalent, the ordering of the variables within the set is irrelevant. This implies that the permutations need only be done over symmetry sets of the same size, i.e., symmetry sets belonging to the same symmetry class  $G_i$ . Thus the number of permutations required to detect a match is  $\Pi_{i=1}^q(S_i!)$ , where G is the cardinality of the largest symmetry set, and G is the cardinality of a symmetry class G.

For example, let us enumerate the permutations for matching functions  $\mathfrak{F}=y_1y_2(y_3+y_4)+y_5y_6$  and  $\mathfrak{G}=i_1i_2+(i_3+i_4)i_5i_6$ . Function  $\mathfrak{F}$  has one non-empty symmetry class,  $C_2(\mathfrak{F})$ , which contains three symmetry sets,  $\{y_1,y_2\},\{y_3,y_4\}$ , and  $\{y_5,y_6\}$ . We associate a name,  $\eta_i$ , with each of the symmetry sets:  $C_2(\mathfrak{F})=\{\{y_1,y_2\},\{y_3,y_4\},\{y_5,y_6\}\}=\{\eta_1,\eta_2,\eta_3\}$ ; i.e., we represent the pair of symmetric variables  $\{y_1,y_2\}$  by  $\eta_1$ , the pair  $\{y_3,y_4\}$  by  $\eta_2$ , etc. Similarly, function  $\mathfrak{F}$  has only one non-empty symmetry class,  $C_2$ , with cardinality  $S_2=3$ . We associate a name,  $\xi_j$ , with the symmetry sets of  $\mathfrak{F}$ :  $C_2(\mathfrak{F})=\{\{i_1,i_2\},\{i_3,i_4\},\{i_5,i_6\}\}=\{\xi_1,\xi_2,\xi_3\}$ . We then use the labels  $\eta$  and  $\xi$  to represent the different permutations of

symmetry sets. The cardinality of the symmetry class  $C_2$  is  $S_2 = 3$ , and therefore there are  $S_2! = 6$  possible assignments of symmetry sets of  $\mathcal{F}$  and  $\mathcal{G}$ :

$$(\eta_1, \, \xi_1), \, (\eta_2, \, \xi_2), \, (\eta_3, \, \xi_3)$$

$$(\eta_1, \, \xi_1), \, (\eta_2, \, \xi_3), \, (\eta_3, \, \xi_2)$$

$$(\eta_1, \, \xi_2), \, (\eta_2, \, \xi_1), \, (\eta_3, \, \xi_3)$$

$$(\eta_1, \, \xi_2), \, (\eta_2, \, \xi_3), \, (\eta_3, \, \xi_1)$$

$$(\eta_1, \, \xi_3), \, (\eta_2, \, \xi_1), \, (\eta_3, \, \xi_2)$$

$$(\eta_1, \, \xi_3), \, (\eta_2, \, \xi_2), \, (\eta_3, \, \xi_1).$$

Only the last assignment, where the variables of  $\mathcal{F}$  and  $\mathcal{G}$  are paired as  $\{\{y_1, y_2\}, \{i_5, i_6\}\}, \{\{y_3, y_4\}, \{i_3, i_4\}, \{i_3, i_4\}\}, \{\{y_5, y_6\}, \{i_1, i_2\}\},$  make functions  $\mathcal{F}$  and  $\mathcal{G}$  logically equivalent.

The third use of symmetry classes is during the Boolean comparison itself. Boolean comparisons are based on iterative Shannon cofactoring. Without symmetry considerations, for an n-input function  $\mathfrak{F}$ , up to  $2^n$  cofactors are needed. But since variables of a symmetry set are freely interchangeable, not all  $2^n$  cofactors are different. For example, given F = abc, where  $\{a, b, c\}$  are symmetrical, then the cofactor of  $\{a = 0, b = 1, c = 0\}$  is equivalent to the cofactor of  $\{a = 1, b = 0, c = 0\}$ . In general, for a symmetry set containing m variables, only m + 1 cofactors are different (corresponding to  $0, 1, \dots, m$  variables set to 1). Assuming the n variables of  $\mathfrak{F}$  are grouped into k symmetry sets of size  $n_1, \dots, n_k$  (where  $\sum_{i=0}^k n_i = n$ ), then the number of needed cofactors is  $\prod_{i=0}^k (n_i + 1) \leq 2^n$ .

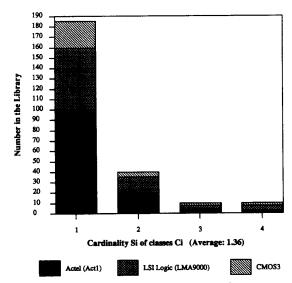

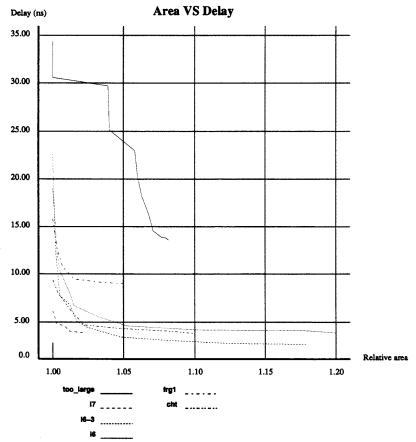

Although in the worst case logic equations have no symmetry at all, our experience with commercial standard cells and (programmable) gate array libraries shows that the library elements are highly symmetric. We computed the symmetry classes  $C_i$  of every element of three available libraries (CMOS3, LSI Logic, and Actel), and established the cardinality  $S_i$  of each symmetry class  $C_i$  extracted. We found that the average cardinality  $\overline{S}_i$  of all the symmetry sets of the library cells in the three libraries is less than 2, as shown in Fig. 4. Therefore, the number of permutations  $\Pi_{i=1}^q(S_i!)$  on the average is close to 1.

Unateness information and symmetry classes are used together to further reduce the search space. Unate and binate symmetry sets are distinguished, since both unateness and symmetry properties have to be the same for two variables to be interchangeable. Thus  $S_i = S_i^u + S_i^b$ , where  $S_i^u$  is the number of sets of cardinality i made of unate variables,  $S_i^b$  is the number of sets of cardinality i made of binate variables. This further reduces the number of permutations to  $\prod_{i=1}^q S_i^{u}! \cdot S_i^b! = \prod_{i=1}^q S_i^{u}! \cdot (S_i - S_i^u)! \prod_{i=1}^q S_i! \cdot (S_i - S_i^u)! \cdot (S_i - S_i^u)! \cdot (S_i - S_i^u)!$  Boolean comparisons have to be made in order to find a match.

As an example, in the Actel library act1, the worst case

Fig. 4. Distribution of symmetry classes  $C_i$ .

occurs for the library element  $MXT = d_0c_1c_3 + d_1\bar{c}_1c_3 + d_2c_2\bar{c}_3 + d_3\bar{c}_2\bar{c}_3$ , where  $S_1 = 7$ , and  $S_1^u = 4$ . In that case,  $4! \cdot 3! \cdot 2^3 = 1152 \ll 7! \cdot 2^7 = 645$  120, where  $7! \cdot 2^7$  represents the number of comparisons needed if no symmetry information is used.

Procedure boolean\_match, a variation on procedure  $simple\_boolean\_match$ , is shown in Fig. 5. It incorporates the symmetry information to reduce the search space: permutations are done only over symmetry sets of the same size. In addition, symmetry sets of unate and binate variables are separated into distinct classes  $C_i^u$  and  $C_i^b$ . Then only symmetry sets with the same unateness property are permuted.

## 3.3.4) Determination of Invariant Properties

Unateness and logic symmetry are the two invariant properties we utilize for search-space reduction during Boolean matching. Since cluster functions represent arbitrary portions of Boolean networks, we preprocess every cluster function to detect possible simplification before the unateness of symmetry properties are extracted.

In particular, the preprocessing step recognizes and eliminates vacuous variables. Recall that an equation  $\mathfrak F$  is vacuous in a variable  $v_i$  if the equation can be expressed without the use of  $v_i$  [22]. Vacuous variables are detected by checking if  $\mathfrak F_{v_i} \equiv \mathfrak F_{v_i}$  for any given variable  $v_i$ . When this condition is true, variable  $v_i$  is vacuous, and therefore does not influence the value of  $\mathfrak F$ . In that case, we arbitrarily set variable  $v_i$  to 0 or to 1, to simplify the expression of function  $\mathfrak F$ .

Unateness is the first property to be extracted from Boolean functions. For efficiency reasons, the unateness determination is done in two successive steps. The first step consists of considering a decomposition of the function  $\mathfrak F$  into base functions represented by a leaf-DAG and detecting the phase of each variable of  $\mathfrak F$ . The phase de-

```

n.match(f,g,f.symmetry.sets,g.sym

if ( f and g are constant 0 or 1) {

/* If leaf value of f and g, matches if f == g */

return (f = g)

if (f.symmetry.sets is empty) {

/* All variables of current symm set are as

f_symmetry_sets = get_next_f_sym

Get next symm set in the list */

symmetry_size = size_of(f_sym

while ( symmetry sets of g with

/* Try all symm sets of g with the same size (recursion) */

size symmetry_size have still to be tried) {

g_symmetry_sets = get_next_available_set(g_symmetry_size)

boolean.match(f,g,f_symmetry_sets,g_symmetry_sets)

if ( it is a match) return(TRUE)

clac return(FALSE) } }

fvar = pick_a_variable(f_symmetry_sets)

/* Select variables from compatible symm sets for decomp */

gvar = pick_a_variable(g_symmetry_acts)

f0 = shannon_decomposition(f,fvar,0)

/* Find Shannon cofactor of f with (fvar = 0) */

f1 = shannon_decomposition(f, fvar, 1)

/* Find Shannon cofactor of f with (fvar = 1) */

g0 = shannon.decomposition(g,gvar,0)

/* Find Shannon cofactor of g with (gvar = 0) */

g1 = shannon_decomposition(g,gvar,1)

/* Find Shannon cofactor of g with (gvar = 1) */

if ((boolean_match(f0,g0,f_symmetry_sets,g_sym

tch(fl,gl,f.symmetry.sets,g.symmetry.sets) {

return(TRUE)

/* Verify that the cofactors of f and g are equivalent */

else if ((boolean_match(f0,g1,f_symmetry_sets,g_syr

and (boolean_match(fl,g0,f_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_symmetry_sets,g_sym

return(TRUE)

Verify that f and is equivalent to the complement of g */

else return(FALSE) {

```

Fig. 5. Algorithm for fast Boolean matching.

tection proceeds as follows. Starting at the root of the leaf-DAG representing function  $\mathfrak{F}$ , a token representing a positive phase is propagated depth first toward the leaves of the DAG. When a vertex corresponding to a negative unate function is traversed, the phase of the token passed down is complemented. Each variable reached during the graph traversal is annotated with the phase of the current token. The traversal of the leaf-DAG takes at most 2n-1 steps, where n is the number of leaves: since the network is decomposed into 2-input gates, then each level in the levelized DAG has at most half the number of vertices of the previous level. Therefore, such a DAG with n inputs has at most  $n + n/2 + n/4 + \cdots + 1 = \sum_{i=0}^{\infty} n/2^i - \sum_{i=0}^{\infty} 1/2^i + 1 = 2n-2+1 = 2n-1$  vertices.

All variables used in only one phase are necessarily unate. However, the first operation can falsely indicate binate variables, because the algorithm relies on structure, not on Boolean operations. In the second step, the unateness property of the remaining variables (those the first step labeled as binate) is detected verifying implications between cofactors [22]. The unateness property of these possibly binate variables is detected by verifying if  $\mathfrak{F}_{v_i} \Rightarrow \mathfrak{F}_{v_i}$  (negative unate variable) or if  $\mathfrak{F}_{v_i} \Rightarrow \mathfrak{F}_{v_i}$  (positive unate variable). If neither implication is true, then variable  $v_i$  is binate.

Once the unateness information has been determined, symmetry properties are extracted. The transformation  $\Upsilon$ , presented in Section 3.3.2, is applied to ensure that symmetry will be detected between unate variables regardless of phase. We detect that two variables are symmetric simply by verifying that  $SR_{\pi}(x_i, x_j)$  is true for that pair of variables. Since the symmetry property is transitive, when variable  $v_i$  is symmetric to  $v_j$ , and  $v_j$  to  $v_k$ , the symmetry of  $v_i$  and  $v_k$  is established without further verification.

Γ

Similarly, if  $v_i$  is symmetric to  $v_j$ , and  $v_j$  is not symmetric to  $v_k$ , then  $v_i$  is not symmetric to  $v_k$ . As a result, when two variables are symmetric, the symmetry relations to the second variable are identical to those of the first variable, and do not need to be established through additional verification. This implies that it is not always necessary to verify all pairs of variables for symmetry. All pairs of variables must be processed (by verifying that  $\Re_{\mathfrak{F}}(x_i, x_j)$  is true) only when there is no symmetry. This is the worst case, and n(n-1)/2 swaps must be done, where n is the number of equal inputs to the equation. When a function is completely symmetric, i.e., when all inputs to a function  $\mathfrak{F}$  are symmetric, then only n-1 swaps are needed.

The unateness property is used to reduce the number of swaps needed. Assuming b out of the n input variables are binate, then at worst b(b-1)/2 + (n-b)(n-b-1)/2 swaps are required. At best, n-2 swaps are needed, when both binate and unate variables are maximally symmetric. In order to verify that swapping two variables  $\{v, v_j\}$  leaves  $\mathfrak{F}$  unchanged, it is sufficient to verify that  $\mathfrak{F}_{v_iv_j} \equiv \mathfrak{F}_{v_iv_j}$ . As in the first step, this is done using Shannon cofactors, and a single ordering (and polarity) of the variables is sufficient.

Since the polarity information is relevant to binate variables, two swaps have to be done for each pair of binate variables, one swap for each polarity of one of the two variables. Again, Shannon cofactors are used to check if the two instances of the equation are the same, and, as in the first step, only variable ordering is used.

From an implementation standpoint, symmetry classes are established once for each library element. Each library element is then inserted into a database, with its symmetry sets used as the key. Library elements with the same symmetry sets are further grouped by functionality (e.g.,

$G_1 = y_1$ ,  $y_2$  and  $G_2 = y_1 + y_2$  are grouped together in a new entry 3C of the database corresponding to functions of two equivalent, unate inputs).

#### 3.4. Matching Incompletely Specified Functions

The importance of the use of don't-care conditions in multiple-level logic synthesis is well recognized [23]. We consider here don't-care conditions that are specified at the network boundary and that arise from the network interconnection itself [24]. Since the topology of the network changes during the covering stage, don't-care conditions are dynamically computed.

Therefore a technology-mapping algorithm that exploits don't-care sets must involve two tasks: 1) computing and updating local don't-care sets and 2) using the don't-care information to improve the equality of the mapped circuit. We present the use of don't-care sets first and we defer their computation to Section 3.4.2.

We have considered two approaches to using don't-care conditions in technology mapping. The former uses Boolean simplification before matching a function to a library element. The latter merges simplification and matching in a single step and it is motivated by the following rationale: don't care conditions are usually exploited to minimize the number of literals (or terms) of each expression in a Boolean network. While such a minimization leads to a smaller (and faster) implementation in the case of pluri-cell design style [25] (or PLA-based design), it may not improve the local area and timing performance in a cell-based design. For example, cell libraries exploiting pass transistors might be faster and/or smaller than other gates having fewer literals. A passtransistor-based multiplexer is such a gate. Assuming a function is defined by its on set F and its don't-care set DC:

$$\mathfrak{F} = (a + b)c$$

$$\mathfrak{D}\mathfrak{C} = \overline{b}\overline{c}$$

then (a + b)c is the representation that requires the least number of literals (3), and the corresponding logic gate is implemented in CMOS pass-transistor logic by 6 transistors. On the other hand,  $a\bar{b} + bc$  requires one more literal (4), but it is implemented by only 4 pass transistors, and it is likely to be faster.

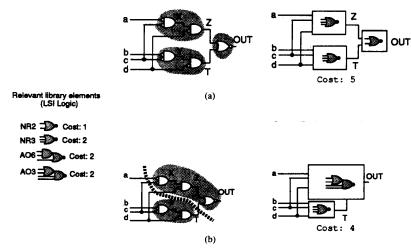

A second example, taken from the MCNC benchmark majority, is also representative of the uses of don't-cares during matching (Fig. 6). In that example, using don't-cares yields better matches, and gives an overall lower cost for the resulting circuit: the cluster function out =  $\overline{T}a + \overline{T}c + \overline{T}d$  has an associated don't-care set  $\mathfrak{DC} \supset Td + Tc$ , and can be reexpressed as out =  $(\overline{c}d(\overline{a} + T)$ . The two expressions have the same number of literals (4), and are therefore equally likely to be chosen by a technology-independent simplify operation (which relies on literal count). But only one of the two exists in the library, and that match is essential in finding the best overall cost.

These examples show that applying Boolean simplifi-

Γ

cation before matching may lead to inferior results, as compared to merging the two steps into a single task. For this reason, we directly use *don't-care* sets in the Boolean matching step to search for the best implementation in terms of area (or timing).

## 3.4.1) Compatibility Graph

Boolean matching that incorporates the *don't-care* information can be done using the simple matching algorithm presented in Section 3.2. Unfortunately, when *don't care* conditions are considered, the *cluster function*  $\mathfrak{F}$  cannot be uniquely characterized by a symmetry set. Therefore the straightforward techniques based on symmetry sets presented in the previous section no longer apply. The simple matching algorithm would require in the worst case  $n! \cdot 2^n$  variable orderings, each ordering requiring up to  $2^n$  Shannon cofactorings. Therefore the algorithm is likely to be inefficient.

Another straightforward approach is considering all the completely specified functions  $\mathfrak{I}$ C that can be derived from  $\mathfrak{F}$  and its don't care set  $\mathfrak{DC}$ , by adding to  $\mathfrak{F}$  all subsets of  $\mathfrak{DC}$ . In this case, the symmetry sets can be used to speed up matching. Unfortunately, there are  $2^N$  possible subsets of  $\mathfrak{DC}$ , where N is the number of minterms in  $\mathfrak{DC}$ . Therefore this approach can be used only for small don't-care sets. For large don't-care sets, a pruning mechanism must be used to limit the search space.

We consider in this section a formalism that allows us to efficiently use don't-care sets in matching. We first introduce a representation of n-variable functions that exploits the notion of symmetry sets and NPN equivalence and that can be used to determine matches while exploiting the notion of don't-care conditions. For a given number of input variables n, let G(V, E) be a graph whose vertex set V is in one-to-one correspondence with the ensemble of all different NPN-equivalent classes of functions. The edge set  $E = \{(v_i, v_j)\}$  of the graph G(V, E) denotes the vertex pairs such that adding a minterm to a function included in the NPN class represented by  $v_i$  leads to a new function belonging to the NPN class represented by  $v_j$ . Such a graph G(V, E) for n = 3 is shown in Fig. 7.

Each vertex  $v_i$  in the graph is annotated with one function  $\theta_i$  belonging to the corresponding NPN-equivalent class of  $v_i$ . The function  $\theta_i$  is chosen arbitrarily among the members of the NPN-equivalent class that have the least number of minterms. For example, vertex 4 in Fig. 7 corresponds to functions  $\{abc + \overline{a}b\overline{c}, \overline{a}bc + ab\overline{c}, \overline{a}bc + \overline{a}b\overline{c}\}$  and their complements. The representative function  $\theta_4$  for vertex 4 is  $\{abc + \overline{a}b\overline{c}\}$ , but could be any of the four functions just enumerated. The set of functions  $\theta_i$  is used as the basis for establishing relations between vertices  $v_i$ . Each vertex  $v_i$  is also annotated with the library elements that match the corresponding function  $\theta_i$ .

The graph G(V, E) is called a matching compatibility graph, because it shows which matches are compatible

Fig. 6. Mapping the majority MCNC benchmark with LSI Logic library elements. (a) Mapping without DC. (b) Mapping with DC.

Fig. 7. Matching compatibility graph for 3-variable Boolean space. Note that no path exists between vertex 4 and vertices 8, 11, and 13.

with the given function and a don't-care set. Note that the size of the compatibility graph is small for functions of 3 and 4 variables, where there are 14 and 222 different NPNequivalent functions respectively [15], representing the 256 and 65 536 possible functions of 3 and 4 variables. Unfortunately, for functions of more than 4 variables, the number of NPN-equivalent functions grows very quickly (functions of 5 and 6 variables have 616 126 and  $\approx$  2  $\times$ 10<sup>14</sup> respectively [20]), although it is very sparse in terms of the vertices corresponding to library elements. At present, we have implemented techniques for technology mapping using don't-care conditions for cluster functions of at most 4 variables. Although libraries contain cells with more than 4 inputs (see Table I), we found from experimental results of mapped networks that the majority of the library elements used have 4 or less variables (see Table II for the distribution of the number of inputs of cells used for mapping 30 benchmarks). Therefore, it is a reasonable implementation decision to use don't-cares only for cluster functions whose fan-in is less than or equal to 4.

Γ

TABLE I Number of k-input Cells Included in the Full act 1 and the LSI Logic Libraries

|                  | Cells | ber of<br>in the<br>rary | Percentage of Total |       |  |

|------------------|-------|--------------------------|---------------------|-------|--|

| Number of Inputs | act1  | LSI                      | act1                | LSI   |  |

| 1                | 1     | 2                        | 0.1%                | 2.5%  |  |

| 2                | 8     | 12                       | 1.1%                | 14.8% |  |

| 3                | 47    | 22                       | 6.7%                | 27.2% |  |

| 4                | 210   | 20                       | 30.0%               | 24.7% |  |

| 5                | 285   | 6                        | 40.7%               | 7.4%  |  |

| 6                | 128   | 8                        | 18.3%               | 9.9%  |  |

| 7                | 21    | 0                        | 3.0%                | 0.0%  |  |

| 8                | 1     | 9                        | 0.1%                | 11.1% |  |

| 11               | 0     | 2                        | 0.0%                | 2.5%  |  |

TABLE II

Number of k-input Cells Used in Mapping 30 Benchmarks with the Full act1 and the LSI Logic Libraries. A Depth of 5 was Used During Covering

|                  |       | of Cells<br>sed | Percentage of Total |       |  |

|------------------|-------|-----------------|---------------------|-------|--|

| Number of Inputs | act 1 | LSI             | actl                | LSI   |  |

| 1                | 305   | 2110            | 2.9%                | 12.9% |  |

| 2                | 3176  | 6816            | 30.7%               | 41.8% |  |

| 3                | 2998  | 2705            | 29.0%               | 16.6% |  |

| 4                | 3685  | 4583            | 35.6%               | 28.1% |  |

| 5                | 182   | 103             | 1.8%                | 0.6%  |  |

| 6                | 0     | 3               | 0.0%                | 0.0%  |  |

For functions of 4 variables and less, the compatibility graph is constructed once and annotated with the library elements. Each vertex  $v_i$  in the graph is also annotated with the paths  $p_{ij}$  from the vertex  $v_i$  to a vertex  $v_j$  corresponding to library element  $G_k \in \mathcal{L}$ . The set of paths  $P_{i\mathcal{L}} = \{p_{i0}, p_{i1}, \cdots, p_{im}\}$  represents all the paths from vertex  $v_i$  to the vertices corresponding to library elements.

Each path represents the set of additional minterms differencing the function  $\theta_i$  corresponding to  $v_i$  from the function  $\theta_j$  of  $v_j$ , where  $v_j$  corresponds to a library element. Therefore, checking if a function  $\mathfrak{F}$  is logically equivalent (modulo the don't-care set  $\mathfrak{DC}$ ) to a library element  $\mathfrak{G}_k \in \mathcal{L}$  is the same as verifying that vertex  $v_i$  (corresponding to function  $\mathfrak{F}$ ) has some path  $p_{ik}$  to vertex  $v_k$  (corresponding to library element  $\mathfrak{G}_k$ ), such that the corresponding minterms are in the don't-care set  $\mathfrak{DC}$ .

Let us define  $\mathfrak{M}(v_i)$  as the number of minterms of the representative function  $\theta_i$  of vertex  $v_i$  in a given n- dimensional Boolean space, and the distance between two vertices  $v_i$  and  $v_i$  as  $\mathfrak{D}(v_i, v_i) = |\mathfrak{M}(v_i) - \mathfrak{M}(v_i)|$ .

Then the number of paths from vertex  $v_i$  to any other vertex (including itself) of the compatibility graph is  $2^{2^n - \mathfrak{M}(v_i)}$ . For a 4-variable compatibility graph, the total number of paths for the entire network is 375 522. This is reasonable from an implementation point of view, since each path is represented by 16 bits, and thus the entire set of paths occupies approximately 750 kilobytes. Note that in general not all paths need to be stored, since the elements of the library usually represent only a subset of all possible NPN-equivalent classes.

If we consider all possible combinations of minterms, the maximum number of paths  $|P_{ik}|$  between a vertex  $v_i$  and a library element  $v_k$  is

$$|P_{ik}| = {2^n - \mathfrak{M}(v_i) \choose \mathfrak{D}(v_i, v_k)} + {2^n - \mathfrak{M}(v_i) \choose 2^n - \mathfrak{M}(v_i) - \mathfrak{M}(v_k)}.$$

The first term of the expression for  $|P_{ik}|$  represents all the combinations of minterms that can make a function of  $\mathfrak{M}(v_i)$  minterms into a function of  $\mathfrak{M}(v_k)$  minterms, in an n-dimensional Boolean space. The second term of the expression represents the combinations of minterms that yield a function of  $2^n - \mathfrak{M}(v_k)$ , i.e., the complement of the functions computed for in the first part. Although this upper bound function grows exponentially, experimental results show that the actual number of paths between any pair of vertices is much smaller. For the 4-variable compatibility graph, the maximum number of paths between any two vertices is 384, corresponding to vertices  $v_i$  = abcd and  $v_i = abcd + \overline{a}(b\overline{d} + \overline{c}d)$ . Given that  $\mathfrak{M}(v_i) =$ 1 and  $\mathfrak{M}(v_i) = 5$ , it is clear that the actual number of paths is much smaller than the worst case of 4004 calculated with the above formula. This is due to the fact that not all combinations of added minterms will make function  $\theta_i$  logically equivalent to  $\theta_k$ . In some cases, it is even impossible to reach some library element  $v_k$  from vertex  $v_i$ . For example, in Fig. 7, vertex  $v_4$  cannot reach vertices  $v_8$ ,  $v_{11}$ ,  $v_{13}$ . In addition, some paths do not need to be recorded, because their head vertex does not correspond to a library cell.

The matching of a cluster function  $\mathfrak{F}$  to a library element is redefined in terms of the compatibility graph as follows. For cluster functions with no applicable don't-care set, only procedure boolean\_match is used to find the vertex  $v_{\mathfrak{F}} \in G(V, E)$  corresponding to the NPN-equiv-

Τ

alent class of cluster function F (without using DC). Since the graph represents all possible functions of 4 or less variables, then there exists a vertex in the graph which is NPN-equivalent to  $\mathfrak{F}$ . At the same time vertex  $v_{\mathfrak{F}}$  is found, the algorithm computes the transformation 3 representing the input ordering and polarity on the inputs and output such that  $\Im(\mathfrak{F}) = \theta_{\mathfrak{F}}$ . The transformation 3 is applied to the don't-care set DC, to generate a new expression,  $\mathfrak{I}(\mathfrak{D}\mathfrak{C})$ , consistent with the representative function  $\theta_{\mathfrak{F}}$  of  $v_{\mathfrak{F}}$ . There exists a match to the library cell  ${\mathfrak{F}}$  if there is a path in the graph G(V, E) from  $v_{\mathfrak{F}}$  to  $v_{\mathfrak{S}}$  (possibly of zero length) whose edges are included in the image 3(DC) of the don't-care set DC of F. It is necessary that don't care sets are transformed by the operator 3 before the path inclusion is checked, because paths in the compatibility graph are computed between representative functions  $\theta_i$ .

The algorithm for graph traversal is shown in Fig. 8. It is invoked with the vertex found by algorithm boolean\_matching and the image  $\Im(\mathfrak{DC})$  to the corresponding don't-care set as parameters. When finished, the algorithm returns the list of all the matching library elements, among which the minimum-cost one is chosen to cover  $\mathfrak{F}$ .

#### 3.4.2) Computation of Relevant Don't-Care Sets

Don't-care sets are classified into two major categories: external DC's, and internal DC's [23]. External DC's are assumed to be provided by the user along the network specification. They represent conditions that never occur on the primary inputs of the circuit and conditions that are never observed on the primary outputs. Internal DC's occur because of the Boolean network structure. They are further classified into controllability don't-cares and observability don't-cares. Controllability don't-cares represent impossible logic relations between internal variables. Observability don't-cares represent conditions under which an internal vertex does not influence any primary output.

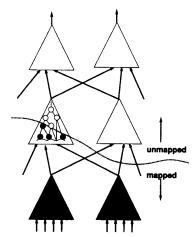

The existence of controllability and observability don't-care sets represent two different (but complementary) aspects of a network. Controllability don't-care sets are related to the logic structures in the transitive fan-in of a vertex, whereas observability don't-care sets are related to the logic structures in the transitive fan-out of a vertex in the Boolean network. The dynamic programming formulation of technology mapping implies the network to map is modified starting at the primary inputs, and is completed when all primary outputs are processed. The technology-mapping operation modifies the logic structure of the network, and potentially modifies the internal don't-care sets. Therefore, don't-care sets should be calculated dynamically, as the boundary of the mapped network moves from primary inputs to primary outputs (Fig. 9).

Controllability don't-care sets are conceptually easily computed: a vertex is being mapped only when all its predecessors are mapped. Then all the logic functions expressing a vertex are known, and it is straightforward to extract the controllability don't-care sets from them. For

```

dc_match(f,dc) {

vertex = get_vertex(f)

NPN_orientation = cast_to_same_NPN_class(vertex,f)

NPN_dc = change_NPN(dc,NPN_orientation)

for (all paths p, in vertex) {

if (included(p;,NPN_dc) {

update_cover_list(vertex_cover_list) }

}

return(cover_list) }

```

Fig. 8. Algorithm for compatibility graph traversal using don't-cares.

Fig. 9. Example of a partially mapped network.

a subset of variables Y that are inputs to a gate or a subnetwork, the controllability don't-care sets (CDC) represent the impossible patterns for the variables Y. The CDC sets can be derived from the satisfiability don't-care sets (SDC) by taking the iterated consensus of SDC on the variables different from Y, where the satisfiability don't-care set is defined as  $SDC = \Sigma i \oplus \mathcal{F}_i$  [23]. For example, for x = ab, the satisfiability don't-care is SDC,  $= x \oplus (ab) = \overline{x}ab + x(\overline{a} + \overline{b})$ . Controllability don'tcare sets can be computed in a straightforward manner from SDC for a particular subset of variables  $\{a, b, c, a\}$  $\cdots$  }. Given the satisfiability don't-care set  $SDC = \sum i$  $\oplus$   $\mathfrak{F}_i$ , each variable j of SDC not in the cutset  $\{a, b, c, a\}$  $\cdots$  } is eliminated by intersecting SDC  $|_{j}$  with SDC  $|_{\bar{j}}$ i.e.,  $CDC_{\{a,b,c,\cdots\}}(f) = \prod_{i \notin \{a,b,c,\cdots\}} \prod_{i=0}^{1} (\Sigma j \oplus \mathfrak{F}_j)$ . For example, let the subset of variables be  $\{x, a\}$  and  $SDC = \overline{x}ab + x(\overline{a} + \overline{b})$ . The  $CDC_{\{x,a\}} = SDC \mid_{b}$  $SDC \mid_{\overline{b}} = x\overline{a}$ . The controllability don't-care sets are computed dynamically as the mapping operation proceeds through the network (Fig. 10). Alternatively, the CDC can be computed using images and a range computation algorithm [26], [27], [28], [29].

Observability don't-care sets deal with the successors of vertices. They denote conditions under which a variable does not influence any primary output. For example, in the network x = at, t = b + c, t is unobservable when a = 0 (in that case, x = 0 regardless of the value of t).

Γ.

/\* Find starting point in the compatibility graph \*/

\* Find how f and the vertex are related \*/

\* Transform dc as f was transformed into the vertex function \*/

\* Find which paths to library elements are covered by dc \*/

By the very nature of dynamic programming techniques, when a vertex is being processed, its successors are not yet mapped. This implies that the exact observability of a vertex is known only after the mapping is completed. Note that unless the observability don't-cares are recomputed each time a vertex is modified, it is not possible to use the full ODC set for all the vertices [30]. Therefore, compatible subsets of the ODC need be used, as described in [31]. Although good algorithms have been proposed to compute compatible observability don't-care sets [32], [33], efficient implementations are far from trivial, and we decided not to include them at present. The results reported in Section V therefore represent only the use of controllability don't-care sets.

Note that when ( $\mathfrak{DC} \cup \mathfrak{F} = 1$ ), or  $\mathfrak{DC} \cup \overline{\mathfrak{F}} = 1$ , then the algorithm finds a match with the constant value 1 (0 in the second case). This is always preferred to any other match, since it has a cost of 0. As a result, for every cell mapped to a library element, there exists at least two controllable input patterns (i.e., it is possible to generate these patterns from the primary inputs), such that the output of the cell is 0 for one pattern and 1 for the other. This is a necessary condition to make a network testable. Assume that the library cells consist of testable gates (i.e., such that internal nodes are controllable and observable from the cell input/output pins). Then our method guarantees that the mapped circuit is 100% testable for stuckat faults with the recently proposed  $I_{DDQ}$  testing method [34], [35]. However, cell controllability is not sufficient for achieving 100% testability by using standard testing methods. Indeed, it is possible that the output of a cell is not observable at the primary outputs when the controllable input patterns are applied to that cell. But by using a post-processing step involving standard ATPG and redundancy removal techniques [36], the mapped network can be made 100% testable for single stuck-at faults. The post-processing step could in principle be eliminated by computing observability don't-care conditions. In practice this goal is hard to achieve, since the network is mapped from primary inputs to primary outputs and the observability of a vertex being mapped depends on portions of the network yet to be mapped.

## IV. PERFORMANCE-DRIVEN MAPPING

We now introduce an ensemble of operations to deal specifically with the optimization of delays through the network, in conjunction with technology mapping. We consider a delay model of the network with

<sup>&</sup>lt;sup>1</sup>Recall that a Boolean network is defined by a set of equations  $i = \mathfrak{F}_i$ . Therefore the condition  $(i \neq \mathfrak{F}_i) = i \oplus \mathfrak{F}_i$  can never occur.

```

ode(vertex,current.ode) {

/* Add all SDCs between vertex and current CDC cut set */

adc = recursive_xor(vertex_support(current_cdc))

ort_recursive(vertex_support(current_cdc) / Get list of cut set vertices now covered by vertex

ed_support = unused_sup

/* Update CDC with SDC previously calculated */

v.cdc = sdc U current.cdc

/* Update CDC cut set */

v_{cut_{a}et} = vertex \cup \{support(current_cdc) \setminus un

for (v ∈ support(new_odc), but ∉ new_cut_set)

/* Eliminate unused variables */

usus(new.cdc, v)

ann(new.odc)

ve_xor(eq,vertex,list)

eq = equation(vertex)

adc = xor(eq.vertex)

for (v ∈ support(eq), but not in list)

sdc = sdc ∪ recursive_xor(v,list)

i_support_recursive(vertex_list)

eg = equation(vertex)

for (v ∈ support(eq) and in list)

if (last_famout(v) = vertex)

unused.support = un

for (v \in support(eq) and not in list)

ed_support U unused_support_recursive(v,list)

```

Fig. 10. Algorithm for dynamic controllability don't-cares calculation.

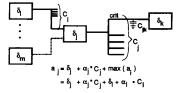

```

\begin{array}{lll} \delta & & \text{intrinsic (unloaded) gate delay;} \\ C & & \text{load capacitance at a gate output;} \\ \delta + \alpha \cdot C & \text{total gate delay;} \\ a_j = & & (\delta + \alpha \cdot C + \max a_i) \text{ arrival time at the output of gate } v_j, \text{ where } a_i \text{ is the arrival time at a gate input, with gate } v_i \in \text{fanin}(v_i). \end{array}

```

In our formulation of the problem, we are given the set of arrival times  $\{a_i\}$  of the primary inputs, together with the set of required times  $\{r_o\}$  of the primary outputs. For synchronous circuits with period T, we assume the input arrival times to be 0, and the required times at the outputs (i.e., register inputs) to be  $T - t_{\text{setup}}$ . We use the concept of slack [37], [38], [39], where the slack  $s_j$  at a certain vertex  $v_j$  corresponds to the difference between the required time at that vertex  $r_j$  and the arrival time  $a_j$ , i.e.,  $s_j = r_j - a_j$ . Therefore, time-critical nets are those with negative slacks.

We already mentioned in Section 2.3 that dynamic programming techniques can be used to optimize timing as well as area. But there is an important difference between the two optimizations: evaluating the area cost of a particular vertex mapping involves only vertices already mapped (predecessors of the vertex), whereas evaluating the timing cost involves also the successors of the vertex being mapped. Successors are needed because the capacitive load on the output of a gate influences its rise and fall times. Since the dynamic programming technique implies that the successors of a vertex being processed are not yet mapped, then the capacitive load on its output is not known. Therefore specific methods to deal with delay have to be introduced. Binning has been proposed by Rudell [40], where each vertex is (possibly) mapped for all the possible capacitive loads on its output. We propose a different heuristic solution, involving iterative mapping of the network. The first mapping of the network includes

Γ

only the optimization of area. Then, the portions of the network that do not meet the timing constraints are iteratively remapped. This method has the advantage that the entire environment of a vertex is known when it is remapped. In particular, the capacitive load driven by the vertex is known exactly.

It is important to remark that a solution under given timing constraints may not exist. Therefore our strategy is to perform a set of transformations leading to a mapped network that either satisfies the constraints or cannot be further improved by the transformations themselves.

In order to be efficient, iterative remapping has to be powerful enough to modify substantially the portions of the network that do not meet the timing constraints, i.e., the vertices with negative slack. To converge to a good solution in a finite number of steps, it must also be monotonic. We propose an ensemble of three techniques to achieve this goal:

- Repartitioning modifies the original partition of multi-fan-out vertices.

- Redecomposition changes the two-input decomposition, taking into account delay information.

- Buffering adds buffer to large fan-out gates on the critical paths.

The three operations are described next, and a description of their integration in the iterative process follows.

## 4.1. Repartitioning

Repartitioning takes place after a first mapping has been done, using the traditional partitioning technique outlined in Section 2.1. Repartitioning targets multiple-fan-out vertices that do not meet the timing constraints. The goal is to change partition-block boundaries, by merging subject graphs, to have other (and possibly more) choices when matching (and redecomposing) the vertices along the critical paths. Merging multiple-fan-out subject graphs

means the merged portions have to be duplicated for the other fan-outs to achieve the original functionality.

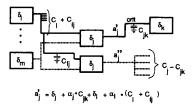

Consider, for example, the subcircuit in Fig. 11, where a gate j is a multiple-fan-out vertex on the critical path. The original arrival time  $a_j$  at its output is  $a_j = \max(a_i) + \delta_j + \alpha_j \cdot C_j$ , where  $a_i$  is the arrival time on the inputs,  $\delta_j$  is the intrinsic delay of gate j,  $\alpha_j$  is the fan-out-dependent delay factor, and  $C_j$  is the fan-out. Assuming  $a_l$  is the latest arriving input, we can reexpress  $a_j$  as  $a_j = \delta_l + \alpha_l \cdot C_l + \delta_j + \alpha_j \cdot C_j$ . Assuming one of the output fanouts is on the critical path, duplicating vertex j, with the new gate driving the critical path only, we get (Fig. 12)  $a_j' = \delta_l + \alpha_l \cdot (C_l + C_{lj}) + \delta_j + \alpha_j \cdot C_{jk}$ , and  $a_j'' = \delta_l + \alpha_l \cdot (C_l + C_{lj}) + \delta_j + \alpha_j \cdot (C_j - C_{jk})$ , where

- $a'_i$  new arrival time for the critical path,

- $a_i''$  new arrival time for the other fan-outs of j,

- $C_{li}$  input capacitance of j at input l,

- $C_{jk}$  input capacitance of gate k, which is the gate corresponding to the fan-out of j on the critical path.

Then, the difference in delay is  $\Delta a_i' = a_j' - a_j = \alpha_l \cdot C_{lj} + \alpha_j \cdot (C_{jk} - C_j)$ , and  $\Delta a_j'' = a_j'' - a_j = \alpha_l \cdot C_{lj} - \alpha_j \cdot C_{jk}$ . The arrival time of the fan-in vertices of  $v_j$  are also modified by the duplication process. The difference in delay is  $\Delta a_l' = a_l' - a_l = \alpha_l \cdot C_{lj}$ .

This example shows some important properties for vertices with multiple fan-outs:

- Duplicating gates per se reduces delay along the critical paths, when  $(\alpha_{i0} \cdot C_{ij} \alpha_j \cdot C_{jk} \le 0)$ . This is usually the case, and it can be verified on a case-by-case basis.

- The fan-ins of the duplicated vertex are slowed down by the addition of one gate load  $(\alpha_{ik} \cdot C_{ij})$ .

For a particular vertex that does not meet the timing constraints, it is therfore simple to verify how much can be gained by duplication, and whether or not the duplication affects other critical nets. In particular, if all the inputs of the vertex to duplicate have a single fan-out, then duplication is always a good solution. In addition, the duplicated vertex can now be merged forward into the next partition (it is now a single fan-out vertex). Mapping can be redone at this point on the modified partition, possibly improving delay even more.

## 4.2. Redecomposition

1

Redecomposition is used both alone or in combination with repartitioning. The goal is to bring late-arriving signals of a partition closer to its output. Redecomposition has (like decomposition) two important side effects:

- It influences the list of library elements that may cover a subject graph.

- It influences the critical path through the Boolean network.

The first point is related to the fact that different decom-

Fig. 11. Delays in a subcircuit.

Fig. 12. Delays in a subcircuit after gate duplication.

positions might give rise to different *possible* covers. For example, given  $f = a + b\overline{c} + \overline{b}c$ , the following decompositions imply very different covers:

$$f_1 = a + x_1$$

$f_2 = x_2 + z_2$

$x_1 = y_1 + z_1$   $x_2 = a + y_2$

$y_1 = b\bar{c}$   $y_2 = b\bar{c}$

$z_1 = \bar{b}c$   $z_2 = \bar{b}c$ .

In particular, the decomposition  $f_1$  allows the xor  $x_1 = b\bar{c} + \bar{b}c$  to be mapped, whereas in decomposition  $f_2$ , the xor gate cannot be found (because variable a appears as an input to the same gate as  $y_2 = b\bar{c}$ ). We address the first point by heuristically trying to keep repeated literals together during the decomposition. The second point is important because decomposition can be used to push latearriving signals closer or further from the output, possibly reducing or lengthening the critical path. This problem has been addressed by Singh [41] and Paulin [42].