# Optimal synthesis of control logic from behavioral specifications

performance of the resulting hardware.

Engineering award from the University of

Christensen Scholarship in 1985, the

David C. Ku and Giovanni De Micheli gol lortnoo suonordonys to sisedunys

Computer Systems Laboratory, Stanford University, Stanford, CA 94305, USA.

Received November 24, 1989

Abstract. This paper presents a method of synthesizing control for synchronous digital circuits starting from a behavioral description of the hardware. The input to the control synthesis task is an abstraction of hardware behavior based on sequencing graphs. The model is a concise way of specifying both control and data dependencies, and support hierarchy, unbounded delay operations such as data-dependent loops and external synchronizations, and multiple threads of concurrent execution flow. We show how the sequencing graph can be mapped directly to a modular interconnection of finite state machines. The approach, called adaptive control, is different from other control schemes in that it takes into account the dynamic variations in the execution delay of operations due to the changing inputs. It is optimal by guaranteeing the minimum number of cycles in the execution of a hardware behavior for all input sequences., Specifically, there are no performance penalties for the arbitrary nesting of procedure calls, conditionals, or loops. The adaptive control model and implementation are used within the framework of the HERCULES/HEBE High-Level Synthesis system.

Keywords. Automated control synthesis, high-level synthesis, control generation

#### 1. Introduction

High-level synthesis systems have been shown to be effective in supporting the design of Very Large Scale Integration (VLSI) digital circuits [1,5,8,14,16,17,18,21]. Numerous advantages can be achieved by designing a circuit starting from a self-documented high-level specification. In particular, the design is more porta-

Elsevier

INTEGRATION, the VLSI journal 10 (1991) 271-298 men as bived about 1982 mon girlensions.

0167-9260/91/\$03.50 © 1991 - Elsevier Science Publishers B.V.

ble, incremental changes in the specification are easier to incorporate, the specification is independent of the target technology, and the design life cycle is likely to increase. Powerful synthesis techniques can optimize the circuit at the behavioral, structural, and logic levels. This results in faster design turnaround time, and increases the quality and profitability of a given design.

We have developed a high-level synthesis sytem at Stanford University called HERCULES/HEBE [7], that transforms a behavioral hardware description in the HardwareC language [10] into an implementation in terms of synchronous logic circuits. This paper deals with a specific task of high-level synthesis: the synthesis of synchronous control logic. Control synthesis is important because it affects the control flow of operations, and hence directly impacts the overall performance of the resulting hardware.

Received November 24, 1989

Giovanni De Micheli is Associate Professor of Electrical Engineering and, by courtesy, of Computer Science at Stanford University. From 1984 to 1986 he worked at the IBM T.J. Watson Research center, Yorktown Heights, New York, where he was project leader of the Design Automation Workstation group. Previously he held position at the Department of Electronics of the Politecnico di Milano, Italy and at Harris Semiconductor, Melbourne, Florida. He was co-director of the Advanced Study Institute on Logic Synthesis and Silicon Compilation, held in L'Aquila, Italy, under the sponsorship of NATO in 1986 and in 1987.

He received a Dr. Eng. degree, Summa cum Laude, in Nuclear Engineering from the Politecnico di Milano, Italy, in 1979, a M.S. and a Ph.D. degree in Electrical Engineering and Computer Science from the Univer-

sity of California, Berkeley in 1980 and 1983, respectively.

Dr. De Micheli was granted a *Presidential Young Investigator* award in 1988. He received the 1987 Best Paper Award for the best paper published on the IEEE Transactions on CAD/ICAS and a Best Paper Award at the 20th Design Automation Conference, in June, 1983.

His research interests include several aspects of the computer-aided design of integrated circuits with particular emphasis on automated synthesis, optimization and verification of VLSI circuits. He is co-editor of the book: Design Systems for VLSI Circuits: Logic Synthesis and Silicon Compilation, Martinus Nijhoff Publishers, 1987.

Dr. De Micheli is a Senior Member of IEEE. He is member of the editorial board of the IEEE Design and Test magazine. He was technical and general chairman of the International Conference

on Computer Design - ICCD in 1988 and 1989, respectively.

David Ku was born in Taipei, Taiwan, in April 1964. He received in 1986 the B.S. degree in Electrical Engineering, Summa cum Laude, and the B.S. degree in Computer Science, Summa cum Laude, both from the University of Utah. He received the M.S. degree in Electrical Engineering from Stanford University in 1987. Since 1987, he is a doctoral candidate in Electrical Engineering at Stanford University. His research interests include high-level synthesis, control synthesis, design automation and CAD frameworks. David is currently a research assistant in the Electrical Engineering Department at Stanford University.

David is a CIS/Signetics FMA Fellow in the Center for Integrated Systems at Stanford University since 1989. He was granted the AT&T fellowship in 1986. He received the Most Outstanding Senior in Electrical Engineering award from the University of Utah in 1986, and the Most Outstanding Junior in Electrical Engineering in 1985. He also received the Minority Scholastic Award in 1986, the Clyde Christensen Scholarship in 1985, the Northwestern Energy Scholarship in 1984, and the University Scholarship from 1982–1986. David is a member of IEEE and ACM.

Numerous control styles have been used in high-level synthesis systems, ranging from read-only memory (ROM) based microprogrammed controllers [21] to distributed control [1]. Although these control approaches are part of powerful synthesis systems, the issue of minimizing the execution time of the hardware behavior is not adequately explored. We present here a control synthesis approach which addresses the following three issues:

- Support both fixed and unbounded delay operations Realistic hardware designs consist of operations with fixed delays, such as addition and multiplication, as well as operations with unbounded delays, such as synchronization primitives and loops with data-dependent completion. The unbounded delay operations have delays that are not known a priori.

- Supports multiple threads of execution flow The power of a synthesis system lies in its ability to explore tradeoffs between serial and parallel designs, related to the tradeoffs between area and performance. For such exploration to be possible, the control model should support multiple threads of concurrent execution flow.

Guarantees performance optimality For efficient hardware design, it is

- Guarantees performance optimality For efficient hardware design, it is important to generate a control that yields the minimum number of cycles in executing the hardware behavior for all input data sequences.

In the restrictive case where all operations have fixed and known delays, scheduling can be used to assign operations to specific time slots, with the control implemented accordingly [8]. In the general case, however, the synthesis of control is more complex. We present here an approach, called adaptive control, that directly maps an abstract hardware model in terms of sequencing graphs into a synchronous control unit consisting of a modular interconnection of interacting finite-state machines. As its name indicates, the adaptive control is able to take into account the variations in the execution times of the operations caused by the changing input data. It is optimal by guaranteeing execution of the hardware behavior in a minimum number of cycles for all input sequences. In particular, the hardware model derived from a procedural hardware description language incurs no performance penalties for the arbitrary nesting of procedure calls, conditionals, and loops.

The adaptive control synthesis has been implemented in the HERCULES/HEBE High-level Synthesis system and tested on many hardware design benchmarks. Since our model of hardware behavior is fairly general, this method has wide applicability to the synthesis of digital circuits. We therefore present it here as a control synthesis method based on an abstract hardware representation. This paper is organized as follows. We review first related research in the field and contrast it to our approach. We then formalize the problem in terms of a hierarchical graph representation and present two control implementations. The former is a simplified scheme that supports unbounded delays and multiple execution flows, but it does not yield optimal performance. We extend the approach in the latter control scheme to satisfy also the optimality requirement, as we prove formally. We conclude by commenting on the software implementation of this technique and on the experimental results.

#### Numerous control styles have been used in high-level drager batelar. 2.

In this section we briefly contrast our work with the related research in the area of automated control synthesis. A widely applied control style in many existing automated synthesis systems is the ROM-based microprogrammed controller model. Examples include the control allocator for the CMU-DA [15], the MCS system for AUDES [20], and the ATOMICS system for Cathedral-II [9,18]. The CMU-DA system is representative of a large number of data-path synthesis systems, including Chippe [2], Design Automation Assistant [11], Architect's Workbench [21], ADAM/MAHA [16], and HAL [17]. It assumes a canonical microprogrammed model, and performs optimizations based on the microcode format constraints. The MCS system is similar, but tailors the general microprogrammed controller model for a specific design. It performs compaction on the parallel operations and minimizes the width of the microwords using heuristic approaches. The ATOMICS system takes an RT-level description as input, and performs microprogram scheduling in order to minimize the global machine cycle count. A common assumption in these systems is that all operations have fixed delays. Namely, data-dependent loops and synchronization primitives such as message passing are not supported by the behavioral model.

Some systems relax the assumption on fixed delay. Among these, an effective approach is to directly map the control-data flow graph representing the hardware behavior into a corresponding state transition graph, which can be implemented by either a ROM or PLA. For example, the Yorktown Silicon compiler [1] implements control as a hierarchy of finite state machines, where a FSM is associated with each routine. Control state splitting allows tradeoffs to be made on the delay through the combinational part of the data-path. In the Karlsruhe synthesis system [5], a state transition graph is generated from the imperative portion of a description in the DSL language. The state transition graph is then optimized by merging states and physically realized. However, both systems assume a single thread of execution flow in the hardware behavior, which limits the flexibility of the synthesis system to explore architectural tradeoffs between serial and parallel design.

A novel formulation that addresses the issue of concurrency is the system proposed by Clarke [6]. A high-level specification of the control flow in a language called CSML is transformed into a state transition graph. To deal with the combinatorial state explosion encountered when dealing with concurrency of unbounded delay operations, interface modules are created for each pair of interacting state machines using a technique called compositional model checking. Unfortunately, the specification does not support data-path operation, and the state explosion problem impacts the efficiency of the resulting control implementation.

Finally, an alternate formulation of graph-based control is the system by Bruck [3]. Hardware behavior is specified using a CSP-like language called CAP/DSDL, which is mapped to a modified Petri-net model. Partitioning is performed to identify the strongly connected state machines, which can be mapped to different

implementation styles. Although it is modular and can support concurrency and external synchronization, the state explosion problem along with the duplication of subgraphs in the partitioning of Petri-nets are issues that need to be addressed.

Although the systems mentioned above are part of powerful synthesis systems, and effective in synthesizing a large class of designs, they address only part, not all, of our objectives – to support unbounded delay operations, concurrency, and to guarantee minimum execution time for all input sequences.

#### 3. Hardware model and problem formulation

We formulate the control synthesis problem on an abstract hardware model. To justify the model, we describe first the hardware description language (HDL) from which our model originates. It is important to remark that most of the language features are common to other HDLs. We abstract these features in the sequencing graph model as the basis for control synthesis.

graph model differs from the Value Trace [21] in that it is primarily control-ori-

#### lar HardwareC, Variations of this model were used in [1] and [5] 29 Mardhall. 1.8.

HardwareC is a procedural HDL with features to support interprocess communication [7]. The language models hardware as a set of concurrent and interacting processes. Each process represents a specific functionality that executes repeatedly. To support communication and synchronization among the concurrent processes, HardwareC has two mechanisms of process communication: parameter passing and message passing. The former model assumes the existence of a shared medium that interconnects the hardware blocks implementing the processes. Reading and writing to this medium is achieved by synchronous read/write operations. The latter model uses a point-wise synchronous send/receive message passing mechanism.

HardwareC supports the computation of arithmetic, Boolean, and relational expressions. It supports arbitrary nested procedure calls, conditional branches and iterative loops. Goto statements are not allowed. There are two variants of loops, depending on whether the iteration bound is fixed or data-dependent. Fixed iteration loops can be selectively unrolled during behavioral synthesis. Data-dependent loops include the while-do and repeat-until constructs. They

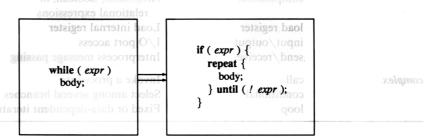

Fig. 1. Transformation of while loop to repeat-until loop.

differ in that the body of a repeat-until loop is always executed at least once. On the contrary, while-do loops may not even be entered depending on the initial value of the loop exit condition. Note that data-dependent loops may not be unrolled at compile time due to the data-dependent loop exit conditions. A while-do loop can be transformed into a conditional repeat-until loop by the transformation shown in Fig. 1. Therefore, without loss of generality we consider only repeat-until loops in latter discussions.

#### 3.2. Sequencing graph abstraction

Hardware behavior described in procedureal HDL can be modeled as a set of operations and a partial order among the operations. This is represented as a polar directed graph, called the sequencing graph. The vertices represent the operations to be performed, and the edges represent the dependencies that are either explicit in the hardware specification, or represent dependencies due to data-flow restrictions or hardware module sharing considerations. The graph model can capture the hardware primitives of most procedural HDLs, in particular HardwareC. Variations of this model were used in [1] and [5]. The sequencing graph model differs from the Value Trace [21] in that it is primarily control-oriented.

3. Hardware model and problem formulation

The vertices of the sequencing graph are classified into different types according to the operations they perform. For example, the types listed in Fig. 2 are sufficient to model HardwareC descriptions [10]. The vertices are further categorized as simple or complex. The simple vertices are operations that do not involve other operations. For example, computations such as addition or Boolean expressions and message passing primitives are simple vertices. On the other hand, complex vertices allow groups of operations to be performed, and include procedure calls, conditionals, and loops. They are analogous to structured control flow constructs in most programming languages. No-op vertices are used as the source and sink vertices of the sequencing graph.

The semantic interpretation of the sequencing graph model is as follows. A vertex is *executed* by performing the task described by the vertex. For example, to execute a *computation* vertex, the task to be performed is the evaluation of the

| Category | Туре                                    | Operation represented                                                               |

|----------|-----------------------------------------|-------------------------------------------------------------------------------------|

| simple   | no-op<br>computation                    | No operation Arithmetic, Boolean, or relational expressions                         |

|          | load register input/output send/receive | Load internal register I/O port access Interprocess message passing                 |

| complex  | call conditional loop                   | Invoke a procedure Select among several branches Fixed or data-dependent iterations |

Fig. 2. Types of vertices to capture HardwareC descriptions.

corresponding expression; to execute a conditional vertex, the operations within the selected branch are executed. In the case of a call vertex, the control flow is temporarily transferred to the called graph. When the called graph completes execution, the control flow returns to the calling vertex. The execution of a sequencing graph is the execution of its vertices according to the dependencies of the graph. A vertex begins execution when all its predecessors have completed execution. Since a vertex may have multiple predecessors and successors, the model supports multiple threads of concurrent execution flow.

The complex vertices – call, conditional, and loop – induce a hierarchical relationship among the graphs. A call vertex invokes the sequencing graph corresponding to the called procedure. A conditional vertex selects among a number of branches, each of which is modeled by a sequencing graph. A loop vertex iterates its body until the exit condition is satisfied; the body of the loop is also a sequencing graph. The sequencing graph is therefore acyclic because only structured control-flow constructs are assumed (no goto), and loops are broken through the use of hierarchy.

#### (3) The execution delay of a loop vertex is equal to the nucleon delay.

We assume in this paper a synchronous implementation of the operations and their control. Therefore we associate with each operation an execution delay in terms of the number of cycles required to complete its execution. For fixed delay operations, the execution delay is computed by the synthesis techniques used for the operations themselves, e.g. apply logic synthesis for delay estimates. We do not address in this paper the specification of the execution delays: we assume only that it is an integer value greater than or equal to zero. The control is synthesized based on the values of these execution delays. We can now formally define the sequencing graph model:

multipled by the execution delay of the loop body.

**Definition 1.** A sequencing graph G(V, A, W) is a hierarchical polar weighted directed acyclic graph, where the vertices  $v_i \in V$  correspond to the operations to be performed, and the directed edges  $a \in A$  represent the sequencing dependencies between the operations. Each vertex  $v_i \in V$  is labeled by an integer weight  $w_i \in W$ ,  $w_i \ge 0$ , representing the execution delay of  $v_i$ .

represents, the property of stateless/state may change dynamically as different

A problem arises when we try to define the delay for a conditional or loop that depends on some external signal or event not known statically. To address this point, the vertices of the graph are categorized into bounded and unbounded vertices. A vertex is bounded if the time required to execute its operation is fixed for all input data sequences; the delay depends solely on the nature of the operation. Examples include addition and register loading. On the other hand, a vertex is unbounded if the time required to execute its operation is data-dependent. Loops whose exit condition depends on some signal value, or message passing primitives that synchronize between two concurrent processes are examples of unbounded vertices. The categorization is hierarchical. A sequencing

graph whose vertices are bounded is called a bounded sequencing graph. A call to a bounded sequencing graph is bounded, a conditional whose branches are all bounded is bounded, and a fixed iteration loop whose body is bounded is bounded.

The presence of unbounded vertices makes it necessary to relate the execution delay of a vertex to a particular input sequence because the time to achieve synchronization, and the number of times a loop iterates are known for a given input sequence. The execution delay of a hierarchical graph is computed bottom up, according to the following definition:

Definition 2. For a particular input sequence, the execution delay of a sequencing graph is equal to the length of the longest weighted path from source to sink, where:

- (1) The execution delay of a call vertex is exactly equal to the execution delay of neithe called graph. (0100 on) behaves an abundance woll-loring behavior

- (2) The execution delay of a conditional vertex is equal to the execution delay of the selected branch.

- (3) The execution delay of a loop vertex is equal to the number of iterations multipled by the execution delay of the loop body.

We further classify a vertex according to the value of its execution delay. A vertex whose operation requires one or more cycles to execute (execution delay > 0) is called a *state* vertex. Otherwise, it is called a *stateless* vertex (execution delay = 0). A sequencing graph where all the vertices are stateless is a stateless sequencing graph.

The property of stateless/state is independent of the classification into bounded/unbounded vertices. Whereas the determination of whether a vertex is bounded or not can be made statically by considering the type of operation it represents, the property of stateless/state may change dynamically as different input sequences are applied to the hardware model. The stateless/state property for bounded vertices is fixed; e.g. a no-op vertex is always stateless and a load-register (takes one cycle) is always a state vertex. For unbounded vertices, however, the property depends on the value of the execution delay for a particular input sequence. Consider for example a conditional vertex with two

| Category    | Туре                  | Bounded/Unbounded            | Stateless/State           |  |  |

|-------------|-----------------------|------------------------------|---------------------------|--|--|

| simple      | no-op                 | Bounded Bounded              | Stateless                 |  |  |

| idress this | computation           | nal signal or even behaved   | Stateless or State        |  |  |

|             | load register         | Bounded to are calbahuod     | point the verticesta t    |  |  |

|             | input/output          | nded if the time rbsbnuod to | vertices. A vertex attack |  |  |

|             | send-receive          | ences; the delbebnuodnU      | for all input datastaqu   |  |  |

| complex     | loading. On tils oth  | Bounded or Unbounded         | Stateless or State        |  |  |

| па-ферев-   | b conditional o an of | Bounded or Unbounded         | Stateless or State XOLTOV |  |  |

| message     | ome signal vool, o    | Bounded or Unbounded         | Stateless or State   Jash |  |  |

| are exam-   | oncurrent processes   | ynchronize between two c     | passing primitives that s |  |  |

gnionoupos A Fig. 3. Categorization of vertices according to their properties. and distributed to roll and an armony of the solution of vertices according to their properties.

branches, one state and one stateless. If for a particular input sequence the selected branch is stateless, then the conditional vertex is stateless for that input sequence. Likewise, if a new input sequence is applied to the conditional causing the other branch to be selected, then the conditional vertex becomes a state vertex. The same analysis applies to call and loop vertices. The properties are summarized in Fig. 3.

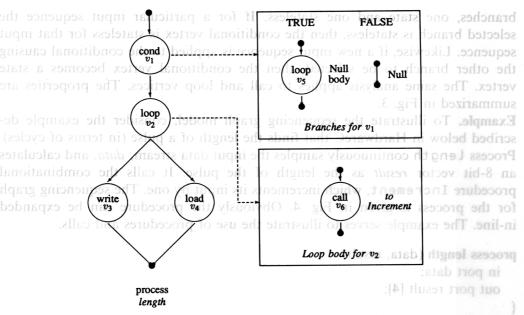

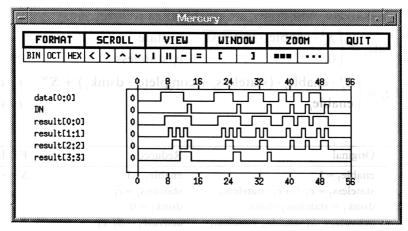

Example. To illustrate the sequencing graph model, consider the example described below in HardwareC that finds the length of a pulse (in terms of cycles). Process length continuously samples the input data stream, data, and calculates an 8-bit vector result as the length of the pulse. It calls the combinational procedure Increment, which increments its input by one. The sequencing graph for the process is given in Fig. 4. Obviously the procedure can be expanded in-line. The example serves to illustrate the use of procedures and calls.

```

process length (data, result) and another

in port data;

out port result [4];

{

Fig. 4. Sequencing graph example for process let; [4] ratnuos nealood

if (data = 0){

/ * v<sub>1</sub> * /

guarantee a minimum number of cvdes el to cuting the hardware bel sagaror all

\} until (data = 1);

To define a criterion for optimality, we need to model the control implementa-

tion of a sequencing graph. As in $12V tale of the operations, we stages a

Increment(counter, counter); / * v<sub>6</sub> * /

synchronous finite state machine (FSM), where transitions oc;(0 = atab) litnu {on

write result = counter; * v<sub>3</sub> * / off | vov vev is langer sools a lo

counter = 0; girly * 1 FSM corresponding; 0 = ranuo

implementation is assumed to be initially in the reset state, and returns to the

reset state when all the operations of the graph have bee (tuqtuo, state)

input sequence, the control delay of the control implementa; [4]atab naing

graph is the number of cycles to go from the reset state ;[4]tuqtuo and tuo

The sequencing graph constrains the assignment of the operations to the FSM

control states. Namely, no two states vertices connected; 1th atab at jurquo he

sequencing graph can be assigned to the same control state. Therefore the

```

The execution delay for both the I/O write  $(v_3)$  and register loading  $(v_4)$  is 1 cycle, therefore they are state vertices. Since Increment consists of combinational logic, it is a stateless procedure.

# **Definition 3.** A control implementation for a sequencing graph G is optimal if its control delay is exactly equal to the execution delay of G for **sizehtnyz lortno2.4**.

Given a hardware description in terms of the sequencing graph model, the task of control synthesis is to generate a control that activates the operations according to the sequencing dependencies of the graph. Our objective is to in addition

Fig. 4. Sequencing graph example for process length.

guarantee a minimum number of cycles in executing the hardware behavior for all input sequences.

To define a criterion for optimality, we need to model the control implementation of a sequencing graph. As in the case of the operations, we assume a synchronous implementation of control that can be modeled on the whole as a synchronous finite state machine (FSM), where transitions occur by the assertion of a clock signal at very cycle <sup>1</sup>. The FSM is characterized by a set of states called control states. For a sequencing graph, the FSM corresponding to its control implementation is assumed to be initially in the reset state, and returns to the reset state when all the operations of the graph have been executed. For a given input sequence, the control delay of the control implementation for a sequencing graph is the number of cycles to go from the reset state back to itself

The sequencing graph constrains the assignment of the operations to the FSM control states. Namely, no two states vertices connected by a path in the sequencing graph can be assigned to the same control state. Therefore the execution delay of a sequencing graph is always a lower bound for the control delay of the corresponding control implementation. We define the criterion for optimality as follows:

**Definition 3.** A control implementation for a sequencing graph G is *optimal* if its control delay is exactly equal to the execution delay of G for all input sequences.

The model of synchronous control as a FSM serves as an abstraction to reason about its properties and it does not imply its physical realization in hardware, i.e. the control circuit may be physically implemented either as a single FSM or as a network of FSMs.

Intuitively, the time to execute an optimal control implementation of hardware behavior depends solely on the execution of the operations and not on the transfer of control. For example, if a cycle is needed to transfer control to a called procedure (as in the microcode-based implementation of [21]), then the control implementation is not optimal by the above definition. On the other hand, an optimal control implementation incurs no delay penalty in the use of control flow constructs such as procedure calls, conditionals, and loops in the HDL.

#### 4.1. Adaptive control

We present an approach to control implementation called *adaptive control* that supports multiple threads of concurrent execution flow and the presence of unbounded delay operations. Before describing the details of adaptive control, we contrast it briefly with other control schemes that address the simplified paradigms of either fixed delay operations, or a single thread of execution flow.

In the case where all operations have fixed delays, scheduling techniques can be used to assign all operations to the states of a microcode sequence, as in [8,16,15]. Scheduling can be applied hierarchically to support fixed-iteration looping and conditional branching. In the case where there is a single thread of execution flow [1], a control automaton can be derived by assigning a state to each vertex of the sequence graph. Transitions among the states depend on the completion of the corresponding operation. The presence of multiple threads of execution flow complicates the situation. In particular, the completion of an operation is not a sufficient condition to trigger the execution of its successor because the successor may have multiple predecessors. The activation of an operator depends on the completion of execution of all its predecessors, and hence in the general case it is necessary to store the information related to the completion of an operation.

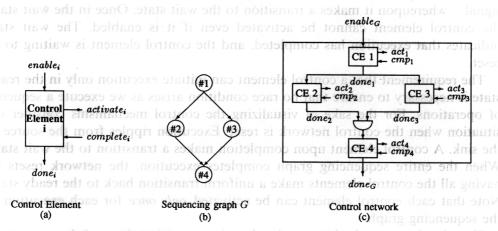

Fig. 5. Direct mapping of the sequencing graph model to the control for (a) a single vertex; (b) sequencing graph; and (c) the corresponding control network.

operations, the adaptive control is implemented as a modular interconnection of control elements. There is one control element per vertex of the sequencing graph, with the interconnection of the control elements having the same topology as the sequencing graph. Since there is a one-to-one correspondence between vertices and control elements, a vertex and its control element are referred to interchangeably. The management of the sequencing graph.

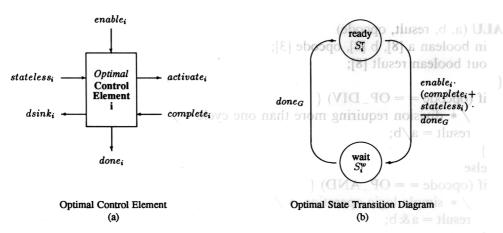

To communicate among the control elements, the control element of a vertex  $v_i$  has two handshaking signals: enable<sub>i</sub> and done<sub>i</sub>. The enable / done handshaking signals indicate when a control element is enabled and when it is finished. The control element of a vertex  $v_i$  initiates its operation in the data-path using the activate<sub>i</sub> signal, and acknowledge completion from the operation using the complete<sub>i</sub> signal. Figure 5 illustrates the direct mapping from the graph to the control and acknowledge completion appends from the graph to the

#### digms of either fixed delay operations, or a single thread of executionsday, or a single thread of executions.

The implementation of a control element is dependent on whether the corresponding vertex is *stateless* or *state*. If a vertex  $v_i$  is stateless for all input sequences (e.g., no-op or a combinatorial logic operation), then its control element asserts the done signal as soon as it is enabled. No state information is needed in this case, and the control element degenerates to the combinational logic, done, = enable,

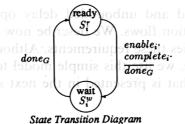

On the other hand, if a vertex requires one or more cycles of execution delay for some input sequences, then the control element is implemented as a synchronous FSM. The FSM has two states - ready  $(S_i^r)$  and wait  $(S_i^w)$ , which can be implemented using a single bit register. The initial state for a control element is the ready state. The reset state for an entire control network is defined to be when all the control elements are in their ready states. In the ready state, a control element begins executing its operation whenever it is enabled. It remains in  $S_i^r$  until the completion of execution - signified by the assertion of the complete, signal - whereupon it makes a transition to the wait state. Once in the wait state, the control element cannot be activated even if it is enabled. The wait state indicates that execution has completed, and the control element is waiting to be reset.

The requirement that a control element can initiate execution only in the ready state is necessary to ensure that no race condition arises as we execute a sequence of operations. For the sake of visualizing the control mechanisms consider the situation when the control network is reset. Execution ripples from the source to the sink. A control element upon completion makes a transition to the wait state. When the entire sequencing graph completes execution, the network resets by having all the control elements make a uniform transition back to the ready state. Note that each control element can be activated *only once* for each execution of the sequencing graph.

The adaptive control adapts to the changing execution times of the operations, and has several advantages, including modularity, distribution of control, uniform

handling of both bounded and unbounded delay operations, and support of multiple concurrent execution flows. We describe now a simple adaptive control implementation that satisfies these requirements. Although it may not be optimal in terms of execution time, we use this simple model to justify a more elaborate adaptive control scheme that is presented in the next section which satisfies the optimality requirement.

## 4.2. A simple adaptive control implementation and morning at the state of the state

In the sequel we use the following terminology. Let  $pred(v_i)$  and  $succ(v_i)$  denote the set of predecessors and successors of a vertex  $v_i$  in the sequencing graph, respectively. We associate to vertex  $v_i$  the handshake signals for the corresponding control element: enable, done, activate, and complete. The handshake signals are defined below, where complete is generated by the corresponding operation in the data-path.

(1) load-register vertices, they are connected to

$$\frac{1}{3}$$

load-register vertices, they are connected to  $\frac{1}{3}$  load-register vertices, they are connected to  $\frac{1}{3}$  load-register vertices, the activate complete signals are mutu-

message passing send/receive vertices, the activate complete signals are muturely coupled. Specifically, the activate of states

$$i_i v_i$$

ald  $i_i$  all  $i_i v_i$  and the sending receive, and the sending  $i_i v_i$  the received to the

$$\operatorname{done}_{i} = \begin{cases} S_{i}^{\mathrm{r}} \cdot \operatorname{enable}_{i} \cdot \operatorname{complete}_{i} + S_{i}^{\mathrm{w}} \quad v_{i} \text{ state} \\ \operatorname{enable}_{i} \end{cases} \quad v_{i} \text{ stateless of rose bons. 8 giff at$$

A vertex is enabled when all predecessors have completed execution, whereupon the corresponding operation is activated until its completion. The enable of a sequencing graph G is the enable of its source vertex, denoted by enable<sub>G</sub><sup>2</sup>, likewise, the done of a sequencing graph G is the done of its sink vertex, denoted by done<sub>G</sub>.

If a vertex  $v_i$  is stateless for all input sequences, then it asserts its done signal as soon as it is enabled. Otherwise, the control element is implemented as a two-state FSM, as shown in Fig. 6. The FSM remains in the ready state  $S_i^r$  until it has completed execution, after which it enters the wait state. The transition back from  $S_i^w$  occurs when the entire graph G has completed execution, signaled by the assertion of done<sub>G</sub>. The transition conditions for the FSM are given below:

From

$$S_i^r$$

to  $S_i^w$ : enable<sub>i</sub> complete<sub>i</sub>  $\overline{\text{done}_G}$

From  $S_i^w$  to  $S_i^r$ : done<sub>G</sub>

a sequencing graph. The double-circled

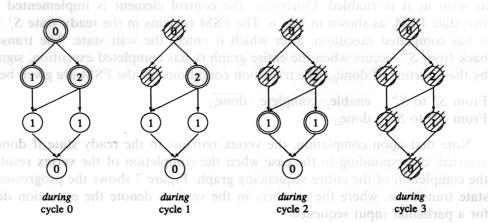

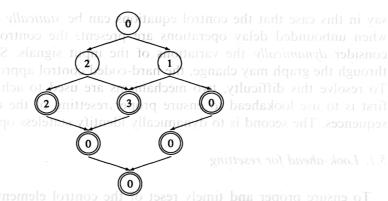

Note that upon completion, the vertex remains in the ready state if  $done_G$  is asserted, corresponding to the case when the completion of the vertex results in the completion of the entire sequencing graph. Figure 7 shows the progression of state transitions, where the numbers in the vertices denote the execution delays for a particular input sequence.

The enable signal of the root graph (process) of a sequencing graph hierarchy is a constant logic "1", to allow the corresponding process to restart execution upon completion.

Fig. 6. State transition diagram for the simple control element.

The control element model is applicable to any type of vertices. The personalization is determined by how the control elements interconnect their activate and complete signals. For simple vertices, these signals are connected directly to the data-path components implementing the operations. For instance, the activate/complete signals for I/O read and write vertices are connected to the I/O ports. For load-register vertices, they are connected to the registers being loaded. For message passing send/receive vertices, the activate/complete signals are mutually coupled. Specifically, the activate of the send is connected to the complete of the corresponding receive, and the activate of the receive is connected to the complete of the send.

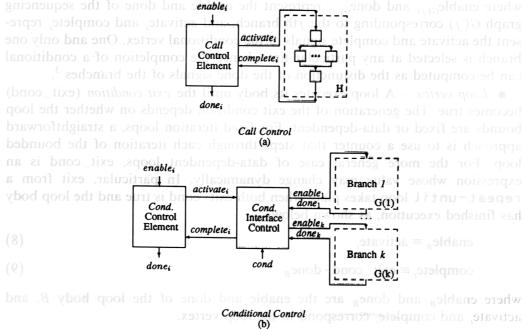

Additional control circuitry is needed for *complex* vertices. They are illustrated in Fig. 8, and described below:

● Call vertex – A network of control elements implementing a sequencing graph can be treated as a single abstract control element, where the enable/done of this abstract control element is connected to the enable/done of the given graph. This formulation supports hierarchy, and allows for a consistent view of the control for both a single operation and a group of operations. The activate (or

Fig. 7. The progression of state transitions in the execution of a sequencing graph. The double-circled vertices denote currently executing vertices (in  $S^r$ ), shaded vertices denote vertices that have finished execution (in  $S^w$ ), and unshaded single-circled vertices denote unexecuted vertices.

(c)

Fig. 8. Generating control for complex vertices: (a) call; (b) conditional; and (c) loop.

Loop Control

he network in preparation for the

complete) signal of the call is connected to the enable (or done) of called sequencing graph, as shown below.

(4) le

$$n+1$$

. However, this is not possible in the simp attached  $= \frac{1}{n}$

(5) ause the resetting of the control network occurs one

$$_{H}$$

and  $\equiv$   $_{i}$  at a superior of

where  $enable_H$  and  $done_H$  are the enable and done of the called graph H, respectively.

• Conditional vertex — Since each branch of a conditional is a separate sequencing graph, a conditional is analogous to a multi-way procedure call that depends on the value of the conditional expression. For a conditional with k branches, the handshake signals are defined as follows:

$$enable_{G(j)} \equiv activate_i \cdot (cond = jth branchvalue)$$

(6)

of the conditional vertex. If this assumption is not valid, then either

$$\prod_{j=1}^{\infty} \text{value of the conditional}$$

$\prod_{j=1}^{\infty} \text{long}_{G(j)}$  must be store  $\prod_{j=1}^{\infty} \text{long}_{G(j)}$  the conditional of the conditional  $\prod_{j=1}^{\infty} \text{variable}_{G(j)}$

where enable<sub>G(j)</sub> and done<sub>G(j)</sub> represent the enable and done of the sequencing graph G(j) corresponding to the jth branch, and activate<sub>i</sub> and complete<sub>i</sub> represent the activate and complete signals of the conditional vertex. One and only one branch is selected at any particular time, hence the completion of a conditional can be computed as the disjunction of the done signals of the branches <sup>3</sup>.

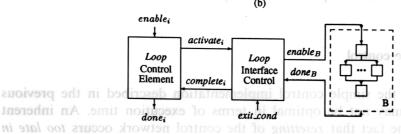

• Loop vertex – A loop executes its body until the exit condition (exit\_cond) becomes true. The generation of the exit condition depends on whether the loop bounds are fixed or data-dependent. For fixed iteration loops, a straightforward approach is to use a counter that steps through each iteration of the bounded loop. For the more general case of data-dependent loops, exit\_cond is an expression whose value may change dynamically. In particular, exit from a repeat-until loop takes place when both exit\_cond is true and the loop body has finished execution, as shown below.

$$enable_B = activate_i$$

(8)

$$complete_i = exit\_cond \cdot done_B$$

(9)

where enable<sub>B</sub> and done<sub>B</sub> are the enable and done of the loop body B, and activate<sub>i</sub> and complete<sub>i</sub> correspond to the loop vertex.

#### 5. Optimal adaptive control

A limitation of the simple control implementation described in the previous section is that it may not be optimal in terms of execution time. An inherent difficulty lies in the fact that *resetting* of the control network occurs too late in time. There is a conflict between trying to reset the network in preparation for the next activation, and actually knowing when to reset.

To illustrate the difficulty, consider a sequencing graph G representing either a process or a loop body that we wish to execute repeatedly. At a particular cycle n, G is in its final cycle of execution, and  $\operatorname{done}_G$  is asserted at the start of the next cycle n+1. Ideally, the control of G should be ready to restart execution during cycle n+1. However, this is not possible in the simple control implementation because the resetting of the control network occurs one cycle after the assertion of  $\operatorname{done}_G$ . Consider the example in Figure 7. The control network detects the completion of the entire graph during cycle 3, and resets one cycle later in cycle 4. Therefore, the periodicity of execution is 4 cycles instead of the critical path delay of 3 cycles. This is clearly suboptimal.

When all operations have fixed delays, the restarting periodicity can be hard-coded into the control because the total delay through the graph is fixed. We

We assume here that the branch condition remains unchanged for the entire duration of execution of the conditional vertex. If this assumption is not valid, then either the value of the conditional expression or the activate signals  $\operatorname{enable}_{G(j)}$  must be stored to ensure that the branch condition remains unchanged during execution of the conditional.

say in this case that the control equations can be *statically* derived. Conversely, when unbounded delay operations are present, the control equations have to consider *dynamically* the variations of the input signals. Since the total delay through the graph may change, the hard-coded control approach cannot be used. To resolve this difficulty, two mechanisms are used to achieve optimality. The first is to use lookahead to ensure proper resetting of the control for all input sequences. The second is to dynamically identify stateless operations.

#### 5.1. Look-ahead for resetting

To ensure proper and timely reset of the control elements, it is necessary to know when a given graph is in the *last cycle* of its execution. If the detection of completion occurs during the last cycle, then the control can reset during the last cycle and restart execution in the following cycle. This guarantees the control of a sequencing graph can repeatedly execute without losing a cycle to reset, which is crucial to ensure no wasted time for restarting loops and processes.

This look-ahead requirement can be achieved by defining the complete signal of a vertex to be asserted during the last cycle of execution of the corresponding operation. For example, if an operation takes only one cycle, then the corresponding complete signal is asserted as soon as it is enabled. In general, if an operation takes n cycles to execute, the corresponding complete signal will be asserted during the nth cycle  $^4$ .

The redefinition of the complete signals needs to be applied consistently throughout the sequencing graph model. For simple vertices, the complete signals are generated by the synthesis system and hence pose no difficulty. However, for complex vertices that invoke other sequencing graphs, we need to detect the completion of an entire graph during the final cycle of execution, denoted by the assertion of done<sub>G</sub>. Since a sequencing graph may have multiple threads of concurrent execution flow, we identify the set of vertices, called *direct-sink* vertices, whose combined completion results in the completion of the entire graph.

**Definition 4.** A vertex v of a sequencing graph G(V, A, W) is a direct-sink vertex if the longest weighted path from v to the sink vertex, excluding the weight of v, is zero. Otherwise, the vertex is an indirect-sink vertex.

As an illustration, consider the sequencing graph of Fig. 9, where the numbers in the vertices represent the execution delay for a particular input sequence. The double-circled vertices are the direct-sink vertices. The completion of execution of

<sup>&</sup>lt;sup>4</sup> It is straightforward to implement a control scheme that uses this look-ahead technique. The only complication is the necessity to determine whether the loop exit condition is satisfied *during* the final cycle of a loop's execution. Since the exit condition may depend on values of variables that are stored in registers and updated at the end of each iteration, the exit condition is computed with the values of variables before they are updated into the registers.

Fig. 9. Illustrating direct sink vertices. The double-circled vertices are direct sink for a given input sequence.

all direct-sink vertices results in the completion of the execution of the entire graph. Note that if the source vertex is direct-sink for a particular input sequence, then by definition the sequencing graph is stateless for that input sequence.

A complication arises since the execution delay of an unbounded vertex may change for different input sequences; in particular it may become zero, making the vertex stateless. Therefore, it is in general not possible to statically identify the set of direct-sink vertices. To address this issue, a direct-sink signal (dsink) is defined for each control element of the network. The dsink signal is asserted when the corresponding vertex is currently direct-sink. Specifically, the dsink, signal for a vertex  $v_i$  is computed as follows:

$$dsink_{i} = \prod_{s \in succ(v)} dsink_{s} \cdot stateless_{s}$$

(10)

where stateless, is asserted if the corresponding vertex s is stateless. Note that dsink of the sink vertex is a constant logic "1".

With this formulation, the control can track the variations in the execution delay of a graph because the dsink signals are evaluated dynamically during hardware execution. Note that if the direct-sink vertices are all bounded vertices, then the dsink signals can be evaluated statically, not adding to the complexity of the resulting implementation.

### 5.2. Dynamically identify stateless computation

Computations that do not take any time to execute, such as stateless branches of conditionals, should immediately activate their successor operations without taking a cycle to transfer control. It is therefore important to know when a given operation is stateless; i.e., execution delay is zero for a particular input sequence. Furthermore, since our model supports unbounded delay operations, it is necessary to dynamically determine whether a particular operation is stateless.

We define a stateless signal for each control element which is asserted whenever the corresponding vertex is stateless (has zero execution delay) for a

particular input sequence. The stateless signals for simple vertices are known statically, e.g., the stateless signal for load register, synchronous I/O, or synchronous send/receive message passing vertex is always "0". The stateless signals for complex vertices are evaluated dynamically, as described below:

e Call – The stateless signal for a call vertex is asserted if the called graph is When the hardware modeled by ALU is executing, the null branch:

(11) inational procedure. Otherwise, it is a sequential

$$^{H}$$

Drocedure if the

where  $dsink_H$  is the direct-sink signal of the source vertex of the called graph H, which is asserted if H is stateless.

Conditional - The stateless signal is asserted whenever the selected branch is stateless:

stateless<sub>i</sub>

$$\equiv \sum_{j=1}^{k} \operatorname{dsink}_{G(j)} \cdot (\operatorname{cond} = j \operatorname{th} \operatorname{branchvalue})^{(minor)}$$

(12)

The optimal control implementation extends the approach described in the

where  $dsink_{G(j)}$  is the direct-sink signal of the source vertex of the sequencing graph G(j) corresponding to the jth branch, and cond is the conditional expression.

• Loop - The stateless, signal for a repeat-until loop is always "0" because the loop body executes at least once.

The use of stateless signals extends the flexibility and power of the control to adapt to the input variations. Most systems deal with loops and procedure calls in a static manner. For example, a loop in many systems takes at least one control cycle to execute, even if it is only to discover that the loop should not be entered (assuming data-dependent loops are even allowed). Likewise, a procedure is often tagged as being either combinational or sequential at compile time, corresponding to whether it requires zero or more cycles to execute, respectively. However, the implementation of a procedure may be at times combinational and at times sequential, depending on the inputs that are applied. Consider the simple description of an ALU below.

```

ALU (a, b, result, opcode)

in boolean a [8], b [8], opcode [3];

out boolean result [8];

{

if (opcode = OP_DIV) {

/* division requiring more than one cycle * /

result = a/b;

}

else

if (opcode = OP_AND) {

/* simple logic operation * /

result = a&b;

}

}

```

```

particular input sequence. The stateless signals for simple vertices are } selson statically, e.g., the stateless signal for lox * giridton ob * sbood blavni * noon send/receive message passing vertex is always "0". The stateless signals for complex vertices are evaluated dynamically, as described below:

• Call - The stateless signal for a call vertex is asserted if the called graph is

```

When the hardware modeled by ALU is executing, the null branch of the conditional is selected if the opcode is OP\_AND, whereupon ALU becomes a combinational procedure. Otherwise, it is a sequential procedure if the opcode selects an operation requiring one or more cycles to execute, such as OP\_DIV. By using the stateless signal, we can now take into consideration the dynamic variations in the time required to call a procedure, and not waste a cycle in calling stateless (combinational) procedures.

#### 5.3. Optimal control implementation

The optimal control implementation extends the approach described in the previous section by incorporating the mechanisms of look-ahead resetting and dynamically identifying stateless computations. The control element for a state vertex  $v_i$ , shown in Fig. 10, has two states as in the previous model –  $ready(S_i^r)$  and  $wait(S_i^w)$ . The transition conditions are now described as follows:

```

because the loop body executes at least once.

The use of stateless si_0=0 (is allowed in the input variations. Most systems deal with loop_0=0 and loop_0=0 in the input variations. Most systems deal with loop_0=0 and loop_0=0 in the input variations a static manner. For example, a loop in many systems takes at least one control.

```

The operation begins executing in the ready state. Upon completion or detection of statelessness, the FSM makes a transition to the wait state. When the entire graph is done (signified by  $done_G$ ), the control element makes an uniform transition back to the ready state.

The enable signal enable, remains the same as in the simple control implementation, equal to the conjunction of the predecessor's done signal (eqn. (1)).

Fig. 10. Optimal control element and its state transition diagram.

|                       | 20 100000           | e activate <sub>i</sub> and done <sub>i</sub> are mod<br>$S_i^r$ enable <sub>i</sub> stateless.                                                                                         |                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       | activ               | $ate_i = \begin{cases} S_i^r \cdot enable_i \cdot \overline{stateless}_i \\ 0 \end{cases}$                                                                                              | v. stateless                                       | > X3H   130   NI8   (13)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                       |                     | (Stateless                                                                                                                                                                              | laammlata dain                                     | dr.) L CW state                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                       | done                | $I_i \equiv \begin{cases} S_i^{r} \cdot enable_i \cdot (stateless_i + enable_i) \\ enable_i \end{cases}$                                                                                | complete <sub>i</sub> · dsm                        | $(v_i) + S_i^{w}$ $v_i$ state                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                       |                     | (enable <sub>i</sub>                                                                                                                                                                    |                                                    | $v_i$ stateless                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                       |                     |                                                                                                                                                                                         |                                                    | (14) result[0:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| #                     | Type                | Original                                                                                                                                                                                | Reduced 0                                          | [E:Elfluser FSM State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| $v_1$                 | cond                |                                                                                                                                                                                         | $enable_1 = 1$                                     | $S_1^r \Leftrightarrow S_1^w$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                       | on                  | $stateless_1 = c_1 \cdot 0 + \overline{c_1} \cdot stateless_5$                                                                                                                          | $stateless_1 = \overline{c_1}$                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |