# NEW ALCORITIMS FOR TIMING ANALYSIS OF LARGE CIRCUITS

G. De Micheli, A. Sangiovanni-Vincentelli, A. R. Newton

Department of Electrical Engineering and Computer Sciences

University of California, Berkeley, 94720.

ABSTRACT: Tuning simulation is a simplified form of circuit simulation in which the circuit equations are decoupled at each node to take advantage of the relative inactivity of large digital networks. Conventional integration schemes applied to tightly-coupled, bidirectional circuit elements either exhibit significant regions of instability or inaccuracy, or do not provide the necessary node decoupling. This paper examines a variety of implicit-explicit by brid algorithms, classified as variable-in-time or variable-in-space, which are suitable for timing simulation. The floating capacitor, common in MOS circuits, is used as a test problem.

#### 1. INTRODUCTION

While circuit simulators (e.g. [1].[2]) can provide accurate time-domain current and voltage waveforms from a device level description of an integrated circuit, as the size of the circuit increases the cost and memory requirements of such an analysis become prohibitive. For small circuits, the simulation time is generally dominated by the time required to evaluate device medel equations [3] but as circuit size increases, or if more efficient modeling techniques are used, an increasing fraction of time is spent solving the sparse-matrix circuit equations [1].

Timing simulators decouple the circuit equations using nonlinear simultaneous displacement [4] or successive displacement [5],[6] methods. For most circuits, this decoupling maintains a linear relationship between the number of circuit elements and the simulation time required per timepoint of the analysis. An added advantage of the decoupled analysis is that event-driven selective trace algorithms may be used easily and independent control of the timestep at any node of the circuit is also possible. These techniques can provide substantial savings in large digital circuits where often only a small fraction of the circuit nodes are actively changing state at any one time [7].

A major drawback with the use of timing analysis is that tightly-coupled feedback loops, or bidirectional circuit elements, can cause severe

inaccuracies and even instability during the analysis. For this reason, special techniques must be used to process such elements. One such element that has limited the application of timing analysis is the floating capacitor [8].

# 2. ALGORITHMS FOR FLOATING CAPACITORS

Floating capacitors play an important role in the analysis of MOS circuits. Often, the solution of networks containing arbitrary interconnections of a large number of floating capaciters is required. Such an analysis performed with ordinary implicit methods [9] would be extremely time consuming, because it requires the solution of a set of equations at each timestep. The use of explicit methods would reduce the computational effort, but requires small stepsize for stability reasons. The use of mixed implicit-explicit algorithms reduces the computational effort and allows, under certain conditions, the choice of optimal stepsize with regard to accuracy considerations while ensuring stability.

Two classes of algorithms are described here and referred to as "variable-in-space" and "variable-in-time" algorithms. We define an algorithm to be "variable-in-space" if different types of integration (implicit or explicit) are used for different components of the circuit at the same timepoint. We define an algorithm to be "variable-in-time" if different types of integration are used for the whole circuit at different timepoints. In the general case an algorithm can be both variable in space and time and different timesteps are used for implicit and explicit integration.

In the circuit that we use to test the algorithm we suppose that capacitors and conductances are linear for ease of proving algorithmic properties. For MOS circuits, where each node is assumed to have a capacitance to ground [7], the node equations are of the form:

$$Cx = Gx \quad x(0) = x_0 \quad x \in \mathbb{R}^n \quad C_{\cdot}(C \in \mathbb{R}^{(n \times n)}) \tag{1}$$

where x is the vector of node voltages. Eq.(1) can be rewritten in normal form[10]:

$$\dot{z} = Az A z R^{(n+n)} \tag{2}$$

with  $A = C^{-1}C$ . In order to study stability, we associate to each algorithm a companion matrix  $M \in \mathbb{R}^{(n \times n)}$  such that:

$$x_{k+p} = M_p x_d \tag{3}$$

Then to ensure stability of the method we require the spectral radius  $\frac{1}{r}(U_p) \le 1$  being all eigenvalues of modulus unity simple [11].

There are two basic approaches to "variable-in-space" algorithms. "partitioning of variables" or "guess of variables". The former requires an implicit integration on a subset of variables and an explicit integration for the remaining ones [12]. The latter is based on the guess at step k+1 of some quantities which are related to the values they had at the previous steps  $k,k-1,\dots,k-q$ . In this paper we concentrate on the "guess of variables" method. Suppose we are integrating the set of equations defined by Eq.(2) using an implicit method such as Backward Euler (B.E.). At each step we have to solve the linear system:

$$[I-hA]x_{k,j}=x_k \tag{4}$$

To solve Eq.(4) we need a L.U. factorization of [I-M], which is very time consuming if we are dealing with a large system. Let us decompose A into the sum of two matrices

$$A = A_{\ell} + A_{\sigma} \tag{5}$$

being  $A_t$  either lower or upper triangular. Eq.(4) is equivalent to

$$[I-A_k]x_{k+1} = x_k + A_k x_{k+1} \tag{6}$$

If we make the "guess"  $A_{x}x_{k+1}=A_{x}x_{k}$  we must solve:

$$[I-hA_{i}]x_{k+1}=[I+hA_{i}]x_{k}$$

(7)

where we do not need any factorization since  $[I-hA_t]$  is triangular. The companion matrix is  $M_t = [I-hA_t]^{-1}[I+hA_t]$ .

We will now restrict our analysis to the unitcell which models a MOS transistor for timing analysis. From the circuit point of view we can refer to voltage guess methods and current guess methods:

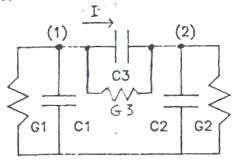

· Fig.1 Floating Capacitor Test Problem

(a) Let us consider first the most simple voltage guess method. Let us use B.E. integration, substitute the companion model for capacitors and apply nodal analysis to the circuit of Fig (1). By taking  $A = C^{-1}C$  in Eq.(4) and multiplying both members by  $\frac{C}{h}$  we obtain:

$$\left[\frac{C}{h} - C\right] x_{k+1} = \frac{C}{h} x_k \tag{8}$$

or more explicitly:

$$=\begin{bmatrix} \frac{C_1 + C_2}{h} & -C_3 - \frac{C_3}{h} \\ -C_3 - \frac{C_3}{h} & G_2 + G_3 + \frac{(C_2 + C_3)}{h} \end{bmatrix} \begin{bmatrix} v^1 \\ v^2 \end{bmatrix}$$

$$= \begin{bmatrix} \frac{C_1 + C_2}{h} & -\frac{C_3}{h} \\ -\frac{C_3}{h} & \frac{(C_2 + C_3)}{h} \end{bmatrix} \begin{bmatrix} v^1 \\ v^2 \end{bmatrix}$$

(9)

Let us use the guess  $v_{k+1}^2 = v_k^2$  in the first equation Then:

$$\begin{vmatrix}

(C_1 + C_3) & & & & & \\

-C_3 - \frac{C_3}{h} & & C_2 + C_3 + \frac{(C_2 + C_3)}{h}

\end{vmatrix}

\begin{bmatrix}

v^1 \\

v^2 \\

\frac{C_3}{h} & \frac{(C_2 + C_3)}{h}

\end{bmatrix}$$

and the companion matrix is

The method is absolutely stable for the test circuit. Fig.(2) shows the root locus and all roots stay within the unit circle for all values of circuit parameters

If  $C_1$  and  $C_2$  are small with respect to  $C_3$ ,  $C_3>0$  and the stepsize is increased, a pair of complex-conjugate roots appears. These roots may cause an oscillatory error component in the resulting circuit wave/orms, and therefore degrade the accuracy of the analysis. As it can be seen from the root locus, there exists a critical maximum timestep  $h_{\rm crit}$  under which the roots are real and the solution is accurate.

(b) Another voltage guess method described in [8] can be achieved by decoupling Eq.(9) by taking the voltage at node (2) one step back in time to solve the first equation. This corresponds to guess

The spectral radius of a matrix M is defined to be  $\rho(M) = \max\{|\lambda| | \lambda \varepsilon \sigma(M)\}$  where  $\sigma$  is the set of all the eigenvalues (spectrum) of M

Fig. 2 Root Locus for Method (a)

$G_3v_k^{2}_{k+1}=G_3v_k^{2}$  and considering the current i through the floating capacitor as given by  $\frac{G_3}{2\hbar}\left[(v_{k+1}^{1}-v_{d}^{1})-(v_{k}^{2}-v_{d+1}^{2})\right]$ . Stability considerations are similar to method (a) though ringing appears in the case  $G_3=0$ , and  $h_{ent}$  has different values. Fig(2) shows the root locus versus h for different values of the floating capacitor.

(c) To avoid the ringing in the solutions given by methods (a) and (b) we can perform a so called "double crossed voitage guess". We refer now to Eq.'s(2),(4) and (5) applied to the test circuit. The method has two steps, modeled as Eq.(6). In the first one,  $A_t = A_t$  is lower triangular and the guess  $A_{g1} v_{k+1}^2 = A_{g1} v_k^2$  is used in the first equation to solve for  $v_{k+1}^1$  and  $v_{k+1}^2$ . In the second step  $A_t = A_u$  is upper triangular and the guess  $A_{g2} v_{k+2}^1 = A_{g2} v_{k+1}^1$  is used in the second equation to solve for  $v_{k+2}^1$  and  $v_{k+2}^2$ . The companion matrix is:

$$M_2=[I-M_w]^{-1}[I+M_{p2}][I-M_t]^{-1}[I+M_{p1}]$$

(10)

The method is stable for the test circuit and the eigenvalues are real for all values of circuit parameters.

Now we consider current guesses.

(d) The first approach is to remove the floating elements and substitute them with a current source, whose value is determined by an explicit predictor. H.E. integration scheme is used for node voltages, and leads to the set of decoupled equations:

$$v_{k+1}^{1} = v_{k}^{1} + \frac{h}{C_{1}} \left( -C_{1} v_{k+1}^{1} - i P_{k+1} \right)$$

Fig.3 Root Locus for Method (b)

$$v_{k+1}^2 = v_k^2 + \frac{h}{C_2} \left( -C_2 v_{k+1}^2 + i_{k+1}^2 \right) \tag{11}$$

igni = iprodicted

The simplest predictor we can use is  $i_{k+1}^2 = i_k$  where  $i_k$  is the current computed from the circuit equation at timestep k. Another method consists of predicting the voltage on the floating element  $v_{k+1}^2$  by means of a forward Euler (F.E.) integration step and then solving for  $i_{k+1}^2$ . At each timestep the current  $i_k$  is evaluated and compared with  $i_k^2$ , if  $|i_k-i_k^2| > \epsilon$  the step is rejected and  $i_k^2$  is computed again with smaller stepsize. A more formal way of viewing the problem is to use modified needlanalysis for the circuit using  $i_k$  as appended variable and guessing its value as equal to the previous one. Using B.E. as the integration rule, we obtain:

$$\begin{bmatrix} 1+h\frac{C_1}{C_1} & 0 & 0 & 0 \\ 0 & 1+h\frac{C_2}{C_2} & 0 & 0 \\ 0 & 0 & 1+h\frac{C_3}{C_3} & -\frac{1}{C_3} \\ -1 & -1 & 0 \end{bmatrix} \begin{bmatrix} v^1 \\ v^2 \\ v^3 \\ i \end{bmatrix}_{k+1}$$

$$\begin{bmatrix} 1 & 0 & 0 & -\frac{1}{C_1} \\ 0 & 1 & 0 & \frac{1}{C_2} \\ 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & 0 \end{bmatrix} \begin{bmatrix} v^1 \\ v^2 \\ v^3 \\ i \end{bmatrix}_k$$

The method has proved to be unstable if  $C_2$  is large with respect to  $C_1$  and  $C_2$ , but stability does not depend on stepsize.

(e) We now take advantage of the possibility of computing exactly the time derivatives of the node voltages at each timestep and add these equations to the integrating equations for node voltages. Using B.E. integration scheme for the test circuit of Fig(1) we obtain:

$$\begin{vmatrix} 1 + \frac{h}{t1} & 0 & -mh & -ah \\ \frac{1}{t1} & 1 & -m & -a \\ -hn & -hb & 1 + \frac{h}{t2} & 0 \\ -n & -b & \frac{1}{t2} & 1 \end{vmatrix} \begin{bmatrix} v^1 \\ \dot{v}^1 \\ v^2 \\ \dot{v}^2 \\ k+t \end{vmatrix} = \begin{bmatrix} v^1 \\ 0 \\ v^2 \\ 0 \end{bmatrix}_k$$

$$t = \frac{C_1 + C_3}{C_1 + C_3} \quad t = \frac{C_2 + C_3}{C_2 + C_3} \quad a = \frac{C_3}{C_1 + C_3}$$

$$b = \frac{C_3}{C_2 + C_3} \quad m = \frac{C_3}{C_1 + C_3} \quad n = \frac{C_3}{C_2 + C_3}$$

by choosing as guess malrix:

$$A_{3} = \begin{bmatrix} 0 & 0 & -mh & -ah \\ 0 & 0 & -m & -a \\ 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 \end{bmatrix}$$

(13)

then:

$$A_k x_{k+1} = [I + A_g] x_k \tag{14}$$

and  $M=A_l^{-1}[I+A_g]$ . The stability of the method is not affected by the value of  $C_3$ , but the stepsize must be larger than a critical value. The major drawbacks are larger matrix dimension and the loss of accuracy if h is forced to be large. This might lead to the loss of fast transients when  $C_1$  and  $C_2$  are small with respect to  $C_2$ . In the case  $C_3=0$  only the guess  $\hat{v}_{k+1}^2=\hat{v}_k^2$  is performed which corresponds to guessing the current through  $C_2$ .

As a final remark, for the current-guess methods it should be pointed out that the best strategy as far as stability and accuracy are concerned is to guess the current through the smallest capacitor.

The following table summarizes stability considerations for the methods described above-

Next we focus our attention now on the "variable-in-time" algorithms. "Variable-in-time" algorithms have the advantage of reducing the total number of implicit integration steps and therefore the number of factorizations. In this case we combine a strictly stable algorithm (B.E.) with an explicit one (F.E.). We refer now to Eq.(2) and consider first the case where we have each

| c        | BOY               | Any   | i h>here             | Ves              | no no     |

|----------|-------------------|-------|----------------------|------------------|-----------|

| b        | any:              |       |                      |                  |           |

| b        | any               | RNY   | h < hent             | yes              | YCS       |

| a        | 1 0               | any   |                      |                  |           |

| <u> </u> | any               | any   | h>hend               | ves              | yes<br>no |

| u crpod  | <u>ပြာ</u><br>any | t any | h < h <sub>ent</sub> | stability<br>yes | DECUENC   |

<sup>\*</sup> for no ringing

Table 1. Stability and accuracy of guess methods

implicit step with stepsize h, followed by an explicit one with stepsize h, The companion matrix is:

$$M_{z}=[l+h_{f}A][l-h_{b}A]^{-1}$$

(15)

By the spectral mapping theorem [13]:

$$\sigma(M_2) = \left\{ \frac{1 + h_f \lambda}{1 - h_b \lambda} \mid \lambda \varepsilon \sigma(\Lambda) \right\}$$

(16)

and stability is ensured if  $\rho(M_2)<1$ . The algorithm is stable if:

$$h_0 - h_f > \frac{2 \operatorname{Re} \lambda}{|\lambda|^2} |\lambda \varepsilon \sigma(A)|$$

(17)

This condition requires the knowledge of the eigenvalues  $\lambda$  of  $\Lambda$ . It is easy to see that by taking  $h_b \ge h_f$ , condition (17) is always satisfied, previded we deal with a stable system. As a further generalization of this class of algorithms let  $\tau$  implicit steps with stepsize  $h_{bf}$  be mixed with s explicit steps with stepsize  $h_{ff}$ , where s+r=p and s, r coprime. In this case:

$$\sigma(M_p) = \begin{cases} \frac{\prod\limits_{f=1}^{p} (1 + h_{ff} \lambda)}{\prod\limits_{f=1}^{p} (1 - h_{bf} \lambda)} & | \lambda \varepsilon \sigma(A) \end{cases}$$

(18)

and stability is ensured by  $\rho(N_p) < 1$

### 3. SUMMARY

This brief overview of mixed algorithms is far from exhaustive. Its purpose is only to point out the potential reduction in total computational effort provided by these methods and the related stability problems. The stability analyses must be extended to more general networks typical of large integrated circuits. At present, some of the algorithms are under test in a timing simulator and will be used for the analysis of large MOS circuits.

#### 4. REFERENCES

- [1] L. W. Nagel, "SPICE2: A Computer Program to Simulate Semiconductor Circuits," ERL Memo No. ERL-M520, University of California, Berkeley, May 1975.

- [2] W. T. Weeks, A. J. Jiminez, G. W. Mahoney, D. Mehta, H. Qassemzadeh, and T. R. Scott, "Algorithms for ASTAP A Network Analysis Program," Trans. IEEE, vol.CT-20, pp 628-634, Nov. 1973.

- [3] A. R. Newton and D. O. Pederson, "Analysis Time, Accuracy and Memory Requirement Tradeoffs in SPICE2," 11th Asilomar Conference on Circuits, Systems and Computers, pp.6-9, Asilomar, Ca. Nov. 1977.

- [4] B. R. Chawla, H. K. Gummel and P. Kozak, "MOTIS An MOS Timing Simulator," Trans. IEEE, Vol.CAS-22, No 13, pp.901-909, Dec. 1975.

- [5] S. P. Fan, M. Y. Hsueh, A. R. Newton and D. O. Pederson, "MOTIS-C: A New Circuit Simulator for MOS LSI Circuits," Proc. IEEE Int. Symp. Circuits Syst., pp. 700-703, April 1977.

- [6] G.R. Boyle, "Simulation of Integrated Injection Logic," ERL Memo No. ERL-M78/13, University of California, Berkeley, March 1978.

- [7] A. R. Newton, "Techniques for the Simulation of Large-Scale Integrated Circuits," Trans. IEEE, vol.CAS-26, No.9, pp.741-749, Sept. 1979.

- [8] A. R. Newton, "The Analysis of Floating Capacitors for Timing Simulation," Proc. Thirtcenth Asilomar Conference on Circuits, Systems and Computers, Asilomar, Ca. Nov. 1979.

- [9] C. W. Gear, "Numerical Initial Value Problems in Ordinary Differential Equations", Englewood Cliffs, NJ Prentice-Hall, 1971.

- [10] C. A. Desoer and E. S. Kuh, "Basic Circuit Theory," McGraw-Hill, 1975.

- [11] O. Nevanlinna and W. Liniger, "Contractive Methods for Stiff Differential Equations," IBM Research Report No. RC-7122.

- [12] R. A. Rohrer, "Passive Algorithms and Stable Computation," to be published.

- [13] F. R. Gantmacher, "Theorie des Matrices," Dunod 1966.

This work was supported in part by NESC under contact number N39-Order#4. A. R. Newton also acknowledges partial support by NSF under grant ENG-7824425.