# Multiple-Independent-Gate Field-Effect Transistors for High Computational Density and Low Power Consumption

#### THÈSE Nº 6884 (2016)

PRÉSENTÉE LE 11 JANVIER 2016

À LA FACULTÉ INFORMATIQUE ET COMMUNICATIONS

LABORATOIRE DES SYSTÈMES INTÉGRÉS (IC/STI)

PROGRAMME DOCTORAL EN MICROSYSTÈMES ET MICROÉLECTRONIQUE

#### ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

PAR

Jian ZHANG

acceptée sur proposition du jury:

Prof. Y. Leblebici, président du jury Prof. G. De Micheli, directeur de thèse Dr W. M. Weber, rapporteur Dr M. Vinet, rapporteuse Prof. E. Matioli, rapporteur

## Acknowledgements

Pursuing the Ph.D. degree at EPFL has been an amazing experience for me. This could not be achieved without all the people who support me throughout these years. Firstly, I would like to express my sincere gratitude to my advisor Prof. Giovanni De Micheli for providing me this great opportunity to participate in doing research under his supervision, for letting me work on this interesting and comprehensive project in a comfortable environment at this beautiful place, for his continuous support of my Ph.D. study. All of my achievements would not have been possible without his trust and patience.

I would like to also gratefully thank Dr. Pierre-Emmanuel Julien Marc Gaillardon, the post-doctoral assistant who supervised me during my whole Ph.D. study. His guidance helped me in all the time of research. I have learned a lot from him, from his knowledge contributing to the technical work of this thesis, and from his patience in revising all my publications.

I would like to express my appreciation to the members of my thesis committee: Prof. Yusuf Leblebici, Prof. Elison Matioli, Dr. Maud Vinet, and Dr. Walter Michael Weber, for their time in reading this dissertation, for their insightful comments and encouragement. I would like to especially thank Dr. Walter Michael Weber for his support during my visit in NaMLab.

My sincere thanks also goes to all of my colleagues in Integrated Systems Laboratory, especially Mme. Christina Govoni for helping me with all the administrative work. I would like to thank Dr. Michele De Marchi and Dr. Davide Sacchetto for their pioneering work and fruitful advices on fabrication. I thank Dr. Shashi Kanth Bobba, Dr. Luca Amaru, Xifan Tang, and Hassan Ghasemzadeh Mohammadi for the collaboration work broadening my vision and knowledge.

I am grateful to all the CMi staff at EPFL for giving me the access to the facilities and the continuous help with advices, discussions and equipment maintenance. I also thank Jens Trommer, Dae-Young Jeon and all NaMLab members for the collaboration and help.

I would like to thank Hu, Wenqi, Xifan, Dechao, Zhendong and all of my friends, who let me enjoy the life in Switzerland and the happy time we spent together.

Last but not the least, I would like to thank my family: my parents Peiyi Zhang and Xiuqin Jia, and Linna for supporting me spiritually. Their existence provides me the infinite motivation and courage to finally achieve the goal.

Lausanne, December 2015

Jian Zhang

### **Abstract**

Transistors are the fundamental elements in *Integrated Circuits* (IC). The development of transistors significantly improves the circuit performance. Numerous technology innovations have been adopted to maintain the continuous scaling down of transistors. With all these innovations and efforts, the transistor size is approaching the natural limitations of materials in the near future. The circuits are expected to compute in a more efficient way. From this perspective, new device concepts are desirable to exploit additional functionality. On the other hand, with the continuously increased device density on the chips, reducing the power consumption has become a key concern in IC design.

To overcome the limitations of *Complementary Metal-Oxide-Semiconductor* (CMOS) technology in computing efficiency and power reduction, this thesis introduces the multiple-independent-gate *Field-Effect Transistors* (FETs) with silicon nanowires and FinFET structures. The device not only has the capability of polarity control, but also provides dual-threshold-voltage and steep-subthreshold-slope operations for power reduction in circuit design.

By independently modulating the Schottky junctions between metallic source/drain and semiconductor channel, the dual-threshold-voltage characteristics with controllable polarity are achieved in a single device. This property is demonstrated in both experiments and simulations. Thanks to the compact implementation of logic functions, circuit-level benchmarking shows promising performance with a configurable dual-threshold-voltage physical design, which is suitable for low-power applications.

This thesis also experimentally demonstrates the steep-subthreshold-slope operation in the multiple-independent-gate FETs. Based on a positive feedback induced by weak impact ionization, the measured characteristics of the device achieve a steep subthreshold slope of 6 mV/dec over 5 decades of current. High  $I_{\rm on}/I_{\rm off}$  ratio and low leakage current are also simultaneously obtained with a good reliability. Based on a physical analysis of the device operation, feasible improvements are suggested to further enhance the performance.

A physics-based surface potential and drain current model is also derived for the polarity-controllable *Silicon Nanowire FETs* (SiNWFETs). By solving the carrier transport at Schottky junctions and in the channel, the core model captures the operation with independent gate control. It can serve as the core framework for developing a complete compact model by integrating advanced physical effects.

#### Abstract

To summarize, multiple-independent-gate SiNWFETs and FinFETs are extensively studied in terms of fabrication, modeling, and simulation. The proposed device concept expands the family of polarity-controllable FETs. In addition to the enhanced logic functionality, the polarity-controllable SiNWFETs and FinFETs with the dual-threshold-voltage and steep-subthreshold-slope operation can be promising candidates for future IC design towards low-power applications.

**Keywords:** Gate-all-around, nanowire, FinFET, Schottky barrier, polarity control, multi-threshold-voltage, steep subthreshold slope, fabrication, simulation, compact modeling, logic design, tunneling, impact ionization, feedback, leakage, low power

## Résumé

Les transistors sont les éléments fondamentaux des circuits intégrés (IC). Le développement des transistors améliore significativement la performance du circuit. De nombreuses innovations technologiques ont été adoptées pour maintenir la réduction continue des dimensions des transistors. Grâce à ces innovations, la taille des transistors approchera les limites naturelles des matériaux dans un proche avenir. Par ailleurs, les circuits doivent calculer d'une manière plus efficace. Dans cette perspective, de nouveaux concepts de dispositifs sont souhaitables pour disposer de fonctionnalités supplémentaires. D'autre part, avec l'augmentation de la densité des puces, la réduction de la consommation d'énergie est devenue une préoccupation majeure dans la conception IC.

Pour surmonter les limites de la technologie CMOS en termes d'efficacité de calcul et de réduction de la puissance, cette thèse présente des transistors à effet de champ (FET) à multiples grilles indépendantes utilisant des nanofils de silicium et des structures FinFET. Le dispositif a non seulement la capacité de contrôler sa polarité, mais offre également des propriétés de double tension de seuil ou de forte pente sous le seuil afin de permettre réduction de la puissance des circuits.

En modulant indépendamment les barrières Schottky entre les contacts métalliques de source ou de drain et le canal semi-conducteur, des propriétés de double tension de seuil et de polarité contrôlable sont atteintes en un seul et même transistor. Cette propriété est démontrée expérimentalement et par simulation. Grâce à la réalisation compacte de fonctions logiques, notre analyse au niveau du circuit montre des performances prometteuses pour la conception de circuits à double tension de seuil configurable et son intérêt pour des applications de faible puissance.

Cette thèse démontre également expérimentalement le fonctionnement à pente sous le seuil raide dans des FETs à grilles multiples indépendantes. Basées sur une rétroaction positive induite par une ionisation par impact faible, les caractéristiques mesurées des transistors atteignent une pente sous le seuil raide de 6 mV/dec sur plus de 5 décades de courant. Un fort rapport  $I_{\rm on}/I_{\rm off}$  et un faible courant de fuite sont également simultanément obtenus avec une bonne fiabilité. Basées sur une analyse physique du fonctionnement du dispositif, de possibles améliorations sont suggérées pour améliorer encore la performance.

Un modèle compact physique du potentiel de surface et du courant de drain est également

#### Résumé

dérivé pour les transistors à nanofils de silicium (SiNWFETs) à polarité contrôlable. En dérivant le transport de porteurs de charge au niveau des jonctions de Schottky et dans le canal, le modèle capture le fonctionnement des grilles de commande indépendantes. Ce modèle peut servir de base pour l'élaboration d'un modèle compact plus complet intégrant des effets physiques avancés.

Pour résumer, les SiNWFETs et FinFETs à grilles indépendantes multiples sont largement étudiés en termes de fabrication, modélisation et simulation. Le concept de dispositif proposé élargit la famille de FET à polarité contrôlable. En plus de disposer de fonctions logiques améliorées, les SiNWFETs et FinFET à polarité contrôlable possèdent une double tension de seuil et un fonctionnement en pente sous le seuil raide et peuvent ainsi être des candidats prometteurs pour la conception des circuits intégrés du futur pour des applications de faible puissance.

**Mots-clés :** grilles enrobantes, nanofil, FinFET, barrière de Schottky, contrôle de la polarité, tensions de seuil multiples, pente sous seuil raide, fabrication, simulation, modélisation compacte, conception logique, effet tunnel, ionisation par impact, rétroaction, fuites, faible puissance

## **Contents**

| A  | cknov | wledgements                                     | j   |

|----|-------|-------------------------------------------------|-----|

| Al | ostra | ct (English/Français)                           | iii |

| Li | st of | figures                                         | X   |

| Li | st of | tables                                          | X   |

| 1  | Intr  | roduction                                       | 1   |

|    | 1.1   | Technologies Towards "More Moore"               | 3   |

|    |       | 1.1.1 Innovations in CMOS Technology            | 3   |

|    |       | 1.1.2 Beyond-CMOS Technologies                  | 6   |

|    | 1.2   | Current Limitations of CMOS Technology          | 7   |

|    |       | 1.2.1 Computing Efficiency                      | 7   |

|    |       | 1.2.2 Multi-Threshold-Voltage Design            | 8   |

|    |       | 1.2.3 Supply Voltage Lowering                   | 10  |

|    | 1.3   | Global Objectives                               | 13  |

|    | 1.4   | Thesis Contributions                            | 13  |

|    | 1.5   | Thesis Organization                             | 15  |

| 2  | Dev   | rice Structure and Fabrication                  | 17  |

|    | 2.1   | Functionality-Enhanced Transistors              | 17  |

|    |       | 2.1.1 Schottky-Barrier FETs                     | 17  |

|    |       | 2.1.2 Functionality-Enhanced Transistors        | 19  |

|    | 2.2   | Structure of Multiple-Independent-Gate FETs     | 22  |

|    | 2.3   | Device Fabrication                              | 23  |

|    | 2.4   | Chapter Summary                                 | 33  |

| 3  | Dua   | al-Threshold-Voltage Characteristics and Design | 35  |

|    | 3.1   | Multi-Threshold-Voltage Technologies            | 35  |

|    |       | 3.1.1 Threshold Voltage in MOSFETs              | 35  |

|    |       | 3.1.2 Process Engineering                       | 36  |

|    |       | 3.1.3 Body Biasing                              | 37  |

|    | 3.2   | Device Operation                                | 39  |

|    |       | 3.2.1 Operation States                          | 39  |

#### **Contents**

|   |      | 3.2.2 Single-Input Configuration                         | 41           |

|---|------|----------------------------------------------------------|--------------|

|   |      | 3.2.3 Two-Inputs Configuration                           | 42           |

|   | 3.3  | Device Characterization                                  | 42           |

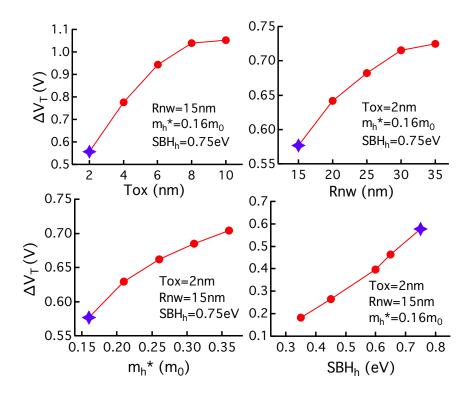

|   | 3.4  | Discussion on Dual-V $_T$ characteristics                | 45           |

|   |      | 3.4.1 Origin of Dual Threshold Voltages                  | 45           |

|   |      | 3.4.2 Effects of Structural and Physical Parameters      | 46           |

|   | 3.5  | Circuit and Physical Design                              | 48           |

|   |      | 3.5.1 Dual-Threshold-Voltage Design                      | 49           |

|   |      | 3.5.2 Additional Logic Implementation                    | 50           |

|   |      | 3.5.3 Uncommitted Logic Gate Pattern                     | 55           |

|   |      | 3.5.4 Connection Schemes for Uncommitted Gate Pattern    | 55           |

|   | 3.6  | Architectural Benchmarking                               | 56           |

|   |      | 3.6.1 Methodology                                        | 56           |

|   |      | 3.6.2 Table-Based Device Model                           | 57           |

|   |      | 3.6.3 Gate-Level Characterization                        | 60           |

|   |      | 3.6.4 Circuit-Level Results                              | 61           |

|   | 3.7  | Chapter Summary                                          | 63           |

| 4 | Stee | ep-Subthreshold-Slope Operation                          | 67           |

|   | 4.1  | Steep-Subthreshold-Slope Devices                         | 67           |

|   | 4.2  | Working Principle of Steep-Subthreshold-Slope DIG FinFET | 73           |

|   | 4.3  | Device Characterization                                  | 75           |

|   |      | 4.3.1 Room-Temperature Characterization                  | 75           |

|   |      | 4.3.2 Temperature-Dependent Characterization             | 78           |

|   |      | 4.3.3 Influence of Fin Width                             | 81           |

|   |      | 4.3.4 Influence of Potential Well under Gate             | 81           |

|   |      | 4.3.5 Reliability Assessment                             | 83           |

|   |      | 4.3.6 Low-Voltage Operation                              | 84           |

|   | 4.4  | Discussion                                               | 84           |

|   | 4.5  | Chapter Summary                                          | 89           |

| = | Con  | npact Modeling                                           | 01           |

| 5 |      | Structure of DIG Silicon Nanowire FET                    | <b>91</b> 92 |

|   | 5.1  |                                                          |              |

|   | 5.2  | Surface Potential Model                                  | 93           |

|   | 5.3  | Drain Current Model                                      | 96           |

|   | 5.4  |                                                          | 100          |

|   | 5.5  | Chapter Summary                                          | 104          |

| 6 | Con  | clusions and Future Work                                 | 105          |

|   | 6.1  | Summary of Contributions                                 | 105          |

|   | 6.2  | Future Work                                              | 106          |

| A | List | of Abbreviations                                         | 109          |

|                  | Contents |

|------------------|----------|

| Bibliography     | 131      |

| Curriculum Vitae | 135      |

# **List of Figures**

| 1.1  | Development of computers from ENIAC to Compute Stick                                      | 1  |

|------|-------------------------------------------------------------------------------------------|----|

| 1.2  | Combined need for digital and non-digital functionalities in an integrated sys-           |    |

|      | tem: "More Moore" and "More-than-Moore"                                                   | 2  |

| 1.3  | Strained silicon technology for enhancing the carrier mobility                            | 3  |

| 1.4  | (a) High- $\kappa$ material and metal gate replace SiO $_2$ and polysilicon gate, (b) TEM |    |

|      | image of hafnium-based high- $\kappa$ dielectric and metal gate stack                     | 4  |

| 1.5  | Evolution of MOSFET structures from planar MOSFET to FinFET and silicon                   |    |

|      | nanowire FET                                                                              | 5  |

| 1.6  | A classification of emerging logic devices based on the state variables and the           |    |

|      | switching mechanisms.                                                                     | 6  |

| 1.7  | Implementation of NAND and XOR functions with CMOS technology                             | 7  |

| 1.8  | Characteristics of low- $V_T$ and high- $V_T$ FinFETs extracted from PTM-MG 20 nm         |    |

|      | model                                                                                     | 8  |

| 1.9  | A simple way to estimate the delay of an inverter with a load capacitance $C_L$ .         | ç  |

| 1.10 | An example of multi-threshold-voltage design.                                             | 10 |

| 1.11 | Supply voltage lowering requires devices with a steeper subthreshold slope to             |    |

|      | maintain good switching properties                                                        | 11 |

| 1.12 | (a) Structure of a <i>n</i> -type MOSFET. (b) Band diagram showing the potential barrier  |    |

|      | lowered by increasing $V_G$                                                               | 12 |

| 2.1  | Conduction of both electrons and holes in a SB-FET and measured characteris-              |    |

|      | tics of SB-FET                                                                            | 18 |

| 2.2  | Schottky-barrier height engineering with dopant segregation technique and                 |    |

|      | improved performance with a fixed polarity                                                | 19 |

| 2.3  | Polarity-controllable transistors built with different device structures and mate-        |    |

|      |                                                                                           | 20 |

| 2.4  | Structure of three-independent-gate SiNWFET and dual-independent-gate FinFET.             | 23 |

| 2.5  | Cross-section of the SOI wafer and dimensions of the alignment markers                    | 25 |

| 2.6  | DRIE (Bosch) process applied to the fabrication of vertically-stacked silicon             |    |

|      | nanowires                                                                                 | 26 |

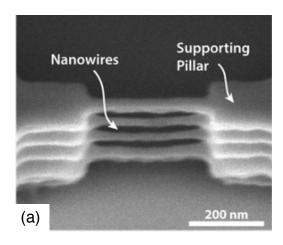

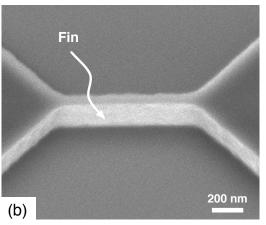

| 2.7  | Fabricated vertically-stacked silicon nanowires and fin                                   | 27 |

| 2.8  | Fabrication of polarity gates in the multiple-independent-gate FinFET                     | 28 |

|      |                                                                                           |    |

| 2.9  | Cross-sectional view of the vertically-stacked nanowires, polarity gates and        |    |

|------|-------------------------------------------------------------------------------------|----|

|      | e e e e e e e e e e e e e e e e e e e                                               | 29 |

| 2.10 | Tilted top view of the fabricated polarity gates and control gate on a fin-shaped   |    |

|      |                                                                                     | 29 |

| 2.11 | Principle of the formation of spacers at the edges after the anisotropic etching of |    |

|      |                                                                                     | 30 |

|      | Fabrication of spacers in the multiple-independent-gate FinFET                      | 31 |

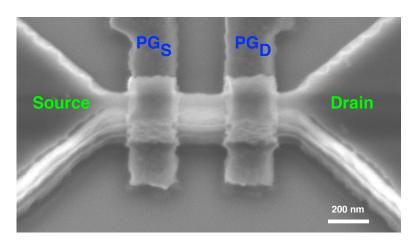

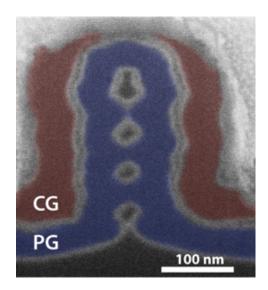

| 2.13 | SEM images of fabricated multiple-independent-gate SiNWFETs and FinFETs.            | 32 |

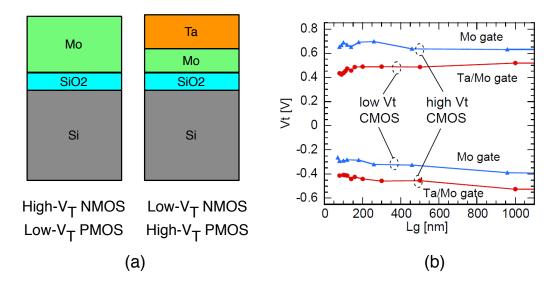

| 3.1  | Dual metal gate CMOS with Ta/Mo diffusion technology for multi- $V_T$ applications. | 37 |

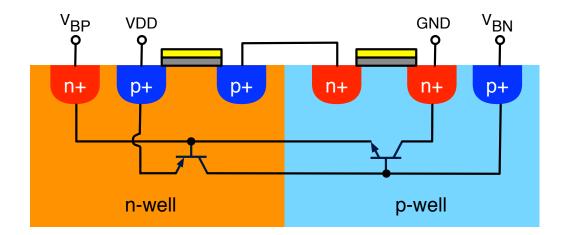

| 3.2  | Leakage path in bulk CMOS with forward body biasing                                 | 38 |

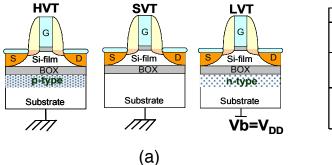

| 3.3  | FDSOI multi- $V_T$ devices obtained by applying doped BP and body bias              | 38 |

| 3.4  | Schematic of three-independent-gate SiNWFET                                         | 39 |

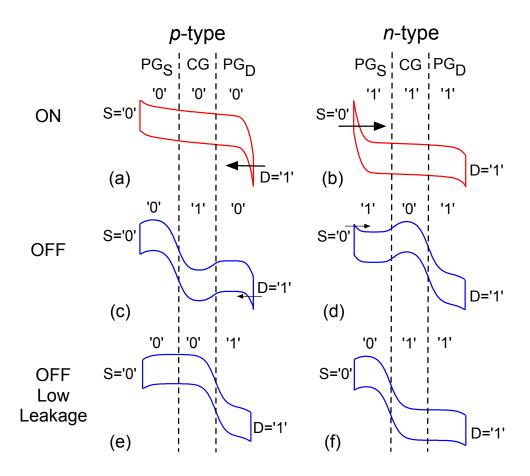

| 3.5  | ON, OFF and low-leakage OFF states and their corresponding band diagrams            | 40 |

| 3.6  | Bias configurations of TIG SiNWFET with a single input                              | 41 |

| 3.7  | Bias configurations of TIG SiNWFET for two inputs                                   | 42 |

| 3.8  | Measured characteristics of a three-independent-gate SiNWFET                        | 43 |

| 3.9  | Structure and simulation results of an optimized TIG SiNWFET                        | 47 |

| 3.10 | The $V_T$ difference of pFET configurations in simulated devices                    | 48 |

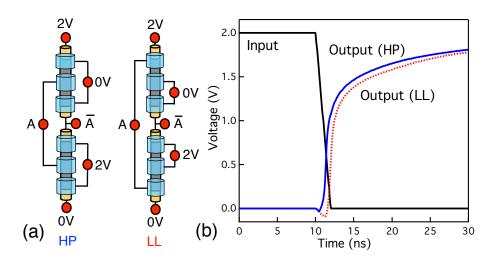

| 3.11 | The different connection schemes and transient simulation results of the invert-    |    |

|      | ers for high performance and low leakage applications                               | 49 |

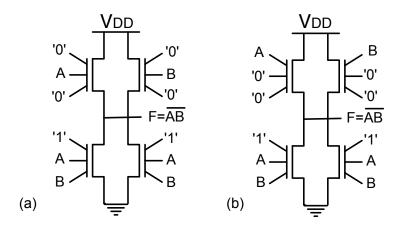

| 3.12 | Mapping of NAND gate towards high performance and low leakage applications.         | 50 |

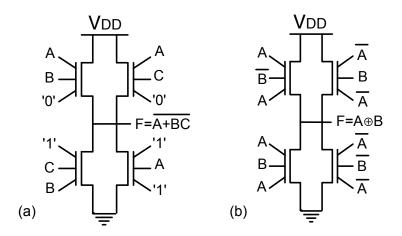

| 3.13 | AOI gate and XOR gate implemented with TIG SiNWFETs in a compact form               | 50 |

| 3.14 | Static CMOS logic function and conventional CMOS transmission gate                  | 51 |

| 3.15 | (a) XOR-based transmission gate, (b) Transmission gate with single polarity-        |    |

|      | controllable device. (c) Compact implementation of logic functions with polarity-   |    |

|      | controllable devices                                                                | 52 |

| 3.16 | Compact implementation of 1-bit full adder with TIG SiNWFETs                        | 52 |

| 3.17 | Mixed-mode TCAD simulation of the carry function                                    | 53 |

| 3.18 | TSPC DFF implemented with TIG SiNWFETs in a compact form and the equiva-            |    |

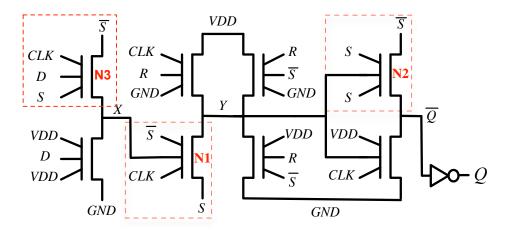

|      | lent gate-level circuit                                                             | 54 |

| 3.19 | A compact implementation of TSPC DFF with asynchronous set/reset functions          |    |

|      | with TIG SiNWFETs                                                                   | 54 |

| 3.20 | Uncommitted logic gate pattern                                                      | 55 |

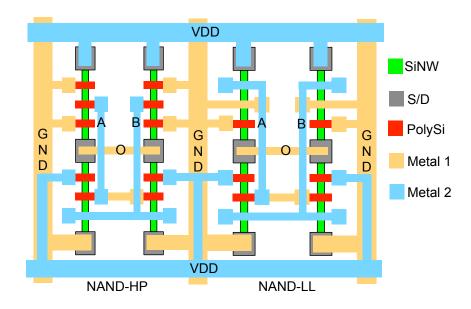

| 3.21 | Connection schemes of NAND gate towards HP and LL applications                      | 56 |

| 3.22 | Schematic of simulated 22-nm TIG SiNWFET                                            | 57 |

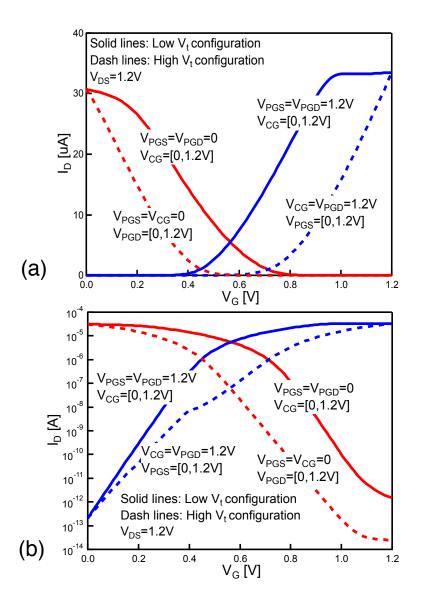

| 3.23 | Transfer characteristic of simulated 22-nm TIG SiNWFET illustrating the dual-V $_T$ |    |

|      | property in both linear and logarithmic scales                                      | 58 |

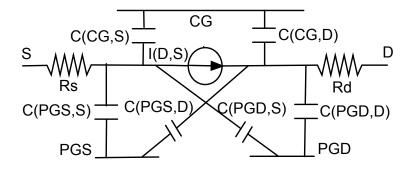

|      | Equivalent circuit model of TIG SiNWFET                                             | 59 |

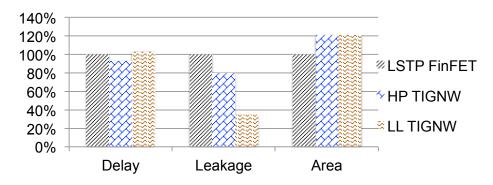

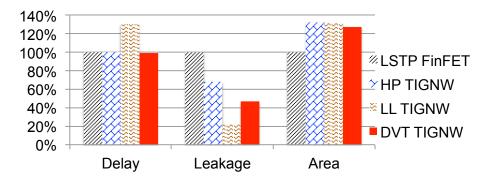

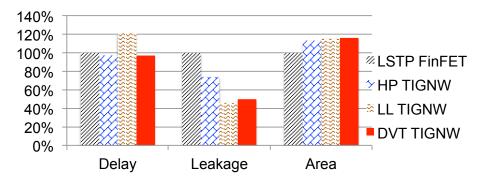

|      | Comparison results of logic gates with TIG SiNWFET and LSTP FinFET                  | 61 |

| 3.26 | Average comparison results of ISCAS'85 benchmark circuits with Dual-V $_T$ TIG      |    |

|      | SiNWFET and LSTP FinFET                                                             | 62 |

| 3.27 | Average comparison results of VTR benchmark circuits with Dual-V $_T$ TIG SiN-WFET and LSTP FinFET        | 62 |

|------|-----------------------------------------------------------------------------------------------------------|----|

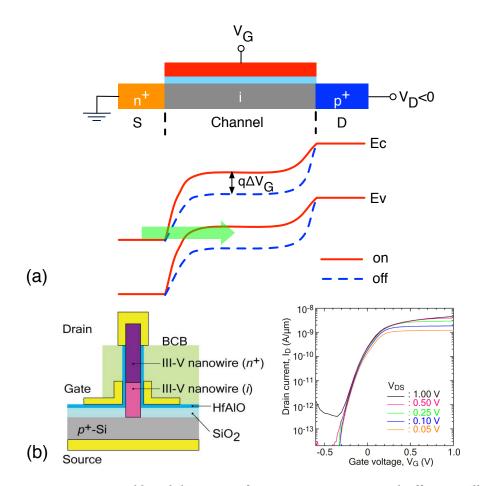

| 4.1  | (a) Structure and band diagrams of a <i>p</i> -type TFET at <i>on</i> and <i>off</i> states, illustrat-   |    |

|      | ing the working principle of the TFET. (b) <i>n</i> -type TFET based on vertical III-V                    |    |

|      | nanowire/Si heterojunction and the steep-SS characteristics                                               | 68 |

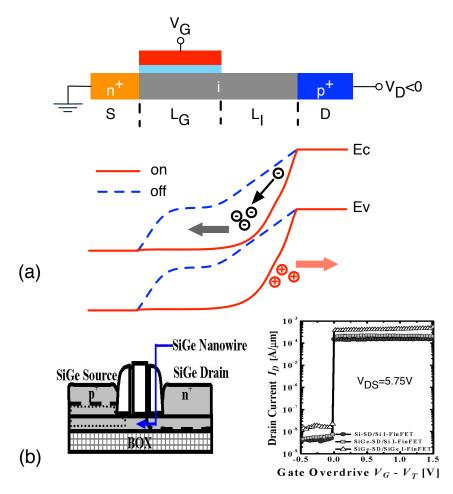

| 4.2  | (a) Structure and band diagrams of a <i>n</i> -type IMOS at <i>on</i> and <i>off</i> states, illustrating |    |

|      | the working principle of IMOS. (b) An IMOS with SiGe impact-ionization region,                            |    |

|      | and the steep-SS characteristics                                                                          | 69 |

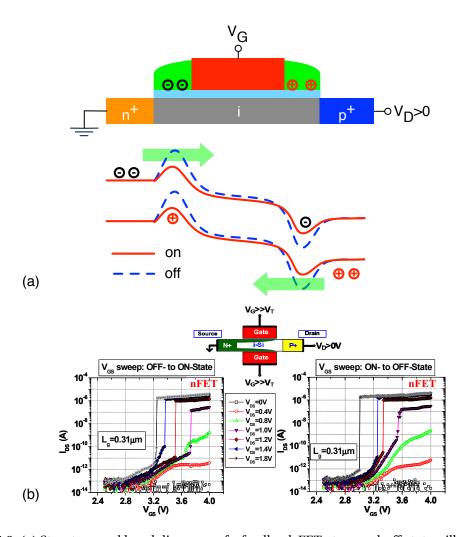

| 4.3  | (a) Structure and band diagrams of a feedback FET at <i>on</i> and <i>off</i> states, illus-              |    |

|      | trating the working principle. (b) the steep-SS characteristics in a feedback FET                         |    |

|      | during turn- <i>on</i> and turn- <i>off</i> , showing the large hysteresis                                | 70 |

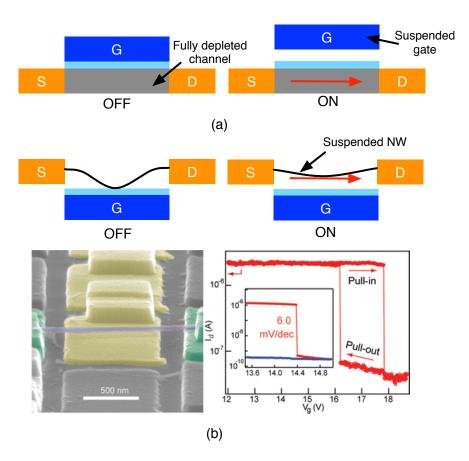

| 4.4  | NEMFETs with a suspended gate or a suspended nanowire channel                                             | 71 |

| 4.5  | Structures and equivalent capacitive partition schematic of conventional MOS-                             |    |

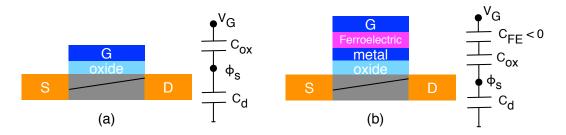

|      | FET and negative-capacitance FET.                                                                         | 72 |

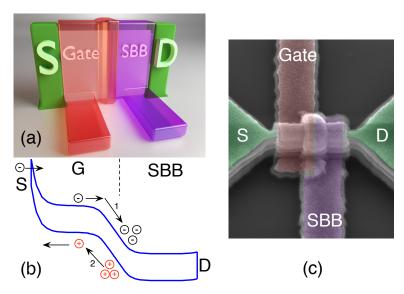

| 4.6  | Structure of a dual-independent-gate silicon FinFET                                                       | 73 |

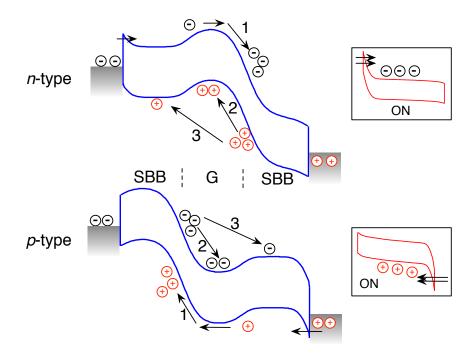

| 4.7  | Band diagram of $n$ -type and $p$ -type operation in DIG FinFET, showing the main                         |    |

|      | switching mechanisms                                                                                      | 74 |

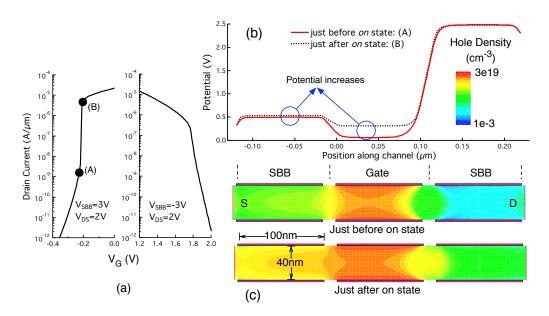

| 4.8  | TCAD simulation of DIG FinFET with steep-SS operation                                                     | 75 |

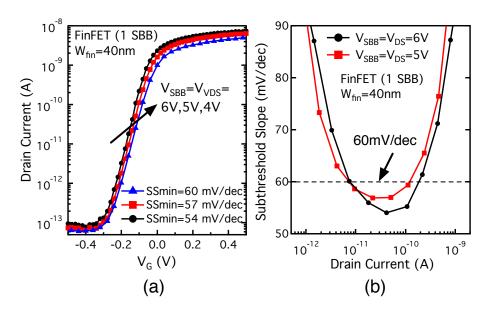

| 4.9  | Measured characteristics of the DIG FinFET at different $V_{DS}$ with $V_{SBB}$ =5V (room                 |    |

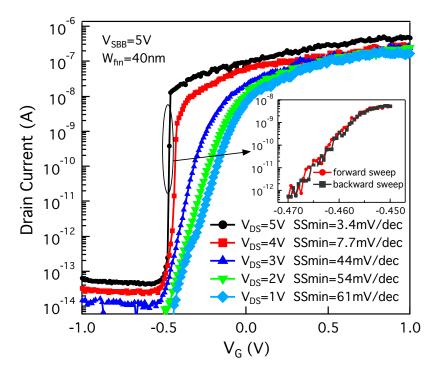

|      | temperature)                                                                                              | 76 |

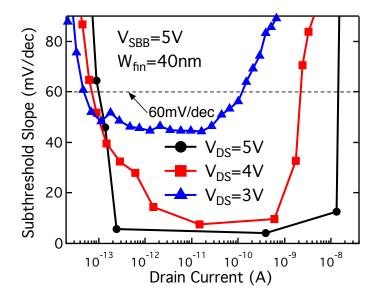

|      | SS as a function of drain current with different $V_{DS}$                                                 | 76 |

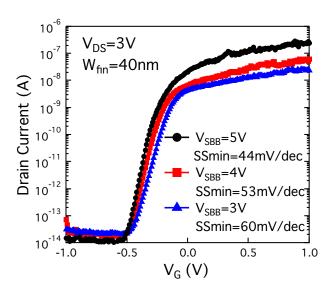

|      | $I_D - V_G$ characteristics at different $V_{SBB}$                                                        | 77 |

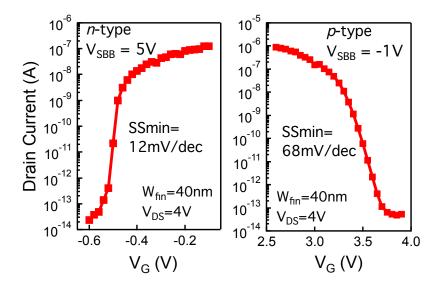

|      | Measured $n$ -type and $p$ -type characteristics in a DIG FinFET                                          | 77 |

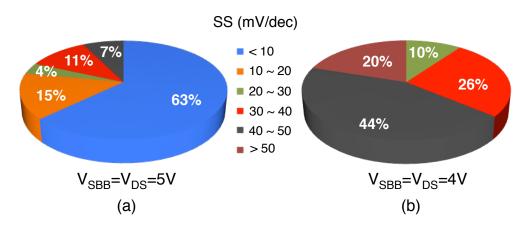

|      | Statistical distribution of SS of the DIG FinFETs under different operation voltages.                     | 78 |

|      | Ambipolar characteristics with steep SS in both $n$ -type and $p$ -type branches                          | 79 |

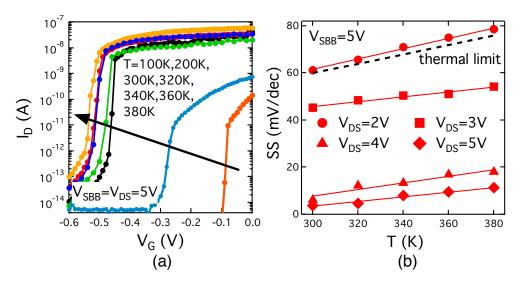

| 4.15 | <i>n</i> -type steep-SS characteristics and the extracted minimal SS at different tem-                    |    |

|      | peratures                                                                                                 | 79 |

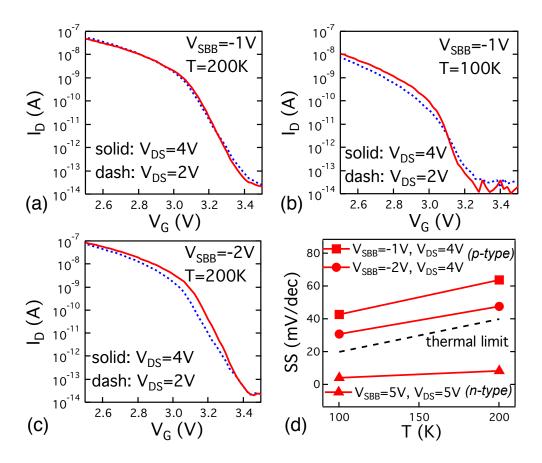

|      | p-type characteristics and SS with different $V_{\rm SBB}$ and $V_{DS}$ at 100 K and 200 K                | 80 |

| 4.17 | Measured characteristics in devices with different $W_{\text{fin}}$ and statistics of SS and              |    |

|      | $V_T$ based on all measured devices                                                                       | 81 |

|      | Sketch and operation of the FinFET with a single SBB region                                               | 82 |

|      | Characteristics of the FinFET with a single SBB region                                                    | 82 |

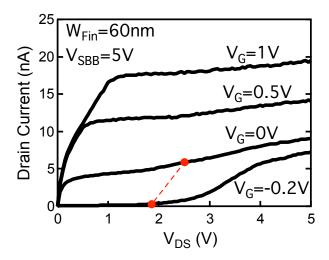

| 4.20 | Output characteristics of the DIG FinFET, indicating the impact ionization only                           |    |

|      | occurs during the transition.                                                                             | 83 |

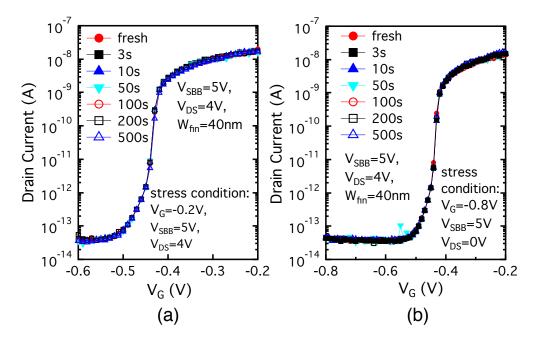

|      | Reliability assessment of the DIG FinFET during the steep-SS transition                                   | 84 |

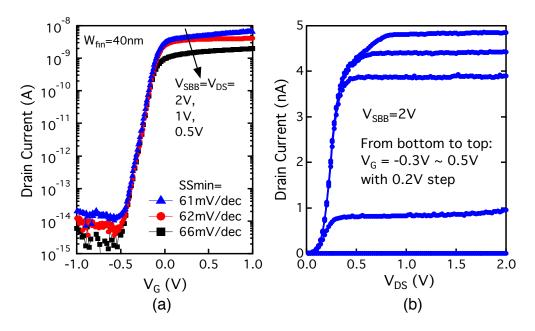

|      | Characteristics of DIG FinFET under low operation voltages                                                | 85 |

| 4.23 | (a) $V_{\rm B}$ indicates different positions in DIG FinFET and SOI MOSFET. (b) The back                  |    |

|      | bias $(V_{\text{sub}})$ applied to the SOI wafer shows no influence on the steep SS or $V_T$ in           |    |

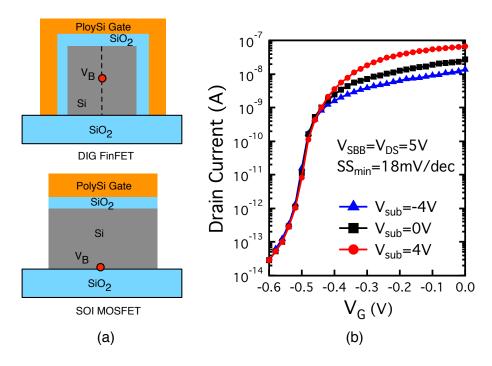

|      | DIG FinFET.                                                                                               | 86 |

| 4.24 | Extracted $dV_{BS}/dV_{GS}$ from the <i>n</i> -type characteristics shown in Fig. 4.15 at differ-         |    |

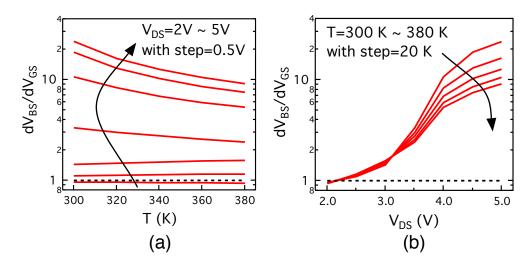

|      | ent temperatures (T) and $V_{DS}$                                                                         | 87 |

#### **List of Figures**

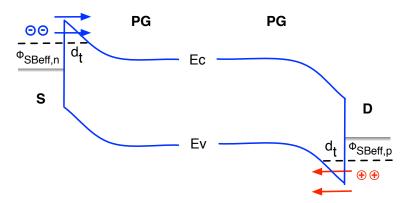

| 5.1  | Structure of a dual-independent-gate SiNWFET                                                 | 92   |

|------|----------------------------------------------------------------------------------------------|------|

| 5.2  | Band diagrams at $on$ and $off$ states in $n$ -type and $p$ -type configurations of a        |      |

|      | dual-independent-gate SiNWFET                                                                | 92   |

| 5.3  | Schottky barriers at source and drain under different bias conditions, showing               |      |

|      | the effective Schottky barrier heights for electrons and holes                               | 97   |

| 5.4  | Potential barrier induced by CG in the middle of the channel                                 | 97   |

| 5.5  | Equivalent circuit symbol of the dual-independent-gate SiNWFET                               | 99   |

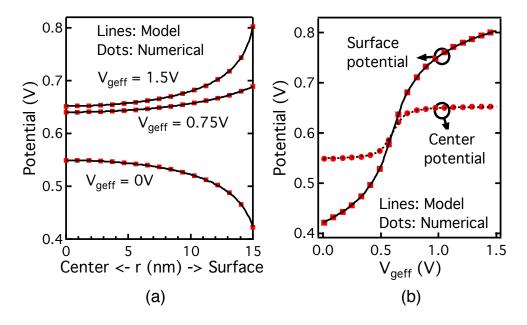

| 5.6  | Electrostatic potential predicted by the model and verified with numerical solution.         | .100 |

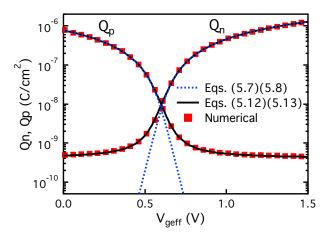

| 5.7  | Carrier density predicted by the model and verified with numerical solution. $$ .            | 101  |

| 5.8  | Surface potential distribution along the channel with different gate voltages                |      |

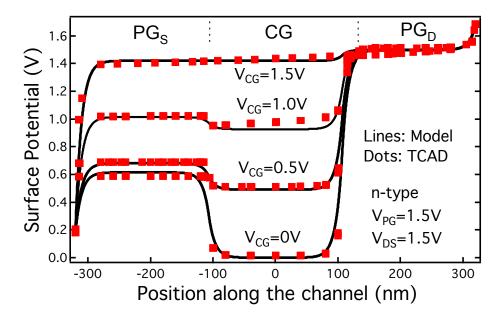

|      | ( <i>n</i> -type)                                                                            | 102  |

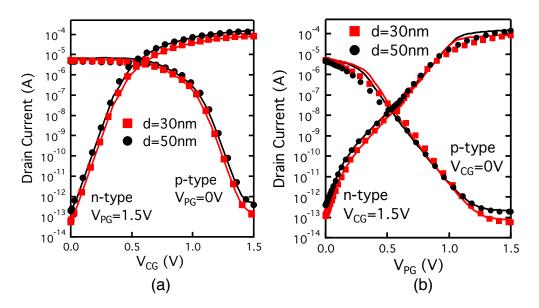

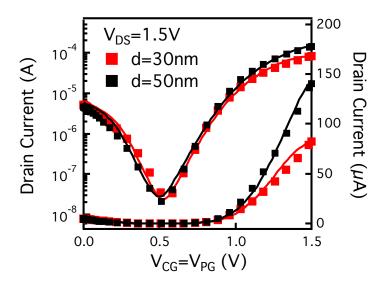

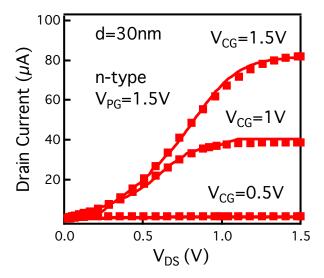

| 5.9  | The predicted drain current with different nanowire diameters under (a) a fixed              |      |

|      | $V_{\rm PG}$ and (b) a fixed $V_{\rm CG}$ for both $n$ -type and $p$ -type configurations    | 102  |

| 5.10 | Ambipolar characteristics by applying the same $V_{\rm CG}$ and $V_{\rm PG}$ in DIG SiNWFET. | 103  |

| 5.11 | Output characteristics with a fixed $V_{PG}$                                                 | 104  |

## **List of Tables**

| 2.1 | Process for fabricating alignment markers                                         | 24 |

|-----|-----------------------------------------------------------------------------------|----|

| 2.2 | Process for fabricating vertically-stacked silicon nanowires                      | 25 |

| 2.3 | Process for fabricating silicon fins                                              | 27 |

| 2.4 | Process for fabricating polarity gates                                            | 28 |

| 2.5 | Process for fabricating control gate                                              | 30 |

| 2.6 | Process for fabricating spacers                                                   | 31 |

| 2.7 | Process of silicidation                                                           | 32 |

| 3.1 | Limitations of conventional multi- $V_T$ technologies                             | 39 |

| 3.2 | Performance of simulated 22-nm TIG SiNWFET                                        | 59 |

| 3.3 | Performance of logic gates with TIG SiNWFET and LSTP FinFET                       | 60 |

| 3.4 | Delay, leakage, and area of ISCAS'85 benchmark circuits with dual-V $_T$ TIG SiN- |    |

|     | WFET and LSTP FinFET                                                              | 64 |

| 3.5 | Delay, leakage, and area of VTR benchmark circuits with dual-V $_T$ TIG SiNWFET   |    |

|     | and LSTP FinFET                                                                   | 65 |

| 4.1 | Suggestions for reducing $V_{DS}$ in steep-SS multiple-independent-gate FETs      | 89 |

### 1 Introduction

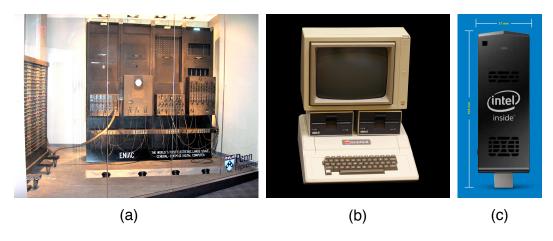

The first electronic general-purpose computer ENIAC was born in 1946 [1]. Since then, people have been keen on pursuing smaller but more powerful computers. After the invention of semiconductor devices and integrated circuits, there has been a fast development of computers for more than half a century [2–5]. Fig. 1.1 illustrates the development of computers from ENIAC to Personal Computer, and the recent Compute Stick. Thanks to the greatly enhanced computing capability of integrated circuits with a deeply scaled feature size, the whole system of computation, control, and memory perfectly fits in a small stick [6].

Figure 1.1: Development of computers, (a) ENIAC (part), (year 1946), (b) Apple-II, (year 1977), (c) Intel Compute Stick, (year 2015).

With such a speedy development, not only computers, but also consumer products containing semiconductor devices and integrated circuits have arrived at almost every corner of human society. They are changing every part of people's life.

This revolution greatly relies on the scaling down of transistors, which are the fundamental elements of integrated circuits [7]. The benefits from the scaling down of transistors was described by the famous "Moore's law" proposed by Gordon E. Moore in 1965 [8]. Generally, the scaling down of transistor size dramatically increases the device density on chips, and

decreases the relative cost, at an exponential pace.

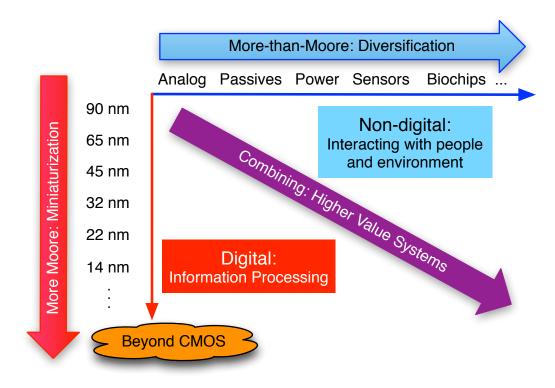

Driven by the benefits from downscaling, there is the need to maintain this trend, which is referred to as "More Moore". On the other hand, with the progress in both process technology and design, the capability of non-digital technologies is significantly enhanced. This brings the migration of non-digital components, such as analog circuits and sensors, into the package. Thus, the highly integrated systems can efficiently interact with people and environment. The so-called "More-than-Moore" trend is characterized by functional diversification of semiconductor-based devices. As shown in Fig. 1.2, the dual trend of "More Moore" and "More-than-Moore" summarizes the combined need for digital and non-digital functionalities in an integrated system [9].

Figure 1.2: The combined need for digital and non-digital functionalities in an integrated system is translated as a dual trend in the *International Technology Roadmap for Semiconductors* (ITRS): miniaturization of the digital functions ("More Moore") and functional diversification ("More-than-Moore") [9]

The technologies to maintain the trend of "More Moore" are introduced in Sec. 1.1. Then, Sec. 1.2 introduces the current limitations of CMOS technology on computing efficiency and power reduction. Sec. 1.3 discusses the global objectives of this thesis to overcome these limitations with the proposed device concept. Sec. 1.4 summarizes the contributions of the thesis. Finally, Sec. 1.5 gives the organization of this thesis at the end of this chapter.

#### 1.1 Technologies Towards "More Moore"

This section introduces the innovations in CMOS technology for continuous miniaturization, and beyond-CMOS technologies expected to keep the trend of "More Moore" when CMOS devices approach the material limit.

#### 1.1.1 Innovations in CMOS Technology

Numerous key technology innovations have been adopted in CMOS technology to keep the device performance while scaling down:

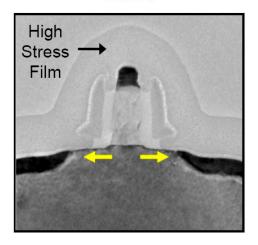

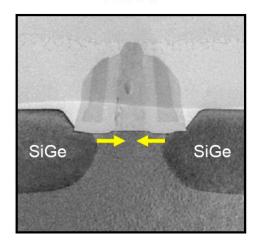

#### 1. Strained Silicon:

In CMOS technology, faster velocity of carriers (electrons and holes) can provide a higher current in *Metal-Oxide-Semiconductor Field-Effect Transistors* (MOSFETs), which consequently improves the performance of circuits. At low electric field, the drift velocity is proportional to the electric field strength, and the proportionality constant is defined as mobility of the carriers [10]. Therefore, increasing the mobility can boost the performance of CMOS circuits.

Study shows that by applying appropriate tensile or compressive stress to the channel, the energy band structure can be slightly tuned, resulting in the enhancement of the

#### **NMOS**

SiN cap layer Tensile channel strain

#### **PMOS**

SiGe source-drain

Compressive channel strain

Figure 1.3: Strained silicon technology for enhancing the carrier mobility. Tensile strain in the NMOS channel is created by adding a high-stress layer that wrapped around the transistor, while compressive strain in PMOS channel is created by replacing the conventional source/drain region with strained SiGe [11]

mobility of carriers [12]. Fig. 1.3 shows the technology to achieve strained silicon channel in both *N-type Metal-Oxide-Semiconductor* (NMOS) and *P-type Metal-Oxide-Semiconductor* (PMOS) [11]. The technology of strained silicon has been introduced since the technology node of 90 nm, which increases the saturated currents by  $10\% \sim 20\%$  and mobility by >50% [13].

#### 2. High- $\kappa$ Gate Oxide:

$SiO_2$  has served as gate insulator since the advent of MOS devices. As the scaling down of MOSFETs, the  $SiO_2$  layer became thiner and thiner to maintain the electrostatic control over the channel. Unfortunately, the leakage current through the thin layer of  $SiO_2$  also increased with decreased  $SiO_2$  thickness [14].

In order to continue the scaling down without sacrificing the leakage power, oxide materials with higher dielectric constant ( $\kappa$ ) have been introduced since the technology node of 45 nm [15]. The high- $\kappa$  materials such as HfO<sub>2</sub> provide sufficient electrostatic control (i.e., sufficiently small equivalent SiO<sub>2</sub> thickness) while having a much thicker physical thickness, which efficiently prevents the gate leakage.

#### 3. Metal Gate:

Polycrystalline silicon was used as the gate material for the easy integration with CMOS technology. In the meantime, the polysilicon gate also suffers from a high gate resistance and a depletion effect [16]. The depleted region in polysilicon behaves as an additional gate oxide, thus increasing the oxide thickness and reducing the electrostatic control [17].

Since the technology node of 45 nm, metal gates have replaced polysilicon gates to reduce the gate resistance and eliminate the depletion effect [15]. Moreover, the metal gates further enhance the benefits from the high- $\kappa$  dielectric by reducing the mobility degradation caused by the phonon scattering [18]. Fig. 1.4 shows the conceptual sketch and *Transmission Electron Microscopy* (TEM) image of high- $\kappa$  dielectric and metal gate stack [15].

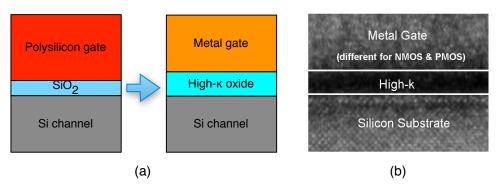

Figure 1.4: (a) High- $\kappa$  material and metal gate replace SiO<sub>2</sub> and polysilicon gate, (b) *Transmission Electron Microscopy* (TEM) image of hafnium-based high- $\kappa$  dielectric and metal gate stack [15].

#### 4. FinFET Structure:

When coming to the technology node of 22 nm, the planar bulk structure of MOSFETs cannot provide sufficient electrostatic control over such a short channel (Fig. 1.5(a)). *Short Channel Effects* (SCE) and *Drain-Induced-Barrier-Lowering* (DIBL) can severely degrade the device performance with such a short channel in a planar bulk structure [19,20].

In order to maintain the continuous downscaling, different device structures are investigated, including *Partially-Depleted* (PD) *Silicon-On-Insulator* (SOI), *Fully-Depleted* (FD) SOI, *Ultra Thin Body and Buried Oxide FD SOI* (UTBB-FD SOI), FinFET (Fig. 1.5(b)), and gate-all-around nanowires (Fig. 1.5(c)), etc. [21–33]. Yan *et al.* and Colinge studied a "natural length"  $\lambda$  in different device structures to characterize their scalability [34,35]. Smaller  $\lambda$  indicates a better electrostatic control with a short channel. The study shows that  $\lambda = \sqrt{(\varepsilon_{\rm Si}/\varepsilon_{\rm Ox}/N)t_{\rm Ox}t_{\rm Si}}$ , where N=1,2,4 for single-gate SOI, double-gate SOI (Fin-FET), and quadruple-gate (gate-all-around) structures, respectively. Therefore, FinFET has a smaller  $\lambda$  compared to single-gate structure with the same gate oxide ( $\varepsilon_{\rm Ox}, t_{\rm Ox}$ ) and silicon film ( $\varepsilon_{\rm Si}, t_{\rm Si}$ ). FinFET is consequently introduced in products at the 22 nm node [36]. The FinFET structure significantly improves the electrostatic control, and enables the continuous scaling down to the present 14 nm technology node [37].

A further improvement on the MOSFET structure will be silicon nanowires that exploiting a *Gate-All-Around* (GAA) structure, which is illustrated in Fig. 1.5(c) [31–33]. As discussed in [35], gate-all-around structure features a even smaller  $\lambda$  as compared to FinFET. Therefore, the GAA SiNWFETs can provide the ultimate electrostatic control with the MOS structure [38,39].

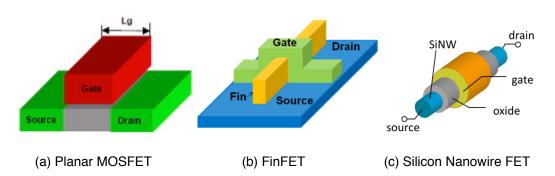

Figure 1.5: Evolution of MOSFET structures from planar MOSFET to FinFET and silicon nanowire FET.

Besides the evolution on MOSFET structures, channel materials with high carrier mobility (e.g., germanium, III-V materials) or intrinsic One-Dimensional (1-D) / Two-Dimensional (2-D) structure (e.g., carbon nanotube, graphene,  $MoS_2$ ) have also been explored to extend the CMOS scaling down [40–44]. Still based on the field effects, they are referred to as "CMOS extension".

#### 1.1.2 Beyond-CMOS Technologies

With all these innovations and efforts in CMOS technology, the transistor size is approaching the natural limitations of materials in the near future [45, 46]. Moreover, the switching energy of silicon FET is also fairly close to a fundamental limit of switching energy of a binary charge-based switch controlled by energy barrier modulation [47]. Therefore, emerging logic devices beyond CMOS technology are expected to continuously address the need of "More Moore". They explore non-charge state variables (e.g., spintronics devices) or novel mechanisms for charge-based devices (e.g., Tunnel FET based on tunneling transport, single electron transistor based on Coulomb blockade) [48–52]. Fig. 1.6 summarizes a classification of emerging logic devices based on the state variables and the switching mechanisms [53].

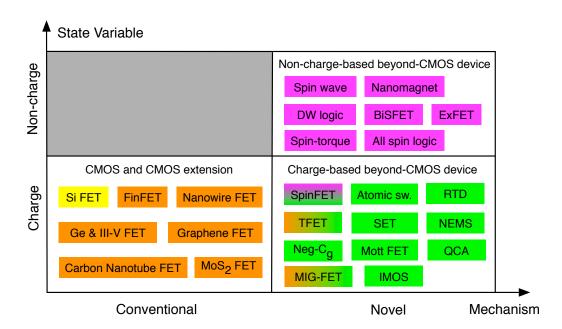

Figure 1.6: A classification of emerging logic devices based on the state variables and the switching mechanisms [53]. The Different colors represent different mechanisms or state variables, and the mixed color reflects the multiplicity of the mechanisms or state variables.

In addition, the circuits are also expected to compute in a more efficient way to keep the trend of "More Moore" when the transistor size approaches the limitations. Therefore, new device concepts are desirable to exploit additional logic functionality. Moreover, with the dramatically increased device density on the chips, reducing the power consumption has become a key concern for circuit applications.

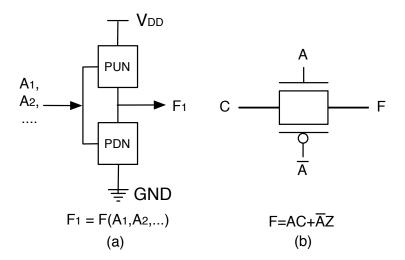

From this perspective, this thesis aims at exploiting the multiple-independent-gate field-effect transistors. The device concept is investigated with silicon nanowire and fin-shaped channels. The devices provide enhanced logic functionality by introducing the electrostatically controlled polarity. The computing efficiency is consequently improved with the proposed devices thanks to the efficient implementation of unate and binate functions. In addition

to the enhanced logic functionality, this thesis further exploits this device concept towards low-power applications. A unique dual-threshold-voltage design with the devices is proposed to achieve a fine trade off between performance and leakage power consumption. Moreover, a steep-subthreshold-slope operation is also demonstrated in the devices, which breaks the limit of subthreshold slope in conventional CMOS technology.

#### 1.2 Current Limitations of CMOS Technology

This section discusses the current limitations of CMOS technology on computing efficiency, as well as the power reduction with multi-threshold-voltage design and supply voltage lowering.

#### 1.2.1 Computing Efficiency

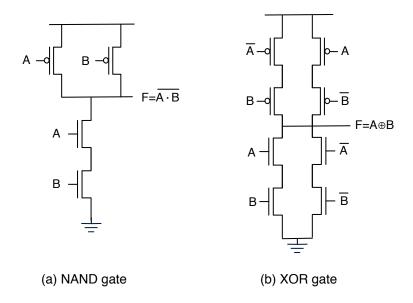

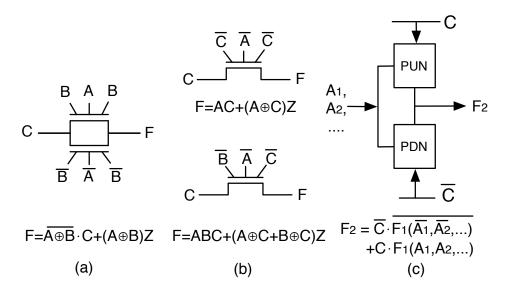

In a majority of real applications, NAND/NOR and exclusive-OR (XOR) intensive functions are the most frequent functions within the circuits [54]. CMOS technology is very efficient in implementing NAND/NOR-based functions. As shown in Fig. 1.7(a), a NAND gate consists of only 4 transistors.

In contrast, to implement the XOR function, CMOS technology has to employ more devices in a complex form as compared to implementing NAND function. Fig. 1.7(b) shows a XOR gate built with 8 transistors excluding the inverters for the input signals.

Figure 1.7: Implementation of logic functions with CMOS technology, (a) NAND gate with 4 transistors, (b) XOR gate with 8 transistors excluding the inverters for the input signals.

XOR-based functions are widely used in various circuits, such as arithmetic circuits, parity checker, comparator, etc.. Thus, a less efficient XOR gate can directly affect the performance of these circuits in terms of speed, power consumption and area [55]. Even though many designs

of XOR function have been proposed, the implementation of XOR intensive functions still limits the computing efficiency of CMOS technology [55, 56].

#### 1.2.2 Multi-Threshold-Voltage Design

With the dramatically-increased device density on the chips, the power consumption has to be considered as a prime constraint in the design of integrated circuits, especially for portable equipments that have a limited battery capacity.

The main source of power consumption in integrated circuits can be divided into dynamic power consumption and static power consumption. Dynamic power is consumed whenever the device is utilized. In contrast, static power is consumed as long as the power supply is maintained [57]. Static power consumption is mainly caused by the leakage current through the device in its *off* state, and is called leakage power consumption. Therefore, transistors with low leakage currents can reduce the leakage power consumption in circuit design.

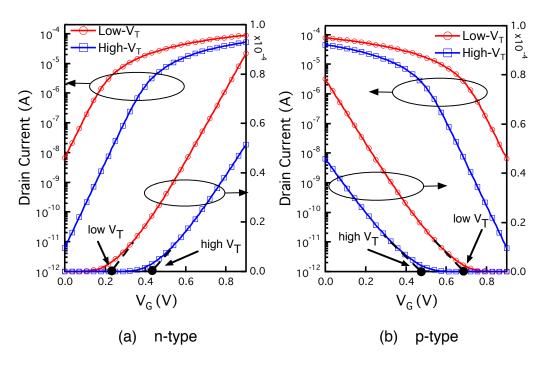

According to the operation of MOSFETs in a certain technology, the subthreshold drain leakage of MOSFETs ( $I_{\rm off}$ ) exponentially decreases with higher *Threshold Voltage* ( $V_T$ ). Hence, the utilization of high- $V_T$  devices can reduce the leakage power. Nevertheless, the devices with higher  $V_T$  provide lower on-state current ( $I_{\rm on}$ ). Fig. 1.8 shows the characteristics of FinFETs with different threshold voltages [58]. It can be observed that the high- $V_T$  devices provide lower  $I_{\rm off}$  by 3 decades but only 50%  $I_{\rm on}$  as compared to low- $V_T$  devices.

Figure 1.8: Characteristics of low- $V_T$  and high- $V_T$  FinFETs extracted from PTM-MG 20 nm model [58]. (a) nFET, (b) pFET.

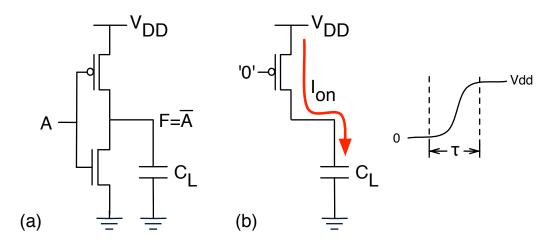

High- $V_T$  devices can efficiently reduce the leakage power consumption with lower  $I_{\rm off}$ . However, the lower  $I_{\rm on}$  of high- $V_T$  devices may harm the circuit performance at the same time. This can be easily understood by considering the operation of a fundamental CMOS logic gate, i.e., an inverter. As shown in Fig. 1.9, the change of the output value can be simply modeled as charging/discharging the load capacitance  $C_L$  through a transistor with the current  $I_{\rm on}$ . Thus, the delay of this operation  $\tau$  can be approximately estimated as:

$$\tau = \frac{C_L V_{DD}}{I_{on}} \tag{1.1}$$

Eq. (1.1) clearly shows the effect of  $I_{on}$  on the circuit performance. Lower  $I_{on}$  of high- $V_T$  devices can significantly degrade the circuit speed.

Figure 1.9: A simple way to estimate the delay of an inverter. (a) An inverter with a load capacitance  $C_L$ , (b) When input is '0', the NMOS is *off*, and the load capacitance is charged by PMOS with the current  $I_{\text{on}}$ . The output rises from 0 to  $V_{DD}$  in a delay of  $\tau$ .

In order to make a trade off between the performance and leakage power consumption, the multi-threshold-voltage (multi- $V_T$ ) design is widely used in CMOS technology [59]. This method mixes devices with different threshold voltages in the design. In general, low- $V_T$  devices with higher  $I_{\rm on}$  are used in the critical paths to meet timing constraints, while high- $V_T$  devices with lower leakage current are used in slack paths to reduce the leakage power consumption.

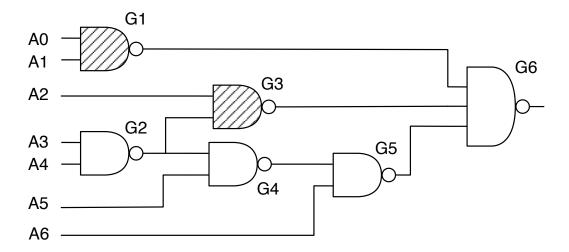

Fig. 1.10 shows an example of the multi- $V_T$  design. By assuming all the input signals (A0~A6) arrive at the same time, the path G2-G4-G5-G6 has the tightest timing constraint, while the paths G1-G6 and G2-G3-G6 are slack paths. Therefore, the gates G2, G4, G5 and G6 can be built with low- $V_T$  devices to improve the speed of the circuit. G1 and G3 can be built with high- $V_T$  devices to reduce the leakage power without degrading the circuit performance.

However, the above analysis and design of Fig. 1.10 are based on an important condition: the circuit still meets the timing constraint when using G1 and G3 built with high- $V_T$  devices. In

Figure 1.10: An example of multi- $V_T$  design. G1 and G3 in slack paths are built with high- $V_T$  devices, while the other gates are in the critical path, thus using low- $V_T$  devices.

other words, the high- $V_T$  devices should provide significant leakage reduction with acceptable performance degradation. Otherwise, G1 and G3 have to be built with low- $V_T$  devices, and the leakage power is not reduced.

As shown in Fig. 1.8, lower  $I_{\rm on}$  in high- $V_T$  devices can significantly degrade the speed of the components. Consequently limited by the discussed condition, the conventional multi- $V_T$  technology can only provide a *coarse* trade off between the circuit performance and the leakage power consumption.

On the other hand, in order to fabricate devices with different threshold voltages, additional process steps are required in conventional multi- $V_T$  design with CMOS technology. This increases the fabrication cost and also reduces the regularity of design.

#### 1.2.3 Supply Voltage Lowering

The total power (dynamic power and static power) consumed by a logic circuit can be approximately estimated as [60]:

$$P_{\text{total}} = P_{\text{static}} + P_{\text{dynamic}} = I_{\text{leak}} V_{DD} + A \cdot C_L V_{DD}^2 f$$

(1.2)

where  $I_{\text{leak}}$  is the leakage current,  $V_{DD}$  is the supply voltage,  $C_L$  is the load capacitance, and f is the operating frequency. The activity factor A models the average switching activity in the circuits.

Eq. (1.2) shows that, lowering the supply voltage  $V_{DD}$  is an efficient way to reduce both the dynamic and static power consumption.

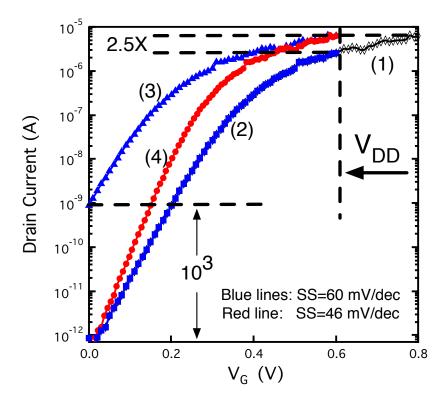

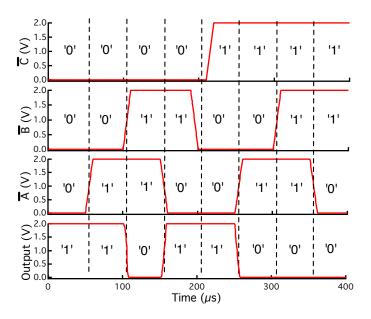

However, as shown in Fig. 1.11, reducing  $V_{DD}$  while keeping the original *Subthreshold Slope* (SS) (Line (1)) leads to a lower  $I_{\rm on}$  (Line (2)) and/or a higher  $I_{\rm off}$  (Line (3)), i.e., a worse  $I_{\rm on}/I_{\rm off}$  ratio. As discussed in Sec. 1.2.2, the degraded  $I_{\rm on}/I_{\rm off}$  ratio will lower the circuit speed or increase the static power consumption. In order to maintain good switching properties at lower supply voltage, the transistor requires a steeper SS (Line (4)).

The subthreshold slope (or subthreshold swing) is commonly defined as the *inverse* of the slope of the  $I_D$ - $V_G$  characteristics in the logarithmic scale at the subthreshold region. It is thus written as:

$$SS = \frac{\partial V_G}{\partial \log_{10} I_D} \tag{1.3}$$

Therefore, a steeper subthreshold slope means a smaller SS.

Figure 1.11: Supply voltage lowering requires devices with a steeper subthreshold slope to maintain good switching properties. (1) Original device characteristics with  $V_{DD} = 0.8 V$ , (2) Characteristics by directly reducing  $V_{DD}$  to 0.6 V, (3) Shifted characteristics with the same  $I_{\rm on}$  and SS as in original device, (4) Characteristics of device with a steeper SS which maintains the  $I_{\rm on}/I_{\rm off}$  ratio as in the original device.

Note that, there is a lower bound of the SS in conventional MOSFETs. According to the working principle, the subthreshold current can be considered as majority carriers at source overcome the barrier in the channel, and finally reach the drain. As shown in Fig. 1.12, the barrier is lowered with the increased gate voltage. Thus, the density of carriers with the energy

above the barrier exponentially increases, leading to the exponentially increased subthreshold current [61]. This relationship can be written as:

$$I_{\text{subthreshold}} \propto \exp\left(\frac{q\phi_s}{kT}\right)$$

(1.4)

where q is the elementary charge, k is the Boltzmann constant, and T is the temperature,  $\phi_s$  is the surface potential in the channel, which determines the barrier for carrier injection. If the gate has an ideal electrostatic control over the channel, the applied gate voltage completely translates into the drop of the barrier, i.e.,  $\partial V_G/\partial \phi_s=1$ .

Figure 1.12: (a) Structure of a n-type MOSFET. (b) Band diagram showing the potential barrier lowered by increasing  $V_G$ .

Therefore, by substituting (1.4) into (1.3), the lower bound of SS is derived as:

$$SS_{\min} = \frac{kT}{q} \cdot \ln 10 \tag{1.5}$$

Eq. (1.5) gives the limit of subthreshold slope in conventional MOSFETs. At room temperature, this limit is nearly 60 mV/dec.

During the past development of MOSFET technology, this limit provided enough room for reducing the supply voltage while keeping the acceptable performance. Numerous innovations

focused on maintaining a good electrostatic control with the gradually shrunk channel to keep the SS close to this limit [13, 15, 36].

However, the pace of reducing the  $V_{DD}$  has to slow down recently. To target ultra-low-power applications with a  $V_{DD}$  far below 1.0 V, new device technologies which are not suffering from this limit are highly desired.

#### 1.3 Global Objectives

This thesis aims at exploiting a new device concept that can overcome these limitations of CMOS technology by introducing multiple independent gate terminals. The device is expected to improve the computing efficiency with enhanced logic functionality and enable a fine-tunned multi-threshold-voltage design without sacrificing the regularity of design. In addition, it is also expected to break the limit of subthreshold slope in CMOS technology.

From this perspective, the concept of multiple-independent-gate FETs is proposed. This device concept is investigated with both silicon nanowire and fin-shaped channels. By efficiently utilizing the unique structure to modulate the Schottky barriers, the device can demonstrate three key properties:

- (1) **Polarity Controllability.** The polarity of the device is controlled by an additional bias, which decides the conduction of different types of carriers. With the polarity controllability, the device can efficiently implement XOR-based functions in addition to NAND/NOR-based functions.

- (2) Multi-Threshold-Voltage Characteristics. By independently modulating the Schottky barriers at contacts and the barrier in the channel, low- $V_T$  and high- $V_T$  configurations are obtained with the same  $I_{\rm on}$  in a single device. The proposed technology can provide a *fine* trade off between performance and leakage power with improved layout regularity. It also brings additional opportunities in design of efficient logic gates.

- (3) Steep-Subthreshold-Slope Operation. By introducing a feedback with dynamic modulation of Schottky barriers, the device can achieve a steep SS below 10 mV/dec over the subthreshold region with high  $I_{\rm on}/I_{\rm off}$  ratio.

This device concept is validated through the characterization of fabricated devices and simulations. Further evaluation at circuit level is carried out, showing the potential of multiple-independent-gate SiNWFETs and FinFETs towards low-power applications.

#### 1.4 Thesis Contributions

This thesis exploits a new device concept: multiple-independent-gate field-effect transistors. The devices are built up with silicon nanowire and fin-shaped channels. The polarity-

controllable device provides new opportunities for circuit design thanks to its enhanced functionality. In the meantime, the proposed technology can improve the low-power design method with the dual-threshold-voltage characteristics and the steep-subthreshold-slope operation.

The proposed device concept is extensively studied on fabrication, dual- $V_T$  characteristics and design, steep-SS operation, and compact modeling. The contributions in each category are introduced as follows:

**Device Structure and Fabrication:** This device concept is originally proposed in this thesis by efficiently utilizing the electrostatic control of Schottky barriers with a multiple-independent-gate structure. A process flow is developed to fabricate the devices with a top-down approach. Multiple-independent-gate SiNWFETs and FinFETs are experimentally demonstrated in the academic cleanroom of EPFL.

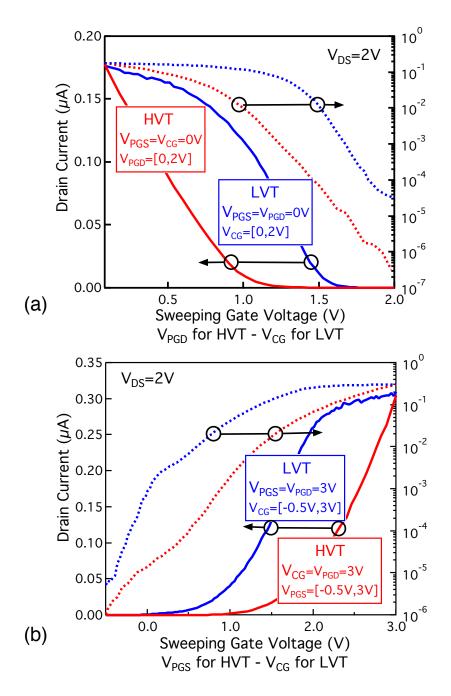

**Dual-Threshold-Voltage Characteristics and Design:** The reconfigurability of threshold voltage in a single device is achieved by independently modulating the Schottky barriers. This property is validated through the characterization of a *Three-Independent-Gate* (TIG) SiN-WFET. The results clearly demonstrate the modulation of threshold voltage and leakage current between low- $V_T$  and high- $V_T$  configurations. Moreover, the device has the same  $I_{\rm on}$  in low- $V_T$  and high- $V_T$  operations. This feature can provide a fine trade off between performance and leakage power consumption in circuit design. This device concept also brings new opportunities in efficiently implementing unate and binate logic functions. In the physical design, an uncommitted logic gate pattern is introduced to improve the layout regularity. Dual- $V_T$  design is thus achieved by applying different wiring schemes on the same pattern.

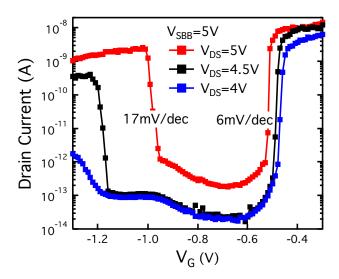

**Steep-Subthreshold-Slope Operation:** The steep-SS operation is achieved by realizing the weak impact ionization induced feedback. In particular, the electrostatic control of the Schottky barriers in the proposed device concept provides not only the polarity controllability, but also a dynamic modulation of the feedback, which can enhance the steep-SS operation. This property is validated by characterizing the fabricated Dual-Independent-Gate (DIG) silicon FinFETs. The measurements show a steep SS of 6 mV/dec over 5 decades of current with high  $I_{\rm on}/I_{\rm off}$  ratio and good reliability. In addition, feasible improvements are proposed to further improve the device performance.

**Compact Modeling:** In order to build the bridge between device technology and circuit design, a physics-based potential and drain current model of DIG SiNWFETs is developed. The presented core model captures the basic operation of the device with a good accuracy as compared to *Technology-Computer-Aided-Design* (TCAD) simulation. Advanced physical effects can be integrated into this core framework to accurately model the behavior of the device.

The presented device concept employs the electrostatic control of Schottky barriers at metalsemiconductor contacts. Therefore, it is not limited in silicon nanowire or fin-shaped channel, but can be extended to SOI or other non-planar structures and other channel materials, such as germanium, etc..

#### 1.5 Thesis Organization

This thesis is organized in five chapters following the introduction. Chapter 2 presents the device structure and fabrication of multiple-independent-gate FETs. Chapter 3 introduces the dual-threshold-voltage characteristics and the design with TIG SiNWFETs. Chapter 4 demonstrates the steep-subthreshold-slope operation with DIG FinFETs. In Chapter 5, a compact model is developed for DIG SiNWFETs. Chapter 6 concludes this thesis and discusses the future work. In detail.

**Chapter 2** first introduces the functionality-enhanced technologies presented in literature. Among different device structures, SiNWFETs and FinFETs with multiple independent gates are chosen by considering their advantages in fabrication and design. Then, the fabrication of multiple-independent-gate SiNWFETs and FinFETs is step-by-step presented following a top-down process flow.

**Chapter 3** presents the device characteristics with dual threshold voltages and the relevant circuit and physical design. Following the review of conventional multi- $V_T$  technologies, the exploitation on the proposed dual- $V_T$  operation is carried out at both device-level and circuit-level.

**Device-Level:** First, the working principle of the dual- $V_T$  operation is introduced. Then, the reconfigurability of both the polarity and  $V_T$  is experimentally validated by characterizing a TIG SiNWFET with vertically-stacked nanowires. Through TCAD simulation, the effect of structural and physical parameters on the dual- $V_T$  characteristics is discussed. A table-based device model is extracted from TCAD simulation, which is applied in the following circuit-level study.

*Circuit-Level:* A circuit and physical design approach with TIG SiNWFETs is studied to exploit their applications in dual- $V_T$  circuits. By applying low- $V_T$  and high- $V_T$  configurations, logic gates are compactly implemented towards either high performance or low leakage applications. In physical design, an uncommitted logic gate pattern is introduced to improve the layout regularity. Combinational and sequential elements are mapped onto the uncommitted pattern with different wiring schemes. Benchmarking of logic gates and circuits shows promising performance in dual- $V_T$  design with TIG SiNWFETs as compared to low-standby-power FinFET technology.

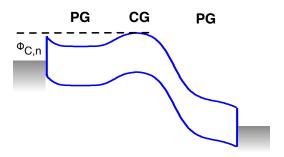

**Chapter 4** first introduces the steep-SS devices presented in literature. Then, it discusses the steep-SS operation in the proposed device. With a feedback induced by weak impact ionization, the device achieves a steep subthreshold slope in addition to the polarity controllability.

#### **Chapter 1. Introduction**

The steep-SS characteristics are studied in terms of experiments and theoretical analysis. In the experimental work, the steep-SS operation is demonstrated through the characterization of DIG FinFETs under different bias and temperature conditions. In the physical analysis, the steep-SS characteristics assisted by the dynamic modulation of Schottky barriers are discussed. Feasible improvements are also suggested to further improve the device performance.

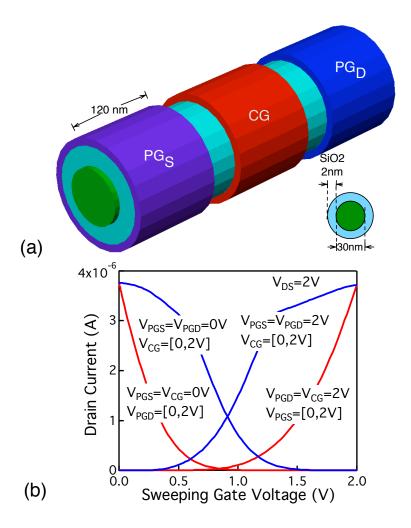

**Chapter 5** focuses on the compact modeling of DIG SiNWFETs, as the DIG SiNWFET is the basic structure in the multiple-independent-gate SiNWFET / FinFET concept. A physics-based surface potential and drain current model is derived. Then, the proposed model is validated by comparing the characteristics predicted by the model with TCAD simulation.

**Chapter 6** concludes the presented results, and summarizes the achievements of this thesis. Finally, a perspective on future work related to and envisaged from this work is discussed.

## 2 Device Structure and Fabrication

This chapter first introduces the general principle behind the functionality-enhanced transistors and the previous work presented in literature. Then, the structures of multiple-independent-gate SiNWFET and FinFET employed in this thesis are illustrated in Sec. 2.2. The fabrication of the proposed devices with a top-down process flow is presented step by step in Sec. 2.3. Finally, this chapter is summarized in Sec. 2.4.

#### 2.1 Functionality-Enhanced Transistors

In this section, we first introduce the operation of Schottky-barrier FETs. Then, the functionality-enhanced transistors presented in literature and that rely on a dynamic control of the Schottky barrier contacts are introduced.

#### 2.1.1 Schottky-Barrier FETs

Conventional MOSFETs use heavily doped semiconductor as *Source and Drain* (S/D) to provide electrons or holes for device operation. The chemical doping at S/D determines the type of the device. For example, the implantation of boron forms *p*-type doped S/D. Thus, the fabricated PMOS are based on the conduction of holes. In contrast, NMOS can be obtained with the implantation of arsenic at S/D to supply electrons.

Instead of using heavily doped semiconductor, metal can also be used as S/D material [62, 63]. The contact between metal S/D and semiconductor channel forms a potential barrier at the interface, i.e., Schottky barrier [10]. The conduction of the device can thus be controlled by electrostatically trimming the Schottky barriers.

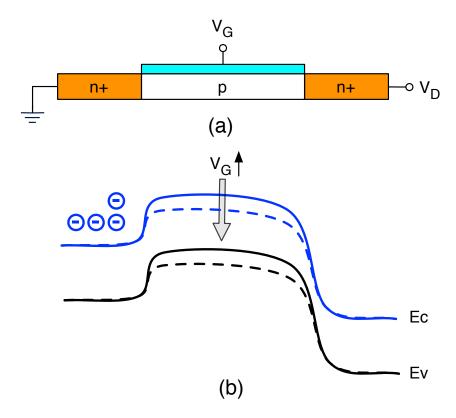

Fig. 2.1(a) illustrates the structure of a *Schottky-Barrier FET* (SB-FET) with a single gate. Since metal can provide both electrons and holes, the SB-FET can achieve the conductions of both carriers. Fig. 2.1(b) illustrates the band diagram for electrically neutral. In Fig. 2.1(c), the energy band in semiconductor is bent downwards by applying positive gate and drain

Figure 2.1: Conduction of both electrons and holes in a SB-FET. (a) Schematic of a single-gate SB-FET. (b) Band diagram for electrically neutral. (c) Conduction of electrons in SB-FET with  $V_G > 0$ . (d) Conduction of holes in SB-FET with  $V_G < 0$ . (e) Cross-section of a 22-nm p-type SB-FET and the measured characteristics [64].

voltages. Thus, electrons can come into the semiconductor channel from metal by means of *Thermionic Emission* (TE), *Thermionic-Field Emission* (TFE) and *Field Emission* (FE) [10,65,66]. In contrast, the upward band bending obtained by applying a negative gate voltage allows the conduction of holes at the Schottky barrier (Fig. 2.1(d)). Therefore, the device exhibits ambipolar characteristics as shown in Fig. 2.1(e) [64]. However, the ambipolar characteristics may degrade the SS and reduce the  $I_{\rm on}/I_{\rm off}$  ratio of the device, thus degrading the circuit performance and increasing the power consumption.

In order to overcome the drawbacks of the ambipolar characteristics and improve the device performance, many techniques are adopted in the development of SB-FETs [67–71]. For example, Fig. 2.2 shows the Schottky-barrier height engineering with dopant segregation technique [67]. The Schottky-barrier height for electrons and holes are tuned by implanting dopant with different dose (Fig. 2.2(a)). The device thus achieves a good  $I_{\rm on}/I_{\rm off}$  ratio, which is comparable with conventional MOSFETs (Fig. 2.2(b)). Nevertheless, the obtained SB-FETs have to abandon the conduction of either electrons or holes in a single device. Therefore, the functionality of the SB-FETs with a fixed polarity are still the same as conventional MOSFETs.

Figure 2.2: (a) Schottky-barrier height engineering with dopant segregation technique, (b) Improved *n*-type performance in SB-FET with dopant segregation, which is comparable to conventional MOSFETs.

## 2.1.2 Functionality-Enhanced Transistors

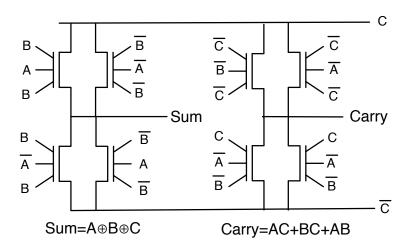

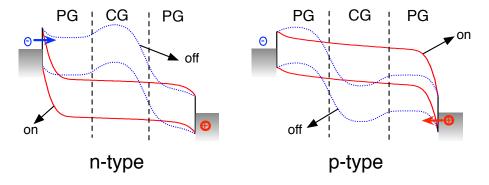

As compared to SB-FETs, functionality-enhanced transistors efficiently utilize the inherent ambipolar conduction at Schottky junctions. Relying on the electrostatic trim of Schottky barriers, the devices select the desired type of carriers with one gate. Moreover, the functionality-enhanced transistors employ an additional gate to modulate the conduction of the carriers. Thanks to the cooperation of both gates, the functionality-enhanced transistors can achieve independent control of the polarity and the conduction of the devices, and exhibit both n-type and p-type characteristics in a single device.

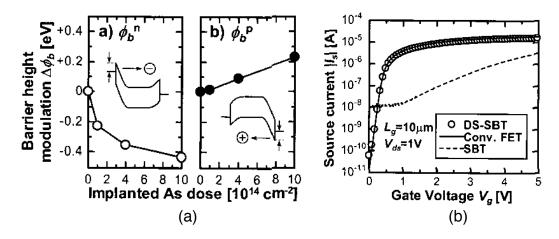

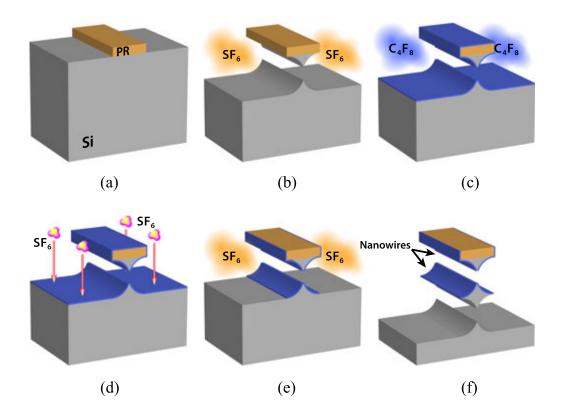

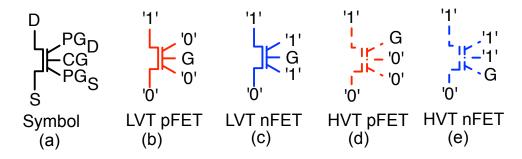

Starting from this principle, functionality-enhanced transistors have been demonstrated with different structures and channel materials. [72–81]. Fig. 2.3 shows some of them.

Heinzig *et al.* fabricate a functionality-enhanced transistor with silicon nanowire as the channel (Fig. 2.3(a)) [73]. Two top gates separately modulate the Schottky barriers at source and drain. During the operation, one gate blocks the unwanted type of carriers, thus determining the polarity of the device. The other gate modulates the tunneling of selected carriers through the corresponding Schottky barrier, thus controlling the channel conduction.

Figure 2.3: Polarity-controllable transistors built with different device structures and materials: (a) single silicon nanowire with two top gates [73], (b)  $MoS_2$  channel with two buried gates [74], (c) vertically-stacked silicon nanowires with double gate-all-around gates [72], (d) graphene with a top gate and a back gate [78], (e) carbon nanotube with a top gate and a back gate [79], (f)  $\alpha$ -MoTe<sub>2</sub> with a top gate and a back gate [80].

Sutar  $\it et al.$  use MoS<sub>2</sub> as the channel material as shown in Fig. 2.3(b) [74] . The device also has two independent gates and consequently similar operation as in Fig. 2.3(a), but the gates are buried in the oxide.

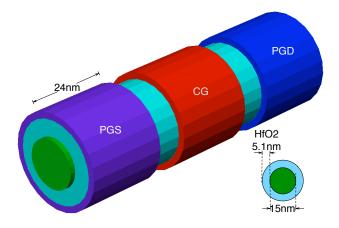

De Marchi *et al.* present a functionality-enhanced device based on vertically-stacked silicon nanowires (Fig. 2.3(c)) [72]. The channel is controlled by three gate-all-around structures. Two gate structures close to source and drain are connected to modulate the Schottky barriers. Therefore, this gate selects the desired carrier type, and is called *Polarity Gate* (PG). The *Control Gate* (CG) modulates a potential barrier in the middle of the channel, which consequently controls the channel conduction.

In Fig. 2.3(d), (e) and (f), the devices feature a top gate controlling the channel conduction, and a back gate modulating the Schottky barriers. The operation of these three devices are similar to the device in Fig. 2.3(c). However, these devices are built with different channel materials. Lin *et al.* use carbon nanotube as the channel materials, while 2-D materials graphene and  $\alpha$ -MoTe<sub>2</sub> are applied in the work of Harada *et al.* and Nakaharai *et al.* [78–82].

The similarities and the differences between these devices are further discussed as follows:

#### • Similarities:

- 1. They all employ metallic S/D contacts with semiconductor channel. Therefore, the operation of the devices is based on the carrier transport at the Schottky barriers.

- 2. The devices all use two separate gates to independently control the polarity of the device and the channel conduction.

#### • Differences:

#### 1. Material:

Different semiconductor materials are applied to these devices as the channel. Fig. 2.3(a) and (c) both use silicon nanowires. In (a), the channel is made by a single nanowire, while (c) consists of vertically-stacked nanowires; (e) is based on carbon nanotube; (b), (d) and (f) exploit 2-D materials, including  $MoS_2$ , graphene, and  $\alpha$ - $MoTe_2$ .

## 2. Number of gated regions:

Each channel of the devices can be divided into several gated regions from source to drain. Although these devices all have two gates for independent control, the number of gated regions in each device can be different.

For example, Fig. 2.3(a) and (b) have two gated regions. Each gate controls a Schottky barrier. While (c), (d), (e), (f) all have three gated regions. The two gated regions close to S/D are controlled by a common gate, which modulates both Schottky barriers. The other gate at the middle of the channel controls the conduction of the carriers in the channel.

#### 3. Placement of Gates:

These devices place the gates in different ways. In Fig. 2.3(a), two top gates are placed on the nanowires, while (b) buries the two gates underneath the  $MoS_2$  channel. In (c), the two gates are both made with gate-all-around structures. (d), (e) and (f) all build the devices with a top gate and a back gate connected from the substrate.

From the perspective of fabrication, the functionality-enhanced transistors exploit a dopant-free process by replacing heavily doped S/D in CMOS technology with metal. The use of metallic S/D helps to fabricate ultra-shallow S/D junctions with a low resistance [83]. In

addition, the dopant-free process may eliminate the ion implantation and reduce the variation due to random dopant fluctuation in nano-scale devices [84, 85].

More importantly, the polarity controllability can be utilized to implement new logic architectures in a compact form [86–89]. In particular, the polarity-controllable FETs can efficiently implement both NAND-based and XOR-based functions with the enhanced logic functionalities [54, 86, 90]. Therefore, the application of polarity-controllable FETs can promote the design of more efficient logic circuits, which will be discussed in details in Chapter 3.

# 2.2 Structure of Multiple-Independent-Gate FETs

Functionality-enhanced transistors introduced before are fabricated with different channel materials and gate structures. In this thesis, we consider that:

- 1. Compared to new materials such as carbon nanotube or  $MoS_2$ , silicon is preferred as the channel material in this study because of the mature technology for device fabrication and large-scale integration. The mature technology can enhance the yield of high-quality devices and circuits during the complex fabrication steps, including etching, oxidation, and Schottky-barrier formation, etc..

- 2. Compared to the bulk structure, the use of the silicon nanowire or fin-shaped channel is best suited for excellent electrostatic control, which is considered as a primary requirement for deeply scaled devices, especially when the channel length shrinks to below 20 nm [36, 38, 39].

- 3. When employing the device structure with a top gate and a back gate, it is difficult to independently control each device on the substrate. In contrast, the structure with independent top gates provides independent control of each device from the top, thus enabling the circuit-level fabrication with the proposed devices.

- 4. Moreover, the multiple-gate structure can enhance the degree of freedom and range of functionalities in one transistor by independently controlling each Schottky barrier and the conduction of the channel.

Finally, this thesis proposes the multiple-independent-gate field-effect transistors through the investigation of different materials and structures. Silicon nanowire and fin-shaped channel are applied to this device concept based on the above considerations.

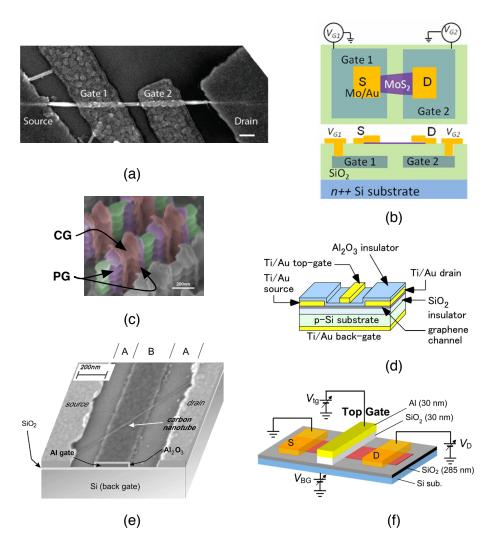

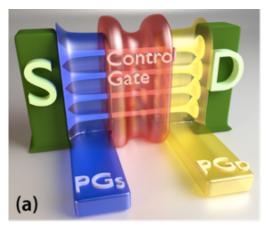

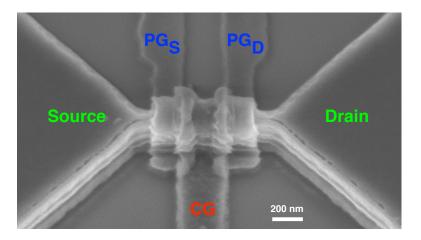

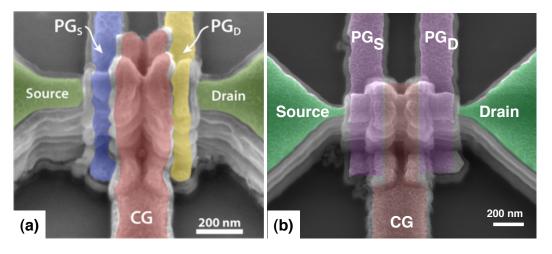

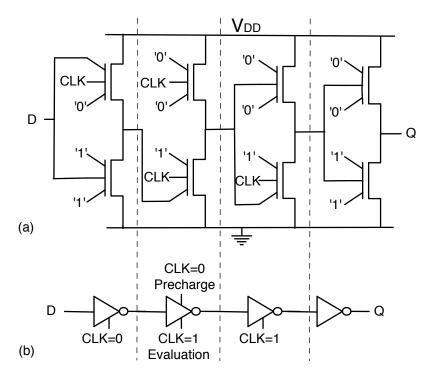

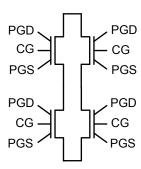

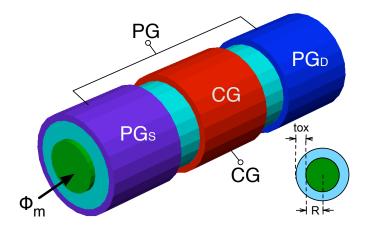

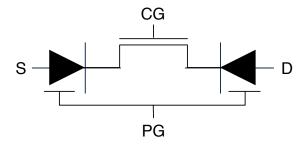

The conceptual sketches of two representatives of the multiple-independent-gate SiNWFET and FinFET are shown in Fig. 2.4. In Fig. 2.4(a), vertically-stacked silicon nanowires are confined within the source and drain pillars. The channels are surrounded by three independent gates, named *Polarity Gate at Source* (PG<sub>S</sub>), *Control Gate* (CG) and *Polarity Gate at Drain* (PG<sub>D</sub>). Nickel silicide is used as S/D material to form Schottky junctions with the silicon channel.

Figure 2.4: Structure of (a) three-independent-gate SiNWFET and (b) dual-independent-gate silicon FinFET.

Therefore,  $PG_S$  and  $PG_D$  in the structures modulate the Schottky barriers at the source and drain contacts, while CG controls the current flow through the channel.

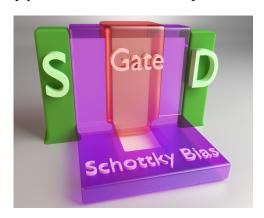

Fig. 2.4(b) shows a dual-independent-gate silicon FinFET. As compared to the device in Fig. 2.4(a),  $PG_S$  and  $PG_D$  in this device are connected together to bias the Schottky barriers. Therefore, the connected polarity-gates are renamed as *Schottky Barrier Bias* (SBB), and the control gate is simply called *Gate* (G). Note that, the dual-independent-gate structure is a simplified multiple-independent-gate structure, which can be directly obtained by connecting  $PG_S$  and  $PG_D$  in the layout design.

The three-independent-gate SiNWFET in Fig. 2.4(a) will be used to discuss the dual-threshold-voltage characteristics and design in Chapter 3, and the dual-independent-gate FinFET in Fig. 2.4(b) will be used to demonstrate the steep-subthreshold-slope operation in Chapter 4.

## 2.3 Device Fabrication

In order to experimentally demonstrate the multiple-independent-gate SiNWFETs and Fin-FETs, a process flow is developed and completely implemented at the facilities in the Center of MicroNanoTechnlogy (CMi) of EPFL. In this section, we show the process flow and runcard of the fabrication of three-independent-gate SiNWFETs and FinFET. Devices with dual independent gates can be fabricated with the same process by connecting the two polarity gates in the layout design.

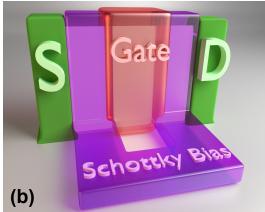

First, a lightly *p*-type boron doped ( $\sim 10^{15}/cm^3$ ) SOI 100 mm wafer with a 340 nm thick silicon device layer is used as the substrate. The thickness of the *Buried Oxide* (BOX) is  $2\mu m$ . The crystal orientation of the SOI layer is (100), and the resistivity of the SOI layer is between  $8.5\Omega \cdot cm$  to  $11.5\Omega \cdot cm$ .

The desired critical feature size of the devices is around 50 nm, which is the diameter of nanowires and thickness of fins. In order to write such small patterns, the Vistec EBPG5000 electron-beam lithography system is used, which is capable of writing <10 nm features and placing structures on a substrate with an accuracy of less than 20 nm [91].

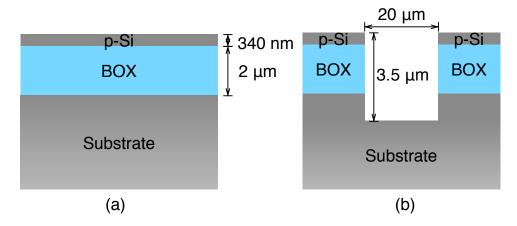

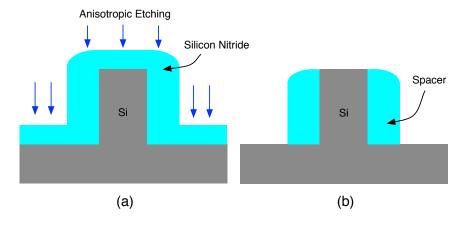

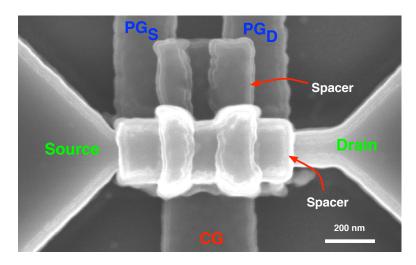

The fabrication of the devices is implemented with a CMOS-compatible top-down approach, which is suitable for circuit fabrication and large-scale integration. The process consists of six main steps, i.e., the fabrication of (1) alignment markers, (2) channel, (3) polarity gates, (4) control gate, (5) nitride spacers, and finally (6) nickel silicide. The detailed process flow is introduced below.