# Program Compilation for Large-Scale Quantum Computers

Thèse n. 8756 présentée le 14 décembre 2020 à la Faculté des sciences et techniques de l'ingénieur programme doctoral en Génie électrique École polytechnique fédérale de Lausanne

pour l'obtention du grade de Docteur ès Sciences par

acceptée sur proposition du jury :

Prof. Andreas Peter Burg, président du jury Prof. Giovanni De Micheli, directeur de thèse Dr. Mathias Soeken, co-directeur de thèse

Prof. Paolo lenne, rapporteur Prof. Michele Mosca, rapporteur Dr. Nikolaj Bjørner, rapporteur

Lausanne, EPFL, 2020

## Acknowledgements

First of all, I would like to express my gratitude to my thesis director, Prof. Giovanni De Micheli, for believing in me from the very first moment and for the continuous guidance and support. I would also like to thank my co-director Dr. Mathias Soeken, for guiding me during these years and for passing on the love for scientific research. I am thankful for all the fun moments we had during our many, sometimes little crazy trips.

My gratitude goes to the referees of my thesis, Prof. Michele Mosca, Dr. Nikolaj Bjørner, and Prof. Paolo Ienne, for their time and their precious feedback. I hope to have the opportunity to further discuss our research.

I am grateful to Dr. Martin Roetteler and Dr. Thomas Häner for the opportunity of working on such exciting summer internship projects.

I would like to thank all my special colleagues, that created the right environment for an amazing experience. Thank you, Ivan, for always making me smile and for being there for me in all kinds of situations. I am glad to have a friend like you.

Thanks, Eleonora, for our friendship, which now has deep roots in all the things we have in common and all the experiences we have had together.

Thanks to the best botanist and green thumb office mate, Simone. Thank you for the company, for your availability and the delicious presents from your hometown. It has been a pleasure sharing the office with you.

Thanks to Francesca C., for all the long talks and the fun activities. Your energy is contagious, thanks for sharing some with me.

Thank you, Giovanni, for all the excellent dishes you have cooked. You have dampened the feeling of homesickness with your excellent cooking skills. Thank you for all the amazing trips and events that you organized.

Thanks to Francesca S., Enrico T., and to the little Leo, for the sweetness and hospitality. Your family has always been a pillar of our community in times of need but also in times of celebration.

Although part of LSI only for a short time, I would like to thank Sofia N., Sara, Kate, Nadya, Lucia, Sofia M., Samuel and Abduwali for making the PhD experience a lot more fun.

Thank you Bruno for the discussions and collaborations on quantum computing and for all the fun moments we had together outside of the lab.

A special thank goes to all my present and past logic synthesis colleagues for the fruitful discussions: Heinz, Zhufei, Winston, Sonia, and Ferehste.

For always assisting me with bureaucratic problems (and non-), I would like to thank Cristina,

#### Acknowledgements

Carol, and Chantal.

I am grateful to all the people that I have met during this amazing journey. First of all, I am grateful to Chiara for being among my closest friends. You have been an amazing flatmate, you are generous beyond imagination, and you always manage to cheer me up. Also, I would like to thank Giacomo, Jacopo, Nicoló, Carlotta, Matteo, Luca, Nadia, Mariazel, and Emanuele, for being my family far from home.

I would also like to thank my fellow summer interns, even if we have spent a little time together, you made me feel at home. A special thanks to Fernando, Harsh, Jessica L., Jessica S., and Ilaria. I hope that our paths will bring us together once more.

I am thankful to the people that supported me from my hometown: my friends, and my dear family. Lorenzo, I could not be luckier than having you as my long-time friend. Thank you for giving me strength and for inspiring me to become a better version of myself. Chiara, thank you for always cheering for me and my success. Thanks for your unique and true friendship. Alessandro, thank you for loving me, for your patience, for being by my side every day even when apart, for making me happy, and for taking care of me.

Finally, I would like to thank my family. You have supported me with love, attention, and dedication in my path of personal and professional growth. I have always felt close to you over the years and all my achievements, are also your achievements.

Lausanne, December 14, 2020

### **Abstract**

Practical realizations of quantum computers are poised to deliver outstanding computational capabilities far beyond the reach of any classical supercomputer. While classical systems are reliably implemented using CMOS technology, the fabrication of quantum hardware has not yet reached a commercially viable level of maturity. Nowadays, many different technologies are being developed as competing candidates to build the first error-corrected quantum computer. Among the software resources required to operate such a system, quantum compilers translate a high-level description of a quantum algorithm into low-level, technology-dependent quantum instructions.

Many quantum algorithms, including Shor's and Grover's algorithms, require to compute some classical logic functions on the quantum computer. The first part of this thesis deals with the problem of compiling quantum circuits that perform such classical Boolean functions, called *oracles*, into a fault-tolerant set of instructions. Oracle circuits often demand many resources in terms of the number of qubits and gates. The focus is on compiling quantum circuits starting from multi-level logic networks representing large Boolean functions while minimizing the resource footprint of the obtained quantum circuits. At the same time, the trade-off between memory resources and the number of operations typical of such a compilation process is explored. As part of the effort in reducing the resources required to perform a given quantum program, I also present some quantum circuit optimization techniques.

The researched algorithms leverage data structures and techniques borrowed and adapted from classical logic synthesis, e.g., SAT solvers, LUT mapping, and multi-level logic networks. I implemented all the compilation algorithms presented in this thesis as part of open-source projects. In particular, I develop and maintain *caterpillar*—a C++ header-only library dedicated to the quantum compilation of oracles and quantum memory management.

The second part of this thesis describes how to equip quantum programming language compilers with automatic accuracy management. Despite the availability of many of such languages, resource estimation of quantum algorithms does not yet support taking approximation errors into account. This general methodology is applicable to any programming language and I demonstrate its integration into the Q# compiler. The technique consists of providing language support to ease the accuracy-aware programming task. The user can define accuracy parameters that will be automatically optimized according to a constraint and a cost function directly generated from the source code. In the presented practical evaluations, the constraint function is the overall allowed accuracy, while the cost function is application-dependent and related to the number of operations. During the optimization process, such functions are eval-

#### **Abstract**

uated hundreds of times. For this reason, they are extracted as (near-)symbolic expressions, whose evaluation time does not depend on the quantum algorithm size.

The algorithms and the methodologies presented in this thesis are part of a widespread effort of the research community to build a complete and efficient software stack to program and control the first practical universal quantum computer.

**Keywords:** logic synthesis, quantum computing, quantum compilation, quantum programming, resource estimation

#### **Estratto**

I futuri computer quantistici promettono capacità di calcolo eccezionali, ben al di là della portata di qualsiasi supercomputer classico. Mentre i sistemi classici possono essere implementati in modo affidabile utilizzando la tecnologia CMOS, la fabbricazione di hardware quantistico non ha ancora raggiunto un livello di maturità commercialmente sostenibile. Al giorno d'oggi, diverse tecnologie sono in fase di sviluppo e sono in competizione tra loro per costruire il primo computer quantistico con correzione degli errori. Tra le risorse software necessarie per far funzionare un tale sistema, i compilatori quantistici traducono una descrizione ad alto livello di un algoritmo quantistico in istruzioni quantistiche a basso livello, dipendenti dalla tecnologia.

Molti algoritmi quantistici, compresi gli algoritmi di Shor e Grover, richiedono che il computer quantistico calcoli alcune funzioni logiche. La prima parte di questa tesi affronta il problema della compilazione di circuiti quantistici che eseguono tali classiche funzioni Booleane, denominati *oracle*, in un insieme di istruzioni supportato dai codici di correzione degli errori. I circuiti *oracle* spesso richiedono molte risorse in termini di numero di qubit e di operazioni. Per questo, la mia ricerca si focalizza su minimizzare tali risorse attraverso un'efficiente compilazione di circuiti quantistici a partire da reti logiche multilivello. Allo stesso tempo, la tesi esplora il *trade-off* tra la memoria e il numero di operazioni, tipico di un tale processo di compilazione. Nel quadro dello sforzo volto a ridurre le risorse necessarie per eseguire un dato programma quantistico, presento inoltre alcune tecniche di ottimizzazione dei circuiti quantistici.

Gli algoritmi oggetto di questa ricerca sfruttano strutture di dati e tecniche prese in prestito e adattate dalla sintesi logica, ad esempio: SAT *solvers*, LUT *mapping* e reti logiche multilivello. Ho implementato tutti gli algoritmi presentati in questa tesi come parte di progetti *open-source*. In particolare, sviluppo e mantengo una libreria C++ dedicata alla compilazione quantistica degli *oracle* e alla gestione della memoria quantistica.

La seconda parte di questa tesi descrive come dotare i compilatori dei linguaggi di programmazione quantistica di una gestione automatica della loro accuratezza. Nonostante la disponibilità di molti di questi linguaggi, la stima delle risorse degli algoritmi quantistici non prende ancora in considerazione gli errori di approssimazione. Questa metodologia è generalmente applicabile a qualsiasi linguaggio di programmazione e ne dimostro l'integrazione nel compilatore del linguaggio Q#. La tecnica consiste nel fornire, attraverso il linguaggio, un supporto per facilitare il compito di tenere in considerazione l'accuratezza. L'utente può definire parametri di accuratezza che saranno automaticamente ottimizzati secondo una

#### **Estratto**

funzione di vincolo e una funzione di costo generati direttamente dal codice sorgente. Nelle valutazioni pratiche presentate, la funzione di vincolo è l'errore complessivo consentito, mentre la funzione di costo dipende dall'applicazione e si riferisce al numero di operazioni. Durante il processo di ottimizzazione, tali funzioni vengono valutate centinaia di volte. Per questo motivo, vengono estratte come espressioni (quasi) simboliche, il cui tempo di valutazione non dipende dalla dimensione dell'algoritmo quantistico.

Gli algoritmi e le metodologie presentate in questa tesi fanno parte di uno sforzo diffuso della comunità scientifica per costruire uno *stack* software completo ed efficiente per programmare e controllare il primo computer quantistico universale.

**Parole chiave:** sintesi logica, calcolo quantistico, compilazione quantistica, programmazione quantistica, stima delle risorse

## **Contents**

| Ac | knov  | ledgements                                | j    |

|----|-------|-------------------------------------------|------|

| Al | ostra | (English/Italian)                         | iii  |

| Li | st of | igures                                    | X    |

| Li | st of | ables                                     | xiii |

| Li | st of | cronyms                                   | XV   |

| 1  | Intr  | duction                                   | 1    |

|    | 1.1   | History of quantum computing              | 1    |

|    |       | 1.1.1 The rise of quantum mechanics       | 1    |

|    |       | 1.1.2 Computing with quantum physics      | 2    |

|    | 1.2   | Quantum computing systems                 | 4    |

|    |       | 1.2.1 Trapped ions                        | 5    |

|    |       | 1.2.2 Superconducting circuits            | 6    |

|    |       | 1.2.3 Nitrogen vacancies and quantum dots | 7    |

|    |       | 1.2.4 Anyonic particles                   | 7    |

|    | 1.3   | Software requirements                     | 7    |

|    |       | 1.3.1 Model of computation                | 7    |

|    |       | 1.3.2 Control software                    | 9    |

|    |       | 1.3.3 Debugging and testing               | g    |

|    | 1.4   | Quantum compilers                         | 10   |

|    | 1.5   | Thesis contribution                       | 11   |

|    |       | 1.5.1 Compilation of combinational logic  | 11   |

|    |       | 1.5.2 Accuracy management                 | 14   |

|    | 1.6   | Thesis organization                       | 15   |

| I  | Bac   | ground                                    | 19   |

| 2  | Log   | synthesis                                 | 21   |

|    | 2.1   | Logic representations                     | 21   |

|    |       | 2.1.1 Boolean functions                   | 21   |

#### **Contents**

|    | 2.2<br>2.3<br>2.4<br>2.5 | 2.1.2 Truth tables          2.1.3 ESOP representation of Boolean function          2.1.4 Multi-level logic networks          Classification of Boolean functions          Look-Up Table (LUT) mapping          Boolean satisfiability (SAT) problem          Summary | 22<br>23<br>24<br>27<br>28<br>29 |

|----|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 3  | O112                     | intum computing                                                                                                                                                                                                                                                      | 31                               |

| J  |                          | Quantum computing principles                                                                                                                                                                                                                                         | 31                               |

|    | 5.1                      | 3.1.1 Qubits                                                                                                                                                                                                                                                         | 31                               |

|    |                          | 3.1.2 Gates                                                                                                                                                                                                                                                          | 32                               |

|    |                          | 3.1.3 Universal quantum libraries                                                                                                                                                                                                                                    | 32                               |

|    |                          | 3.1.4 Measurements                                                                                                                                                                                                                                                   | 34                               |

|    |                          | 3.1.5 Quantum circuits                                                                                                                                                                                                                                               | 34                               |

|    | 3.2                      | Phase polynomial representation                                                                                                                                                                                                                                      | 35                               |

|    | 3.3                      | Summary                                                                                                                                                                                                                                                              | 36                               |

|    |                          |                                                                                                                                                                                                                                                                      |                                  |

| 4  | Rev                      | ersible circuits                                                                                                                                                                                                                                                     | 39                               |

|    | 4.1                      | Reversible gates                                                                                                                                                                                                                                                     | 39                               |

|    | 4.2                      | Synthesis of reversible circuits                                                                                                                                                                                                                                     | 40                               |

|    |                          | 4.2.1 ESOP-based reversible logic synthesis                                                                                                                                                                                                                          | 41                               |

|    |                          | 4.2.2 Hierarchical reversible synthesis                                                                                                                                                                                                                              | 41                               |

|    | 4.3                      | Decomposing reversible gates into quantum circuits                                                                                                                                                                                                                   | 42                               |

|    |                          | 4.3.1 Gray synthesis                                                                                                                                                                                                                                                 | 42                               |

|    |                          | 4.3.2 Quantum circuits for the Toffoli gate                                                                                                                                                                                                                          | 42                               |

|    | 4.4                      | Summary                                                                                                                                                                                                                                                              | 44                               |

| II |                          | antum circuit synthesis and optimization                                                                                                                                                                                                                             | 45                               |

| 5  |                          | rarchical reversible synthesis                                                                                                                                                                                                                                       | 47                               |

|    | 5.1                      | Method overview                                                                                                                                                                                                                                                      | 47                               |

|    | 5.2                      | Quantum-aware k-LUT mapping                                                                                                                                                                                                                                          | 50                               |

|    |                          | 5.2.1 Cut enumeration and costing                                                                                                                                                                                                                                    | 50                               |

|    |                          | 5.2.2 XOR-block matching                                                                                                                                                                                                                                             | 51                               |

|    | 5.3                      | Quantum memory management                                                                                                                                                                                                                                            | 52                               |

|    |                          | 5.3.1 Reversible pebbling game                                                                                                                                                                                                                                       | 54                               |

|    |                          | 5.3.2 SAT-encoding                                                                                                                                                                                                                                                   | 55                               |

|    |                          | 5.3.3 Show-cases                                                                                                                                                                                                                                                     | 57                               |

|    | 5.4                      | Results                                                                                                                                                                                                                                                              | 59                               |

|    | 5.5                      | Summary                                                                                                                                                                                                                                                              | 62                               |

| 6  | Con                      | aniling var-and-inverter granhs                                                                                                                                                                                                                                      | 63                               |

|    | 6.1  | Methods overview                                                     | 63  |

|----|------|----------------------------------------------------------------------|-----|

|    | 6.2  | Xor-and-inverter graphs                                              | 65  |

|    | 6.3  | Methods                                                              | 67  |

|    |      | 6.3.1 Algorithm 1: minimizing the T-count                            | 67  |

|    |      | 6.3.2 Algorithm 2: minimizing the T-depth                            | 69  |

|    |      | 6.3.3 Algorithm 3: minimizing the number of qubits                   | 70  |

|    | 6.4  | Results                                                              | 72  |

|    |      | 6.4.1 Improving the T-count versus T-depth                           | 73  |

|    |      | 6.4.2 Qubits/T-count trade-off                                       | 73  |

|    |      | 6.4.3 Discussion                                                     | 74  |

|    | 6.5  | Summary                                                              | 77  |

| 7  | Sing | gle-target gate decomposition                                        | 79  |

|    | 7.1  | Precomputed quantum circuits                                         | 79  |

|    |      | 7.1.1 Spectral equivalence in quantum compilation                    | 80  |

|    |      | 7.1.2 Algorithms for the synthesis of the database                   | 82  |

|    |      | 7.1.3 Database of optimized quantum circuits                         | 84  |

|    | 7.2  | ESOP-based decomposition                                             | 86  |

|    |      | 7.2.1 Optimal ESOP for quantum compilation                           | 86  |

|    |      | 7.2.2 Constraint-based ESOP synthesis                                | 87  |

|    |      | 7.2.3 Results                                                        | 91  |

|    | 7.3  | LUT-based decomposition                                              | 96  |

|    | 7.4  | Experimental results                                                 | 98  |

|    | 7.5  | Summary                                                              | 98  |

| 8  | Qua  | antum circuit optimization                                           | 101 |

|    | 8.1  | T-count optimization using graph matching                            | 101 |

|    |      | 8.1.1 Optimization properties                                        | 101 |

|    |      | 8.1.2 Graph matching problem                                         | 103 |

|    | 8.2  | SAT based (CNOT, $T$ ) optimization                                  | 104 |

|    |      | 8.2.1 Linear reversible functions                                    | 104 |

|    |      | 8.2.2 SAT-based algorithm for the synthesis of {CNOT, $T$ } circuits | 105 |

|    |      | 8.2.3 SAT-based rewriting algorithm                                  | 109 |

|    |      | 8.2.4 Results                                                        | 109 |

|    | 8.3  | Summary                                                              | 110 |

| II | I C  | ompiler-integrated accuracy management                               | 113 |

|    |      |                                                                      |     |

| 9  | 9.1  | omatic accuracy management  Errors in quantum compilation            | 115 |

|    | 9.1  | 9.1.1 Synthesis errors                                               |     |

|    |      | 9.1.2 Phase estimation errors                                        |     |

|    |      | 9.1.2 Phase estimation errors                                        |     |

|    |      | 9.1.0 / MEVILLIHU VIIVIO                                             | /   |

#### **Contents**

|          | 9.2                                  | Approximation errors in quantum circuits                                                                                       | 118                                                         |  |  |

|----------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--|--|

|          | 9.3                                  | Sample quantum programs                                                                                                        |                                                             |  |  |

|          |                                      | 9.3.1 Quantum Fourier transform                                                                                                | 120                                                         |  |  |

|          |                                      | 9.3.2 Simulating time-evolution of operators                                                                                   | 121                                                         |  |  |

|          |                                      | 9.3.3 Quantum phase estimation                                                                                                 | 122                                                         |  |  |

|          | 9.4                                  | Adding language support for accuracy management                                                                                | 123                                                         |  |  |

|          | 9.5                                  | Automating accuracy management                                                                                                 | 125                                                         |  |  |

|          |                                      | 9.5.1 Cost/constraint functions: extraction                                                                                    | 126                                                         |  |  |

|          |                                      | 9.5.2 Cost/constraint functions: optimization                                                                                  | 127                                                         |  |  |

|          | 9.6                                  | Compiler and language requirements                                                                                             | 129                                                         |  |  |

|          |                                      | 9.6.1 LLVM prototype                                                                                                           | 130                                                         |  |  |

|          |                                      | 9.6.2 Q# integration                                                                                                           | 133                                                         |  |  |

|          | 9.7                                  | Qualitative evaluation                                                                                                         | 135                                                         |  |  |

|          | 9.8                                  | Quantitative evaluation                                                                                                        |                                                             |  |  |

|          | 9.9                                  | Summary                                                                                                                        | 138                                                         |  |  |

| IV       | Oı                                   | pen-source development                                                                                                         | 141                                                         |  |  |

|          | o I                                  | 1                                                                                                                              |                                                             |  |  |

|          | -                                    | erpillar                                                                                                                       | 143                                                         |  |  |

|          | Cate                                 | •                                                                                                                              | 143                                                         |  |  |

|          | Cate                                 | erpillar                                                                                                                       | <b>143</b> 144                                              |  |  |

|          | Cate                                 | erpillar  Compiling with caterpillar                                                                                           | 143<br>144<br>145<br>147                                    |  |  |

|          | 10.1                                 | erpillar Compiling with caterpillar  10.1.1 Mapping strategies  10.1.2 Pebbling strategies  10.1.3 Mapping strategies for XAGs | 143<br>144<br>145<br>147<br>148                             |  |  |

|          | 10.1                                 | erpillar  Compiling with caterpillar                                                                                           | 143<br>144<br>145<br>147<br>148                             |  |  |

|          | 10.1<br>10.2<br>10.3                 | erpillar  Compiling with caterpillar                                                                                           | 143<br>144<br>145<br>147<br>148<br>148<br>149               |  |  |

|          | 10.1<br>10.2<br>10.3<br>10.4         | erpillar  Compiling with caterpillar                                                                                           | 143<br>144<br>145<br>147<br>148<br>148<br>149<br>150        |  |  |

|          | 10.1<br>10.2<br>10.3<br>10.4         | erpillar  Compiling with caterpillar                                                                                           | 143<br>144<br>145<br>147<br>148<br>148<br>149<br>150        |  |  |

|          | 10.1<br>10.2<br>10.3<br>10.4         | erpillar  Compiling with caterpillar                                                                                           | 143<br>144<br>145<br>147<br>148<br>148<br>149<br>150        |  |  |

| 10       | 10.1<br>10.2<br>10.3<br>10.4<br>10.5 | erpillar  Compiling with caterpillar                                                                                           | 143<br>144<br>145<br>147<br>148<br>148<br>149<br>150        |  |  |

| 10       | 10.1<br>10.2<br>10.3<br>10.4<br>10.5 | erpillar  Compiling with caterpillar                                                                                           | 143<br>144<br>145<br>147<br>148<br>148<br>149<br>150<br>151 |  |  |

| 110<br>A | 10.2<br>10.3<br>10.4<br>10.5<br>Con  | compiling with caterpillar                                                                                                     | 143<br>144<br>145<br>147<br>148<br>149<br>150<br>151        |  |  |

## **List of Figures**

| 1.1                               | volume>                                                                                                                                                                              | ım<br>4 |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 1.2                               | Sequence diagram illustrating how the QPU interacts with a host CPU, image                                                                                                           |         |

|                                   | from [1]                                                                                                                                                                             | 8       |

| 1.3                               | Different stages of the offline software stack. Image from [2]                                                                                                                       | 10      |

| 2.1                               | Electronic Design Automation (EDA) flow.                                                                                                                                             | 22      |

| <ul><li>2.2</li><li>2.3</li></ul> | An XAG for the majority of 3-inputs                                                                                                                                                  | 24      |

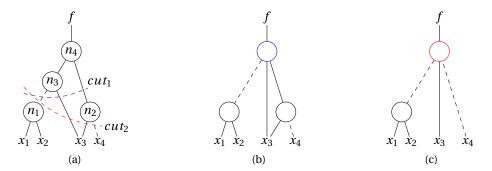

|                                   | by $cut_2$                                                                                                                                                                           | 27      |

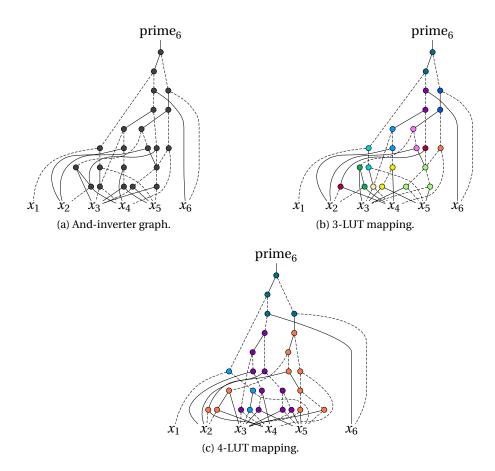

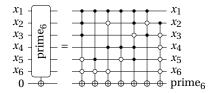

| 2.4                               | LUT mappings for the function $prime_6$                                                                                                                                              | 28      |

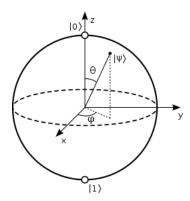

| 3.1<br>3.2                        | The Bloch sphere                                                                                                                                                                     | 32      |

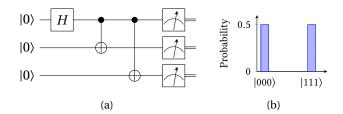

| 0.2                               | expected measurement outcomes                                                                                                                                                        | 35      |

| 3.3                               | A {CNOT, $T$ } circuit                                                                                                                                                               | 36      |

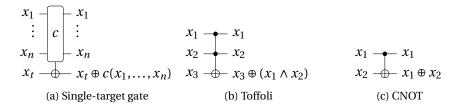

| 4.1                               | Examples of reversible gates                                                                                                                                                         | 40      |

| 4.2                               | Notations for the multiple-controlled Toffoli: the left gate is $T_{1 \wedge 2}(\{1,2\},3)$ in the complete notation and $T(\{1,2\},3)$ in the special notation; for the second gate |         |

|                                   | $T_{\overline{1} \wedge 2}(\{1,2\},3)$ and $T(\{\overline{1},2\},3)$                                                                                                                 | 40      |

| 4.3                               | Example of mapping a single-target gate into Toffoli gates using ESOP decompo-                                                                                                       |         |

|                                   | sition                                                                                                                                                                               | 41      |

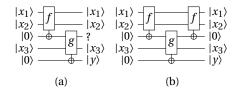

| 5.1                               | (a) Circuit computing $y = g(f(x_1, x_2), x_3)$ with two single-target gates generating an unknown intermediate result. (b) Garbage-free circuit where the intermediate              |         |

|                                   | result has been uncomputed by applying $f$ twice                                                                                                                                     | 48      |

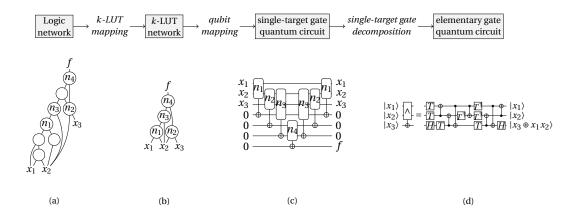

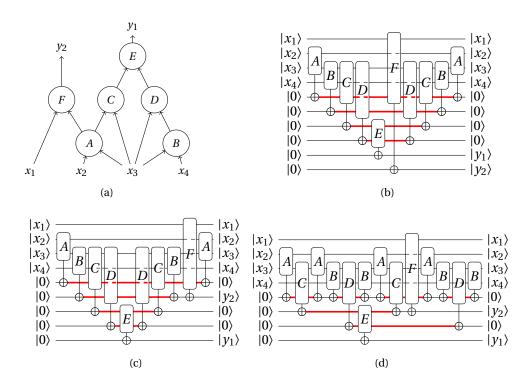

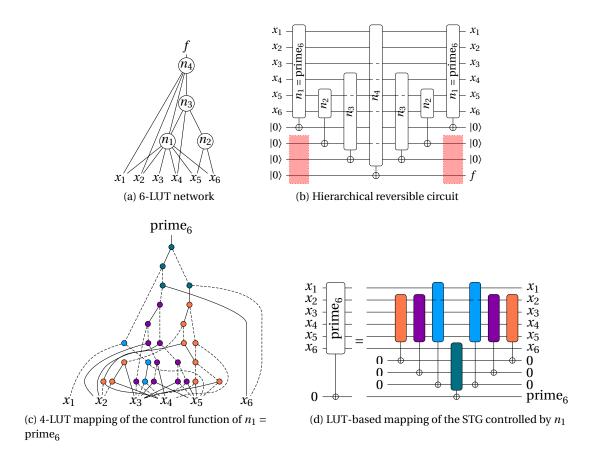

| 5.2                               | k-LUT-based hierarchical quantum compilation flow illustrating the example of                                                                                                        |         |

|                                   | a three-input multi-level logic network performing the Boolean function $f$ (a), mapped into a 2-LUT network for $f$ (b), translated into the reversible circuit for                 |         |

|                                   | the 2-LUT network using the Bennett clean-up strategy (c) then decomposed                                                                                                            |         |

|                                   | into a quantum circuit (d)                                                                                                                                                           | 49      |

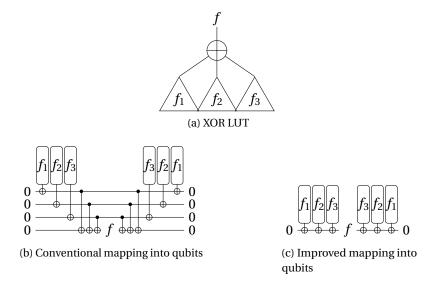

| 5.3                               | Mapping into qubits LUTs performing the XOR function                                                                                                                                 | 51      |

| 5.4 | (a) Example of a DAG. (b)(c)(d) Three different uncomputing strategies: (a) Bennett strategy; (b) space-optimized by reordering; (c) space-optimized by                                                                                                   |     |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | increasing the number of gates                                                                                                                                                                                                                            | 53  |

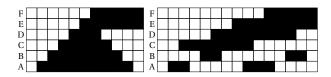

| 5.5 | Two different pebbling strategies for a given DAG                                                                                                                                                                                                         | 55  |

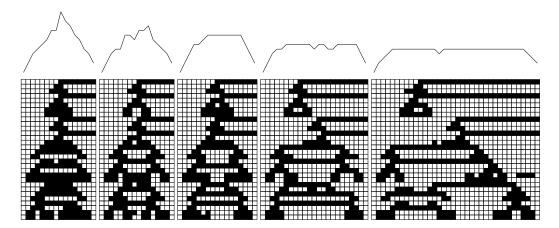

| 5.6 | Illustration of how <i>pebbling</i> maps the given computation into a fixed number of helper qubits: respectively 24 (Add:28, Sub:20, Sqrt:15, Mult:11), 20 (Add:36, Sub:32, Sqrt:21, Mult:9), 16 (Add:28, Sub:24, Sqrt:17, Mult:13), 12 (Add:24, Sub:34, |     |

|     | Sqrt:19, Mult:13) and 10 (Add:34, Sub:38, Sqrt:25, Mult:13)                                                                                                                                                                                               | 58  |

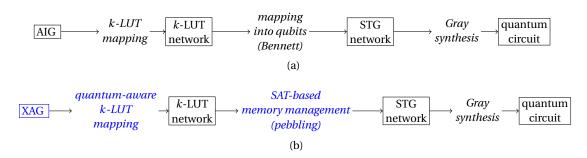

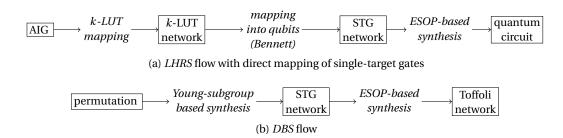

| 5.7 | (a) LHRS flow; (b) ROS flow.                                                                                                                                                                                                                              | 60  |

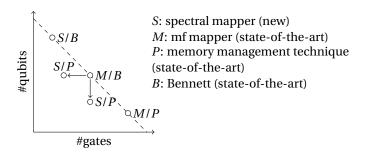

| 5.8 | Qualitative description of ROS's capability                                                                                                                                                                                                               | 60  |

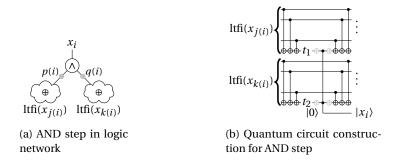

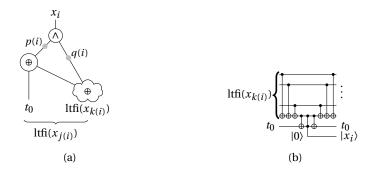

| 6.1 | Illustration of the compilation of an AND step of an XAG into a quantum circuit computing its linear transitive fan-in cones in-place using CNOT gates                                                                                                    | 66  |

| 6.2 | An XAG graph representing the majority-of-three Boolean function                                                                                                                                                                                          | 66  |

| 6.3 | Example in which one transitive fan-in is included in the other and the computed intermediate value can be reused                                                                                                                                         | co  |

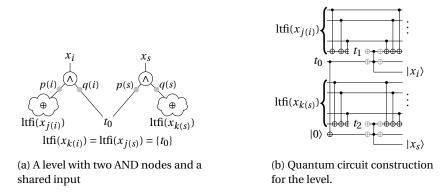

| 6.4 | Illustration of how algorithm 6.2 compiles one level with two AND nodes, $x_i$ and                                                                                                                                                                        | 69  |

| 0.1 | $x_s$ , into a quantum circuit with one single $T$ -stage                                                                                                                                                                                                 | 69  |

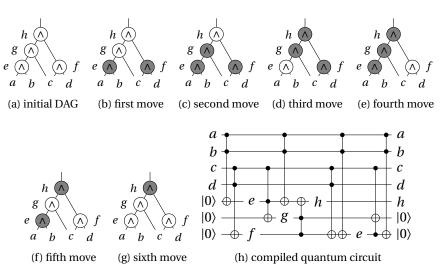

| 6.5 | Illustration of a pebbling strategy for the input DAG (a) using 3 pebbles and 6 moves (b)-(g), and the corresponding compiled reversible circuit of Toffoli gates                                                                                         |     |

|     | (h)                                                                                                                                                                                                                                                       | 71  |

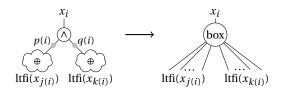

| 6.6 | Illustration of how sections of the XAG are compressed in a box node of the                                                                                                                                                                               |     |

|     | abstract network                                                                                                                                                                                                                                          | 71  |

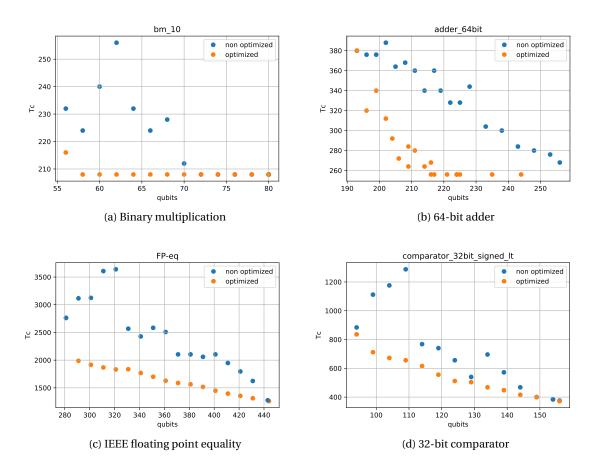

| 6.7 | Optimized and non-optimized pebbling results using different number of pebbles for selected logic networks.                                                                                                                                               | 75  |

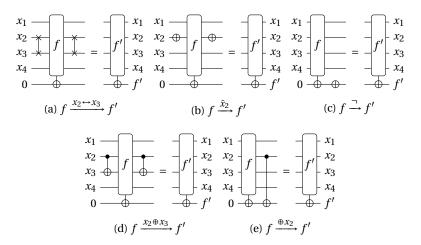

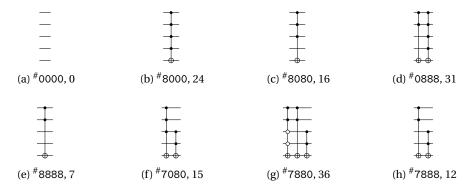

| 7.1 | Reversible circuits implementing the five spectral invariant operations                                                                                                                                                                                   | 80  |

| 7.2 | Synthesized reversible circuit for the function $f$ , obtained performing all the spectral operations to retrieve $f$ from the optimal implementation available in                                                                                        |     |

|     | the database $f_d$ (#0x0888)                                                                                                                                                                                                                              | 81  |

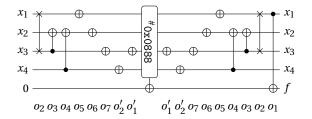

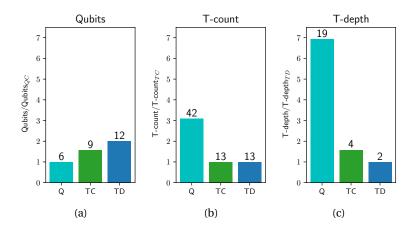

| 7.3 | Bar plots showing the cost functions characterizing the three different imple-                                                                                                                                                                            |     |

|     | mentations for the database functions (Q, TC, TD). The y-axes report: (a) average                                                                                                                                                                         |     |

|     | ratio between number of qubits and best number of qubits in the database, (b)                                                                                                                                                                             |     |

|     | average ratio between $T$ -count and best $T$ -count in the database, (c) average                                                                                                                                                                         |     |

|     | ratio between T-depth and best T-depth in the database. Numbers on the bars                                                                                                                                                                               |     |

|     | show average values of the respective cost function for the three implementations.                                                                                                                                                                        | 84  |

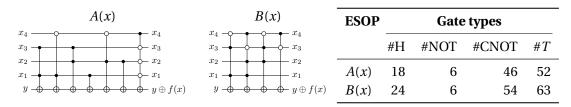

| 7.4 | Synthesis results for two different ESOPs representing the same function $f$                                                                                                                                                                              | 87  |

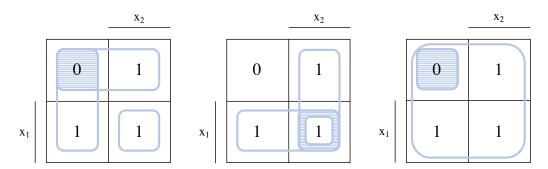

| 7.5 | Three possible ESOP covering for the function $f = x_1 \lor x_2 \ldots \ldots$                                                                                                                                                                            | 89  |

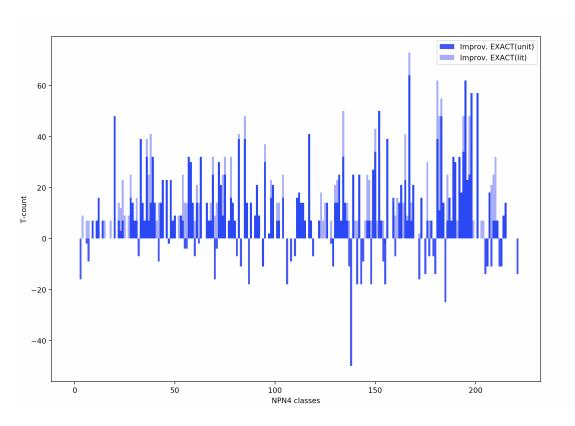

| 7.6 | Histogram showing the improvement of exact methods over <i>PKRM</i> with respect                                                                                                                                                                          |     |

|     | to two different cost functions: number of terms ( <i>EXACT(unit)</i> ) and number of                                                                                                                                                                     | 6.5 |

|     | literals (EXACT(lit))                                                                                                                                                                                                                                     | 91  |

| 7.7 | Two different state-of-the-art compilation flows for Boolean functions that use                                                                                                                                                                           |     |

|     | ESOP-based reversible synthesis                                                                                                                                                                                                                           | 93  |

| 7.8  | tained from the hierarchical reversible synthesis flow                                    | 97  |

|------|-------------------------------------------------------------------------------------------|-----|

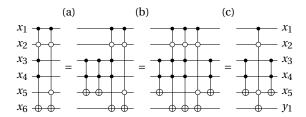

| 8.1  | Rule 2 example. Equivalence rules from [3]: (a) D1, (b) D7, (c) D1                        | 102 |

| 8.2  | Rule 3 example. Equivalence rules from [3]: (a) D2, (b) D3                                | 102 |

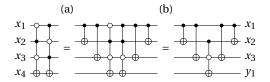

| 8.3  | Example of a linear reversible CNOT circuit                                               | 105 |

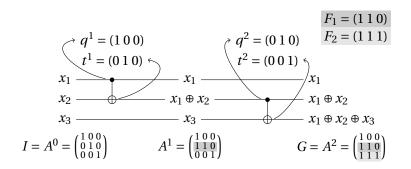

| 8.4  | Illustration of SAT encoding for sample circuit in Example 8.2.3                          | 106 |

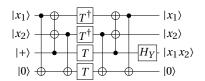

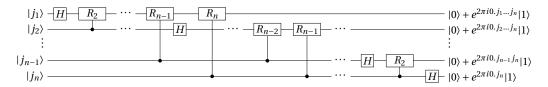

| 9.1  | Efficient circuit computing the quantum Fourier transform                                 | 120 |

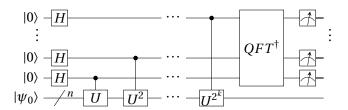

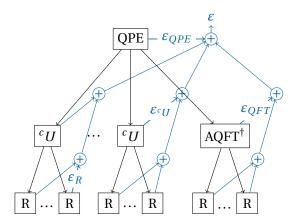

| 9.2  | Quantum circuit performing quantum-phase estimation on an $n$ -qubit system               |     |

| 9.3  | with an accuracy of $k+1$ bits                                                            | 122 |

|      | a code evaluating the overall approximation error $\varepsilon$                           | 125 |

| 9.4  | C++ code for the approximate QFT as consumed by the LLVM prototype                        | 131 |

| 9.5  | Q# implementation of the approximate quantum Fourier transform with epsilon               |     |

|      | declarations                                                                              | 133 |

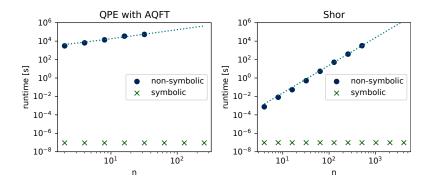

| 9.6  | A comparison between the runtimes of the non-symbolic approach and the                    |     |

|      | symbolic approach developed in this thesis is shown. Each data point marks the            |     |

|      | runtime required for a single evaluation of the $\it T$ function plus a single evaluation |     |

|      | of the $E$ function for the QPE algorithm with approximate QFT and for Shor's             |     |

|      | algorithm. Optimized accuracy parameters are used as input in order to assert             |     |

|      | that the total approximation error is at most $5 \cdot 10^{-3}$ . I provide polynomial    |     |

|      | extrapolations from the collected runtimes for the non-symbolic approach as               |     |

|      | the runtime tops out for bit sizes above 512 for Shor and 32 for QPE                      | 138 |

| 10.1 | Caterpillar's logo                                                                        | 143 |

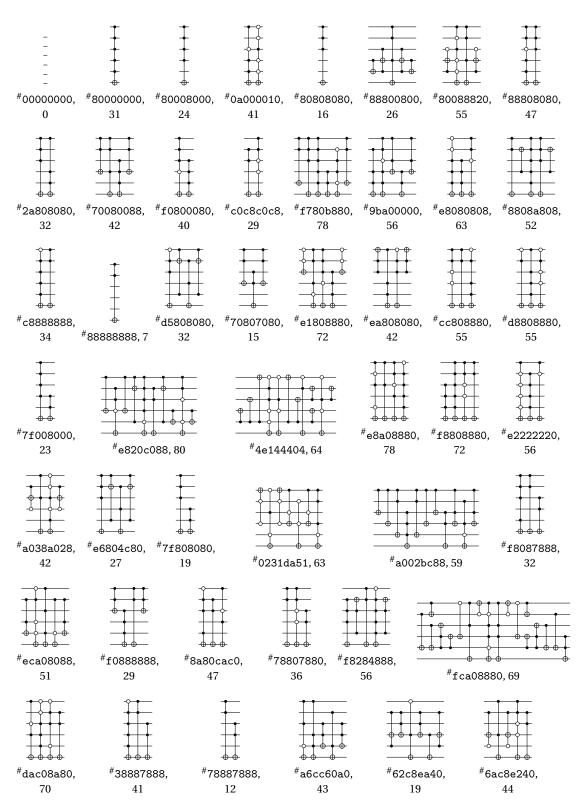

| A.1  | Representative functions, starting point Toffoli networks, and obtained $T$ -count        |     |

|      | for single-target gates with 4-input control functions                                    | 159 |

| A.2  | Representative functions, starting point Toffoli networks, and obtained $T$ -count        |     |

|      | for single-target gates with 5-input control functions                                    | 160 |

## **List of Tables**

| 5.1<br>5.2 | Comparison between the Bennett and the pebbling strategy                                                                                                                                                           |     |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.1        | Compilation results for several arithmetic, floating point and cryptographic designs                                                                                                                               | 74  |

| 7.1        | Specifications of the quantum circuits in the open-source database                                                                                                                                                 | 85  |

| 7.2        | Comparison of different ESOP synthesis methods                                                                                                                                                                     | 92  |

| 7.3        | Comparison between exact method and heuristic for small reversible functions                                                                                                                                       | 94  |

|            | Comparison between PKRM and the pseudo-exact optimal ESOP synthesis integrated into LHRS to synthesize the EPFL arithmetic benchmark Experimental evaluation of different single-target gate decomposition methods | 95  |

| 1.5        | in LHRS on the EPFL arithmetic benchmarks                                                                                                                                                                          | 100 |

| 8.1        | Results of the SAT-based rewriting algorithm                                                                                                                                                                       | 111 |

| 9.1        | Compiler transformations used to optimize the cost and constraint functions                                                                                                                                        | 127 |

| 9.2        | Symbolic expressions for the <i>T</i> -count (T) and total approximation error (E)                                                                                                                                 |     |

|            | as extracted by the LLVM prototype from the source code of various example                                                                                                                                         |     |

|            | programs.                                                                                                                                                                                                          | 137 |

## **List of Acronyms**

AIG And-Inverter Graph. 21, 25, 26, 45, 92, 140

ASIC Application Specific Integrated Circuit. 10

CNF Conjunctive Normal Form. 26

CNOT controlled-NOT. 101

**CPU** Central Processing Unit. 7, 8

**DAG** Directed Acyclic Graph. 48–51, 54, 141, 143, 146

DBS Decomposition-Based Synthesis. 13, 88

EDA Electronic Design Automation. 19, 27

**ELU** Elementary Logic Unit. 5

**EPFL** École Polytechnique Fédérale de Lausanne. 139

**ESOP** Exclusive Sum-Of-Products. xiii, xvi, xvii, xix, 13, 14, 27, 75, 78, 82–89, 91–94, 96, 140, 141, 153, 154

FPGA Field Programmable Gate Array. 25

HLS High Level Synthesis. 19

**HPC** High-Performance Computing. 7

IC Integrated Circuit. 19

ISA Instruction Set Architecture. 8

LHRS LUT-based Hierarchical Reversible Synthesis. xvi, 45, 56

LLVM Low-Level Virtual Machine. 112, 116, 134, 135

LSI Integrated Systems Laboratory. 139

**LUT** Look-Up Table. xiii, xvii, 15, 21, 27, 46, 58, 59, 72, 75, 76, 89, 92–94, 96, 100, 140, 141, 151, 152, 154

MIG Majority-Inverter Graph. 21, 22, 140

MWY Many Worlds Interpretation. 2

NISQ Noisy Intermediate-Scale Quantum. 3, 151

NPN Negation-Permutation-Negation. 22

**NV** Nitrogen Vacancy. 7

PKRM Pseudo-Kronecker Reed Muller. 141

**QCA** Quantum Cellular Automata. 22

QCU Quantum Control Unit. 8

**QEC** Quantum Error Correction. 9

QPU Quantum Processing Unit. 7, 8

**QRAM** Quantum Random Access Machine. 8, 9, 32

QV Quantum Volume. xv, 5, 6

ROS Resource-constrained Oracle Synthesis. xvi, 55, 56

RSA Rivest-Shamir-Adleman. 3

RTL Register Transfer Level. 19

STG Single-target gate. xiii, 48, 49, 75–94, 96

TBS Transformation-Based Synthesis. 13

**XAG** Xor-And-inverter Graph. xiv, 15, 21, 22, 59–61, 72, 78, 140, 141, 143–147, 152, 153

XMG Xor-Majority-inverter Graph. 21, 140

## 1 Introduction

#### 1.1 History of quantum computing

#### 1.1.1 The rise of quantum mechanics

At the beginning of the twentieth century, what we now call *classical* physics was no more capable of explaining observed phenomena in nature. For this reason, it was common to formulate an ad-hoc corrective hypothesis to justify *experimentally observed* phenomena in radiation and atoms theory, and such a hypothesis needed continuous updates.

Theories in physics were predicting absurdities such as the *ultraviolet catastrophe*, a phenomenon for which ideal black bodies should emit an arbitrarily high energy with decreasing emitted wavelength. Consider Rutherford's atomic model [4], theorized in 1911 and based on the well-known gold foil experiment performed in 1909. According to Rutherford, the atomic mass is concentrated at the center of the atom, in the so-called *nucleus* (Rutherford did not use this term in his paper). The nucleus is characterized by a positive charge. Electrons, negatively charged, orbit around the nucleus. According to Maxwell's theory of electromagnetism [5], orbiting negative charges should emit radiation and lose energy. As a consequence, if atoms were subject to the laws of classical physics only, electrons should quickly and inexorably collapse into the nucleus following a spiral trajectory. The amount of time it would take an electron to crash into the nucleus of its atom is about ten picoseconds [6].

It is from similar observations that pioneer scientists developed the wave-particle duality theory. Plank and Einstein showed how light waves could exhibit particle-like properties. In 1900, Plank deduced that electromagnetic radiation could only be emitted and absorbed in discrete packets, i.e., *quanta*, of energy, hence deriving the right intensity spectral distribution for the black body [7]. In 1905, Einstein postulated that Plank's quanta were actual localized particles, later called photons [8]. This theory also explained the photoelectric effect: a phenomenon for which a material hit by electromagnetic radiation emits electrons, only if the radiation's frequency exceeds a given threshold, and independently from its intensity. Besides, De Broglie hypothesized in his doctoral thesis that particles also could have wave-like

properties [9]. In 1926, Schrödinger proposed that electrons in the atoms behave like waves and follow Schrödinger's equation [10], which is solved by a series of wave functions associated with a specific energy. This theory led to the quantum mechanical model of the atom, which is still state-of-the-art.

This duality is reflected in the well-known Copenhagen interpretation of quantum mechanics. This interpretation states that a quantum system is modeled by wave functions and evolves according to the Schrödinger equation. Certain observable quantities, e.g., the position of electrons in an atom, can be measured and the result obtained will depend on the square of the amplitude of the wave function. Measurements cause the wave function to collapse on the obtained result. This interpretation is the one currently accepted and taught to physics students, even if many questioned the distinction between the microscopic quantum world and the macroscopic classical world that the Copenhagen interpretation implies. This distinction suggests that one should not even try to understand quantum behavior [11]. Using Bohr's words: "We must be clear that when it comes to atoms, language can be used only as in poetry. The poet, too, is not nearly so concerned with describing facts as with creating images and establishing mental connections."

A new interpretation is gaining increasing consent: the *Many Worlds Interpretation (MWY)*, proposed in 1957 by Hugh Everett [12] and named by Bryce DeWitt [13]. This interpretation, which exists in many variants, does not make a distinction between the microscopic quantum world, led by the rules of quantum mechanics and the Schrödinger equation, and the macroscopic world that we experience. On the opposite, it states that all the possible outcomes of a quantum experiment exist at the same time in different worlds.

#### 1.1.2 Computing with quantum physics

In the 1980s researchers started to look at the opportunity of using quantum mechanics to boost computing. Feynman postulated that quantum systems could be simulated by quantum computers [15]. In 1985 Deutsch [16] theorized an "universal quantum computer", with properties that are not reproducible by any Turing machine. Using his words during an interview at Wired Magazine in 2007: "The most important application of quantum computing in the future is likely to be a computer simulation of quantum systems, because that is an application where we know for sure that quantum systems in general cannot be efficiently simulated on a classical computer. This is an application where the quantum computer is ideally suited". Later, together with Jozsa, he formulated the *Deutsch-Jozsa algorithm* [17]. He was a supporter of the MWY, which he calls the *multiverse*.

In 1994 Peter Shor proposed an algorithm that solves prime factorization exponentially faster than classical computers [18]. The advent of Shor's algorithm suggested that problems classically considered hard to solve and consequently used in encryption algorithms, e.g., the Rivest–Shamir–Adleman (RSA) algorithm [19], may be solved on a quantum computing system within hours, but would take billions of years on a classical system. In 2001 IBM demonstrated

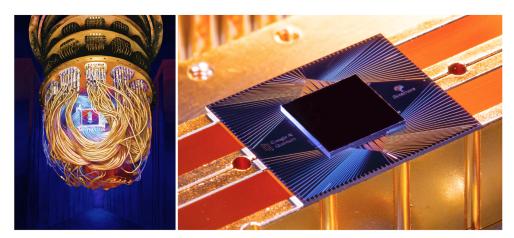

(a) Left: Artist's rendition of Google's Sycamore processor mounted in the cryostat. (Forest Stearns, Google AI Quantum Artist in Residence) Right: Photograph of the Sycamore processor. (Erik Lucero, Research Scientist and Lead Production Quantum Hardware)

(b) System One quantum computer (Image Credit IBM [14]

Shor's algorithm on a 7 qubits system [20]. In 1996 Grover introduced a quantum search algorithm with a quadratic speed-up with respect to classical solutions. Unfortunately, a quantum system capable of performing such an algorithm for sizes that cannot be classically simulated is not available at the time of writing this manuscript.

In 2000 David DiVincenzo laid out the requirements that a quantum system must comply with to be able to perform computation [21]. These criteria are known as *DiVincenzo's criteria*. The first five are necessary for quantum computation: (i) an extensible register of two-level systems, usable as qubits; (ii) the ability to initialize the state of the qubits to a simple fiducial state; (iii) long relevant decoherence times; (iv) a "universal" set of quantum gates; (v) a qubit-specific measurement capability. The remaining two are necessary for quantum communication: (i) the ability to interconvert stationary and flying qubits; (ii) the ability to faithfully transmit flying qubits between specified locations. According to these criteria, new hardware technologies

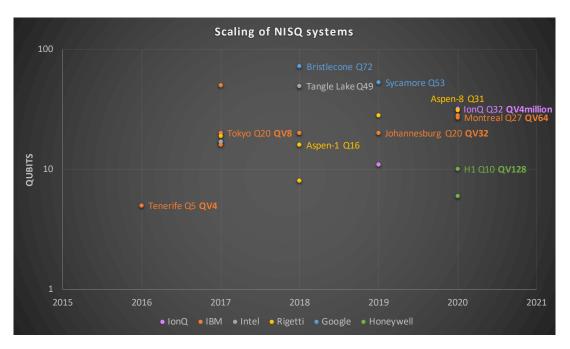

Figure 1.1 – NISQ systems per year of release. Labels: *<name>* Q*<number of qubits>* QV*<quantum volume>*.

are developed as candidates to build scalable quantum computers.

#### 1.2 Quantum computing systems

In the last few years, different computing systems have been developed, known as Noisy Intermediate-Scale Quantum (NISQ) computers. They owe their name to some shared features: few noisy qubits and low-fidelity operations.

Even if current quantum systems are decades of development away from becoming error-corrected universal quantum computers, research is focusing on proving that they are capable of performing tasks beyond the reach of ordinary digital computers. This milestone, called *quantum supremacy*, has been proposed for the first time by Preskill in 2012 [22]. Quantum complexity theory shows that it is not necessary to develop a universal quantum computer to demonstrate quantum supremacy [23]. Besides quantum supremacy, the term *quantum advantage* is often used. Nevertheless, according to Preskill [24]: "In a race, a horse has an advantage if it wins by a nose. In contrast, the speed of a quantum computer vastly exceeds that of classical computers, for certain tasks. At least, that's true in principle."

IBM has recently proposed the Quantum Volume (QV) [25] as a metric to evaluate the ability of a quantum computer to perform complex computation. The complexity of an algorithm is relative to the circuit *width*, i.e., the number of qubits and to the circuit *depth*, i.e., the number of operations performed. The latter depends on many factors such as decoherence time, qubit

fidelity, interconnections, etc.. Randomized model circuits are used to evaluate the system's capabilities: the metric represents the largest squared-shaped model circuit that the system can perform successfully. The QV is now used to compare different quantum computers and enables researchers to quantify the impact of new solutions and design choices.

In the following sections, I will describe four different generations of quantum computers [2], characterized by technologies with promising scalability. The ultimate goal is to fabricate an universal quantum computer, characterized by a large number of qubits, supporting error correction, and long coherence time. Such computer would be capable of performing quantum algorithms promising exponential speed-ups. Fig. 1.1 reports the currently available systems by year of release, showing their number of qubits (Q) and quantum volume (QV), when known.

#### 1.2.1 Trapped ions

The first generation is led by the trapped-ion technology [26]. In an ultra-high vacuum, individual atoms are ionized and trapped using controlled electrical fields. Ions are then used to perform quantum computation by means of an array of individual laser beams (one per ion) and a global beam: the interference between the beams gives the required energy to switch a qubit's state.

The idea of computing with trapped ions and the demonstration of fundamental quantum logic gates date back to 1995 [27, 28]. One approach to build a large computing system is the monolithic design proposed in [29], in which segmented ion traps are fabricated and connected together to build the overall system. Segmented ion traps [30, 31] are architectural models that use DC electrodes to move the ion along trapping pathways and enabling interaction between qubits, i.e., multi-qubit gates. Opposite to the monolithic approach is the fabrication of many Elementary Logic Unit (ELU), optically interconnected [32].

Trapped ions exhibit very long qubits' coherence times, up to 600 seconds [33]. Another advantage of this technology is that both single and two-qubit gates can be implemented with very high fidelity [34]. The achieved state preparation and readout fidelities are better than the one demonstrated by any other technology [35]. Finally, they do not require long calibration steps, as, e.g., superconducting qubits. Even if trapped ions have the highest coherence time over gate time ratio, performing each operation is an order of magnitude slower when compared to the superconducting technology, i.e., typically between 1 to  $100~\mu s$  against tens of nanoseconds. Another drawback is size, as the scaling is slowed down by the fabrication of the required optical control. Finally, this technology is characterized by a high fabrication cost.

Honeywell has presented a 10-qubit system, called H1, with a quantum volume of 128 [36]. The company IonQ develops trapped ions quantum computers with configurable architectures of fully connected qubits. In particular, it has tested single-qubit gates on 79 qubits [37]. IonQ

has recently released its 32-qubit quantum computer achieving the quantum volume of 4 millions [38], which is the highest ever tested.

#### 1.2.2 Superconducting circuits

One of the leading technology to build quantum computing systems is based on superconducting qubits. The first superconducting qubit has been demonstrated in 1999 [39].

Google, Intel, and IBM are developing superconducting quantum technology. IBM is one of the leading companies in quantum computing hardware and since the realization of the first computer in 2016, with 5 qubits, makes the system available on a cloud service, i.e., IBM's quantum experience<sup>1</sup>. In 2017, IBM released on its platform other two quantum computers with 16 and 20 qubits. In January 2018, Intel presented its 49-qubit superconducting quantum processor, Tangle Lake. In March 2018, Google Quantum AI Lab announced its new processor Bristlecone with 72 qubits [40]. In January 2019, IBM announced the first commercial circuitbased integrated 20-qubit quantum computer "IBM Q System One" and the "IBM Q Network" platform [41]. In October 2019, IBM made its 53-qubit system available [42]. At the same time, Google announced the achievement of quantum supremacy, intended as the ability to outperform classical computers on a specific task [43]. Such results were demonstrated on a 53qubit superconducting computer called Sycamore. Sycamore completed in few seconds a task that a state-of-the-art supercomputer would require approximately 10,000 years to perform, according to Google. Later, IBM expressed some criticism on Google's achievement [44], pointing out that the task can be performed faster on certain classical computing processors, i.e., in only 2.5 days. IBM also pointed out that according to the first formulation of quantum supremacy, as by Preskill [22], this is only achieved if the selected task is unfeasible on classical computers.

IBM has computed the QV of several of its quantum computers, namely the 5-qubit Tenerife (2017), the 20-qubit Tokyo (2018), the 20-qubit Johannesburg (2019), and the 27-qubit Montreal (2020), showing an exponential growth resembling the well known Moore's law. The Montreal quantum computer achieves a quantum volume of 64 [45].

In addition to IBM, Intel, and Google, the start-up company Rigetti focuses on building superconducting quantum computers. The company has released in 2019 a quantum system called Aspen-4, for which a quantum volume of 8 has been demonstrated [46]. Rigetti's latest quantum computer, called Aspen-7 features 28 qubits and average gate times of 80ns-340ns, depending on if it is a single- or a two-qubit gate.

Supercomputing qubits have a smaller footprint and faster intrinsic gate times with respect to ion traps, reaching physical speeds of MHz. Nevertheless, fabrication and placement of the necessary control wiring for large qubits array is an unsolved engineering problem, that may compromise the scalability of these systems. Finally, this technology requires many calibration

$<sup>^{1}</sup> https://web.archive.org/web/20160927160441/http://www.research.ibm.com/quantum/$

steps, due to the device mismatch which characterizes the fabrication process.

#### 1.2.3 Nitrogen vacancies and quantum dots

The third generation of quantum computers counts extremely promising but less developed technologies with respect to the previous generations. The technologies in this generation promise high speed, in the order of the GHz and small sizes (nm-um). Impurities in diamond have long been of interest as a potential technology for both large-scale quantum computing and communications, in particular the one based on the *Nitrogen Vacancy (NV)* [47]. Diamond-based quantum technology do not require high infrastructure cost, a vacuum is not needed, and it works at a temperature of *only* 4K, rather than the 4mK needed by the superconducting qubits.

Another promising technology is the one based on quantum dots, which traps electrons at the boundary between different superconductors. The single qubit has been demonstrated in [48], and a two-qubit gate is realized in [49]. Quantum dots have the potential speed and integration density, thanks to the advanced silicon fabrication technology. This technology has demonstrated sufficient thermal robustness to enable computing a universal set of quantum gates, hence including two-qubit gates, at temperatures greater than 1K [50]. Intel is currently researching this technology, which promises small physical sizes, stability, and duration.

#### 1.2.4 Anyonic particles

The fourth and last generation consists of the anyonic or topological quantum computers [51]. Such systems aim at suppressing errors using the fundamental physics of the system, with states naturally protected from decoherence. Even if this technology promises easy-to-scale systems with low error rates, the existence of anyonic (or Majorana) particles in engineered systems has not been yet demonstrated.

#### 1.3 Software requirements

Previous sections have discussed the requirements of quantum computing hardware according to DiVincenzo's criteria and described state-of-the-art computing systems. This section focuses on the software resources necessary to operate a quantum computer. It starts with a description of the model of computation using a Quantum Processing Unit (QPU) and gives details on the required control software.

#### 1.3.1 Model of computation

A quantum computer is not to be considered as an independent computing system but as a coprocessor to classical computation [1], integrated into a future High-Performance Computing

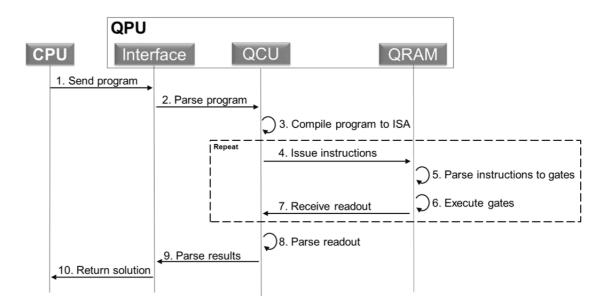

Figure 1.2 – Sequence diagram illustrating how the QPU interacts with a host CPU, image from [1].

(HPC) architecture. Fig. 1.2 (from [1]) shows a sequence diagram that models the interaction between the Central Processing Unit (CPU) and the Quantum Processing Unit (QPU).

The computing core of the QPU is the Quantum Random Access Machine (QRAM), a machine with the ability to perform a set of operations on quantum registers: quantum state preparation, unitary operations, and measurements [52]. Computation on a quantum register consists of operations modifying the state of the qubits. Such states are in a superposition of the classical states  $|0\rangle$  and  $|1\rangle$  and are represented by two complex coefficients which encode the probability to obtain the classical 0 or 1 upon measurement in the computational basis. Any gate operating on a qubit state has to guarantee that the probabilities of measurement outcomes sum up to one, and as such, they are represented by norm-preserving unitary matrices. Hence, any quantum operation is reversible. The QRAM receives instructions from a predefined set of unitary operations. The set of unitaries is a *universal quantum library*, as it must allow the QRAM to perform any quantum algorithm with arbitrary precision.