### Speed/Power/Area Trade-offs for High Speed Inter Layer Data Transmission in 3D Stacked ICs

THÈSE Nº 6278 (2014)

PRÉSENTÉE LE 26 AOÛT 2014 À LA FACULTÉ DES SCIENCES ET TECHNIQUES DE L'INGÉNIEUR LABORATOIRE DE SYSTÈMES MICROÉLECTRONIQUES PROGRAMME DOCTORAL EN MICROSYSTÈMES ET MICROÉLECTRONIQUE

### ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

PAR

### Giulia BEANATO

acceptée sur proposition du jury:

Dr G. Boero, président du jury Prof. Y. Leblebici, Prof. G. De Micheli, directeurs de thèse Prof. A. P. Burg, rapporteur Dr F. Clermidy, rapporteur Prof. A. K. Coskun, rapporteuse

Considerate la vostra semenza: fatti non foste a viver come bruti, ma per seguir virtute e canoscenza. — Dante Alighieri

To the memory of my grandmas...

## Acknowledgements

This dissertation is the final snapshot of four and a half years of days, nights and weekends digging into some of the many challenges someone faces in order to stack multiple silicon layers. None of this work would have been accomplished if it wasn't for Prof. Yusuf Leblebici and Prof. Giovanni De Micheli, who gave me the opportunity to pursue this research and guided me throughout it. Research is an endless task that rapidly becomes an addiction. I have to thank the member of the thesis committee Prof. Burg, Prof. Coskun, Dr. Clermidy and Prof. Boero, for evaluating my work putting an end to my PhD dependence.

During these years I had the chance to share the lab with both amusing and talented people. Among them I have to particularly acknowledge several persons that marked my life. My officemate Ale who supported me both technically and as a friend, we never stopped arguing and fighting, it was fun and I learned a lot. Hossein, a brilliant officemate for 3 years and a remarkable person. Kiarash and Mahsa who provided for the "tuc of the day" and great support while I was struggling with endless problems, I really hope I've helped them at least half as much as they've helped me. Davide who listened to me when I really needed. Yuksel, Michael, Paolo, Igor and all the people that shared their knowledge and experience with me. I am extremely grateful to Alain for his everlasting patience regarding all the times I knocked on his door with some linux-related issue. I would not dare imagining how could I have endured without the invaluable support of Marie and Melinda.

Then, I should admit I owe a big debt of gratitude to my PhD, for giving me the opportunity to run into amazing people like Sara, Francesco, Alessia, Romain, Erifili, Marco(s), Mauro, Andrea(s), Luca, Alessandro(s), Stefano, ... and all the friends I was so lucky to meet but I cannot mention one by one without occupying too many pages.

The last year of a PhD is supposed to be the most stressful, but thanks to my sister who had the courage to come live with me and the theatre groups I joined I will remember it as an amazing year. I have to thank the ImproPas for all the amusement and laughter we had while bringing new people and situations into being. At the same time I'm also extremely grateful to the Catalyst and all the "enemies of the people" who accepted me as part of the group. I had a wonderful time and a lot of fun rehearsing almost everyday with all of you, we had a great run. I do owe a really special thank to Paolo, Enrico e Wolty, although the kilometres are separating us, they've always been there for me and I know I can always count on them when I need.

Finally, the deepest thank should go to Graziana, Gigi and Elena. Family is the most important thing in life, anything I achieved and will achieve is worth it just because I can share it with them.

Grazie!

Lausanne, 19 June 2014

G. B.

### Abstract

Technology scaling is now struggling to meet the expectations dictated by Moore's Law due to complexity and cost. In particular, interconnects have become a major performance bottle-neck for planar chip multi-processors and are rapidly dominating die area and power dissipation. These limiting factors need to be addressed at the architectural level. A promising option explored in the last few years are *Three Dimensional (3D)* architectures exploiting *Through Silicon Via (TSV)*. In fact, TSV interconnects have the potential to reduce the interconnect wire length and, at the same time, offer high vertical connection density.

In the last decade several groups in both academia and industry have developed their own TSV technology exploiting different designs, fabrication techniques and materials. Given the diversity of the parameters characterizing TSV technology, the choice of the most appropriate 3D interconnect for a specific design is of utmost importance. Nevertheless, the silicon area overhead due to the TSV insertion and the non-negligible TSV capacitance might hinder the performance improvements offered by 3D-ICs. Hence, the IC designers are now required to find circuit design techniques that fully exploit the potential of the available 3D interconnects. This dissertation discusses circuit design solutions for cross-chip communication through state-of-the-art TSV channels. Different TSV channels and interconnect topologies have been explored with the aim of achieving the area, power and performance requirements of 3D-stacked systems. More specifically, the contribution of this thesis consists of proposing design solutions to leverage the high bandwidth and low-delay connection provided by TSV links minimizing the cost in terms of silicon area and capacitance.

A silicon-proven analytical model of the TSV channel is presented, which provides good correlation between simulations and chip measurements. The model is then extensively utilized to emulate the 3D I/O links while designing the interconnect circuits.

The following parts of the thesis aims to demonstrate the efficiency of different 3D interconnection topologies in complete systems. A *configurable network architecture exploiting a fully parallel TSV bus* is proposed. The goal is to create a system composed of a cluster of processing elements, placed on a logic layer, and multiple layers of SRAM modules constituting a single shared L1 memory. The performance of a shared-L1 memory critically depends on the architecture of the interconnect between processors and memory banks. The required low-latency communication is achieved by a 3D logarithmic network structure. This architecture shows significant improvements in both area and latency compared to the planar 2D implementation.

Nevertheless, a parallel TSV bus is still extremely area consuming. In order to balance inter-

#### Abstract

layer bandwidth offered by TSVs and their silicon area occupation, a *high data-rate 3D serial link* is proposed. The high-speed serial 3D link optimizes both the inter-layer communication speed and the interconnect area occupation, still guaranteeing low-power communication. The proposed *serializer-deserializer (SERDES)* circuits have been explored across a variety of state-of-the-art TSV technologies.

A modular 3D stacked multi-processor platform, 3D-MMC, featuring the 3D serial connection macro has been designed to demonstrate the potential of the proposed interconnect topology. The analysis of the systems' wiring characteristics demonstrates that the reduction in the number of TSVs obtained with the adoption of the serial vertical connection improve the routing congestion of the 3D system.

In the final part of this dissertation, a test vehicle based on the 3D-MMC architecture is presented. A prototype of the 3D multi-processor system has been designed, fabricated and tested. The final 3D system has been obtained by stacking *Known Good Dies(KGD)* using an in-house via-last TSV process. The experimental results obtained from simulations and measurements on the fabricated samples demonstrate that the system exhibits multiple Gbps vertical data bandwidth while limiting the number of TSVs.

Finally, the thesis is concluded with a summary of the contributions and a discussion on the future work.

Key words: 3D ICs, Through Silicon Vias TSVs, Chip Multi-Processors CMPs, high speed serial links.

### Sommario

L'aumento della complessità e del costo legato alla riduzione delle dimensioni della tecnologia CMOS stanno rendendo sempre piú difficile rispettare le aspettative dettate dalla legge di Moore. In particolare, le interconnessioni sono diventate una delle maggiori cause limitanti per le prestazioni dei multiprocessori planari e stanno rapidamente dominando sia l'area che il consumo di potenza dei chip. Questi fattori limitanti devono essere affrontati a livello architetturale. Una promettente opzione esplorata negli ultimi anni sono le architetture tridimensionali che utilizzano le interconnessioni attraverso il silicio, TSVs. Infatti, le TSV hanno la caratteristica di ridurre la lunghezza delle interconnessioni offrendo allo stesso tempo un'alta densità di connessione verticale.

Nell'ultimo decennio diversi gruppi sia in accademia che in industria hanno sviluppato la propria tecnologia di fabbricazione delle TSV utilizzando differenti design, techniche e materiali. Data la diversità dei parametri che caratterizzano le tecnologie TSV, la scelta della tecnologia piú adatta per un particolare design é di primaria importanza. Nonostante ció, l'aumento dell'area dovuta all'instanziamento delle TSV e la loro capacità parassita non trascurabile potrebbero offuscare i benefici offerti dalla tecnologia 3D. Di conseguenza, nuove tecniche di design devono essere esplorate per sfruttare al massimo le potenzialità della tecnologia 3D. Questa tesi propone soluzioni circuitali per la comunicazione tra diversi chip attraverso le TSV disponibili oggi. Varie TSV e topologie di interconnessione sono state esplorate con lo scopo di raggiungere le aspettative sulle prestazioni promesse dalla tecnologia 3D. In particolare, il contributo di questa tesi consiste nel proporre soluzioni per ottimizzare il compromesso tra l'alta banda e la velocità delle TSV riducendo al minimo il costo in termini di utilizzo di area e capacità parassita.

Come prima cosa viene presentato un modello analitico delle TSV validato da misure su silicio, garantendo quindi una buona correlazione tra simulazioni e misure. Il modello viene quindi ampiamente utilizzato per emulare il link 3D durante il design dei circuiti di interconnessione. La parte seguente della tesi ha come scopo dimostrare l'efficienza di diverse topologie di interconnessione inserite in sistemi completi. Viene proposta un'architettura di network combinatoria che utilizza un bus parallelo di TSV. Lo scopo è di interconnettere un sistema composto da un gruppo di processori localizzati su un layer di logica, ad una memoria condivisa di primo livello composta da vari layer occupati da blocchi di SRAM. L'architettura dell'interconnessione tra processori e memoria è un fattore critico per le prestazioni di una memoria di livello 1 condivisa. La comunicazione a bassa latenza viene ottenuta tramite una struttura di network logaritmica in 3D. Questa architettura mostra un incremento significativo

#### Abstract

sia in termini di area che latenza se comparata all'implementazione planare in 2D.

Ció nonostante un bus parallelo di TSV occupa una porzione significante di area. Un 3D link seriale ad alta velocità viene quindi proposto per bilanciare la bandwidth offerta dalle TSV e la loro area. Il 3D link seriale ad alta velocità ottimizza sia la comunicazione tra layer che l'occupazione di area, garantendo allo stesso tempo un basso consumo in potenza. I circuiti di serializzazione-deserializzazione sono stati esplorati per diverse tecnologie di TSV.

Un multi-processore modulare tridimensionale, 3D-MMC, che utilizza una connessione interlayer seriale è stato progettato per dimostrare le potenzialità della topologia proposta. L'analisi delle interconnessioni del sistema dimostra che la riduzione del numero di TSV ottenuta attraverso la serializzazione riduce la congestione del routing.

Nella parte finale della tesi viene presentato un prototipo che si basa sull'architettura 3D-MMC. Il prototipo del multi-processore 3D è stato progettato, fabbricato e testato. Il sistema 3D finale è stato ottenuto mettendo uno sopra l'altro i chip testati funzionanti, interconnettendoli con un processo di fabbricazione delle TSV sviluppato in-house. I risultati sperimentali ottenuti dalle simulazioni e dalle misure sui chip fabbricati dimostrano che il sistema puó arrivare a funzionare a diversi Gbps di bandwidth verticale limitando il numero di TSV.

Infine, la tesi si conclude con un sommario dei contributi scientifici ed una discussione sul lavoro da sviluppare in futuro.

Parole chiave: 3D ICs, Through Silicon Vias TSVs, Chip Multi-Processors CMPs, high speed serial links.

# Contents

| Acknowledgements |                                         |                                                                           | v   |  |  |

|------------------|-----------------------------------------|---------------------------------------------------------------------------|-----|--|--|

| Ał               | Abstract (English/Français/Italian) vii |                                                                           |     |  |  |

| Li               | List of figures                         |                                                                           |     |  |  |

| Li               | st of                                   | tables                                                                    | xix |  |  |

| 1                | Intr                                    | oduction                                                                  | 1   |  |  |

|                  | 1.1                                     | From 2D to 3D ICs                                                         | 3   |  |  |

|                  |                                         | 1.1.1 System in package                                                   | 3   |  |  |

|                  |                                         | 1.1.2 2.5D IC                                                             | 4   |  |  |

|                  |                                         | 1.1.3 3D IC                                                               | 4   |  |  |

|                  | 1.2                                     | Objectives and contributions                                              | 9   |  |  |

|                  | 1.3                                     | Thesis organization                                                       | 11  |  |  |

| 2                | Thr                                     | ough Silicon Vias Technology                                              | 13  |  |  |

|                  | 2.1                                     | TSV fabrication technologies                                              | 14  |  |  |

|                  | 2.2                                     | TSV analytical model                                                      | 19  |  |  |

|                  |                                         | 2.2.1 Model validation                                                    | 25  |  |  |

|                  | 2.3                                     | Summary                                                                   | 27  |  |  |

| 3                | 3D-                                     | LIN: a Logarithmic Network for Inter-Layer Memory to Processor Communica- | -   |  |  |

|                  | tion                                    | l                                                                         | 29  |  |  |

|                  | 3.1                                     | Problem formulation                                                       | 29  |  |  |

|                  | 3.2                                     | State of the art                                                          | 31  |  |  |

|                  | 3.3                                     | 3D parallel computing                                                     | 32  |  |  |

|                  | 3.4                                     | 2D network                                                                | 33  |  |  |

|                  |                                         | 3.4.1 Network architecture protocol                                       | 35  |  |  |

|                  |                                         | 3.4.2 Request block                                                       | 35  |  |  |

|                  |                                         | 3.4.3 Response block                                                      | 35  |  |  |

|                  | 3.5                                     | 3D interconnect network                                                   | 35  |  |  |

|                  |                                         | 3.5.1 Network architecture                                                | 38  |  |  |

|                  |                                         | 3.5.2 Network operation                                                   | 40  |  |  |

|                  | 3.6                                     | Simulations and results                                                   | 41  |  |  |

|                  |                                         |                                                                           |     |  |  |

### Contents

|   |     | 3.6.1 Physical analysis                                            | 43 |

|---|-----|--------------------------------------------------------------------|----|

|   |     | 3.6.2 Power analysis                                               | 47 |

|   |     | 3.6.3 Timing analysis                                              | 49 |

|   | 3.7 | Summary                                                            | 51 |

|   | 3.8 | Acknowledgements                                                   | 52 |

| 4 | Des | ign and Analysis of High Speed Serial Vertical Links               | 53 |

|   | 4.1 | Problem formulation                                                | 53 |

|   | 4.2 | State of the art                                                   | 54 |

|   | 4.3 | SERDES circuit design                                              | 55 |

|   | 4.4 | Design exploration                                                 | 58 |

|   |     | 4.4.1 TSV channel                                                  | 59 |

|   |     | 4.4.2 Area analysis                                                | 60 |

|   |     | 4.4.3 Energy analysis                                              | 62 |

|   |     | 4.4.4 Trade-off analysis                                           | 64 |

|   | 4.5 | 8-bit serial link                                                  | 65 |

|   |     | 4.5.1 Jitter analysis                                              | 66 |

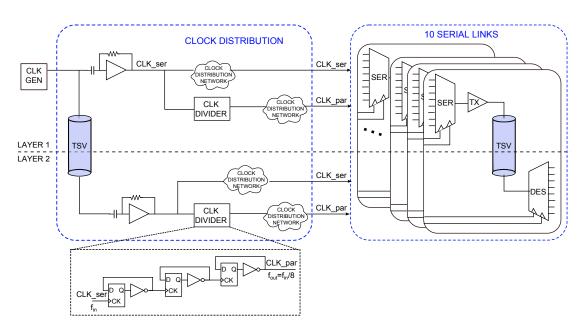

|   |     | 4.5.2 Clock distribution                                           | 70 |

|   | 4.6 | Double data rate TSV serial link                                   | 71 |

|   | 4.7 | Summary                                                            | 73 |

| 5 | TSV | Serialization Impact on a 3D Modular Multi-Core Processor Platform | 75 |

|   | 5.1 | Problem formulation                                                | 75 |

|   | 5.2 | State of the art                                                   | 76 |

|   | 5.3 | 3D modular multi-core architecture                                 | 77 |

|   |     | 5.3.1 2D layer architecture                                        | 77 |

|   | 5.4 | Serial vs. parallel vertical link                                  | 79 |

|   |     | 5.4.1 Physical design                                              | 80 |

|   | 5.5 | Routing analysis                                                   | 83 |

|   | 5.6 | Summary                                                            | 86 |

| 6 | MIF | ACLE: a 3D Multi-core Processor Test Chip                          | 87 |

|   | 6.1 | Problem formulation                                                | 87 |

|   | 6.2 | State of the art                                                   | 88 |

|   | 6.3 | MIRACLE                                                            | 89 |

|   |     | 6.3.1 Homogeneous and modular approach                             | 90 |

|   | 6.4 | 3D specific macro architecture and circuit design                  | 92 |

|   |     | 6.4.1 TSV redundancy and yield collection                          | 92 |

|   |     | 6.4.2 Layer identification                                         | 94 |

|   |     | 6.4.3 Clocking scheme and data transmission                        | 95 |

|   |     | 6.4.4 Physical Design                                              | 96 |

|   | 6.5 | In-house 3D stacking process                                       | 96 |

|   |     | 6.5.1 Process steps                                                | 98 |

### Contents

| 6.6    | Thermal evaluation               | 100 |  |

|--------|----------------------------------|-----|--|

| 6.7    | Design verification              | 101 |  |

|        | 6.7.1 FPGA emulation             | 102 |  |

| 6.8    | Prototype verification           | 103 |  |

|        | 6.8.1 3D oriented testing policy | 104 |  |

|        | 6.8.2 Testing setup              | 107 |  |

|        | 6.8.3 2D prototype testing       | 107 |  |

|        | 6.8.4 3D prototype               | 108 |  |

| 6.9    | Software approach                | 108 |  |

| 6.1    | 0 Performance evaluation         | 113 |  |

| 6.1    | 1 Summary                        | 114 |  |

| 6.12   | 2 Acknowledgements               | 115 |  |

| 7 Sur  | mmary and Conclusions            | 117 |  |

| 7.1    | Summary                          | 117 |  |

| 7.2    | Main contributions               | 118 |  |

| 7.3    | Future work                      | 119 |  |

| Biblio | Bibliography 13                  |     |  |

# List of Figures

| 1.1  | Delay of Metal 1 and global wiring vs. technology node [2]                           | 1  |

|------|--------------------------------------------------------------------------------------|----|

| 1.2  | 3D interconnect roadmap by IMEC                                                      | 2  |

| 1.3  | Samsung PoP technology.                                                              | 3  |

| 1.4  | Intel Co-PoP technology                                                              | 3  |

| 1.5  | Virtex-7 2000T FPGA from Xilinx                                                      | 5  |

| 1.6  | Micro-channel based liquid cooling test vehicle from a collaboration between         |    |

|      | EPFL and IBM, courtesy of LSM.                                                       | 6  |

| 1.7  | WIOMING chip from ST-Ericson, ST-Microelectronics and CEA-Leti.                      | 8  |

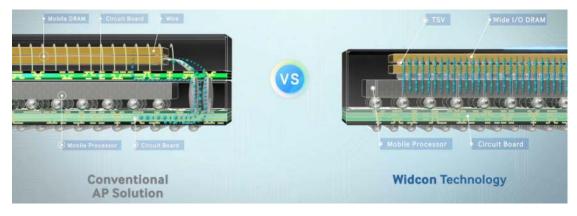

| 1.8  | Widcon technology from Samsung.                                                      | 8  |

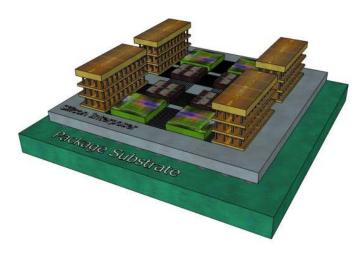

| 1.9  | 2.5D+3D IC. Courtesy of Hsien-Hsin Lee                                               | 9  |

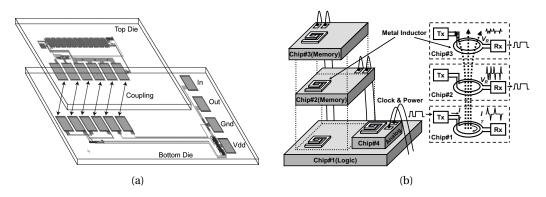

| 2.1  | (a) Capacitive coupling [21] and (b) Inductive inter-chip signaling [22] for 3D ICs. | 14 |

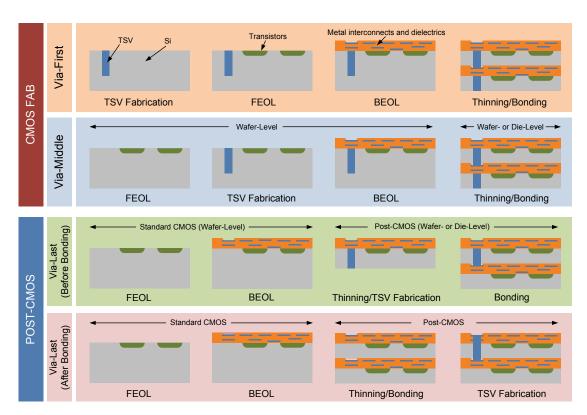

| 2.2  | Summary of the 3D integration scenarios based on the TSV type [23]                   | 15 |

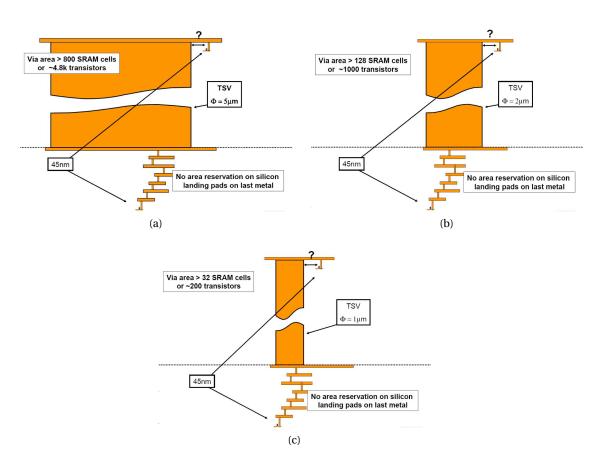

| 2.3  | Typical TSV footprint compared to FEOL structures in a 45 nm CMOS process            |    |

|      | for 5 $\mu$ m, (a), 2 $\mu$ m (b) and 1 $\mu$ m (c) TSV diamater [24]                | 16 |

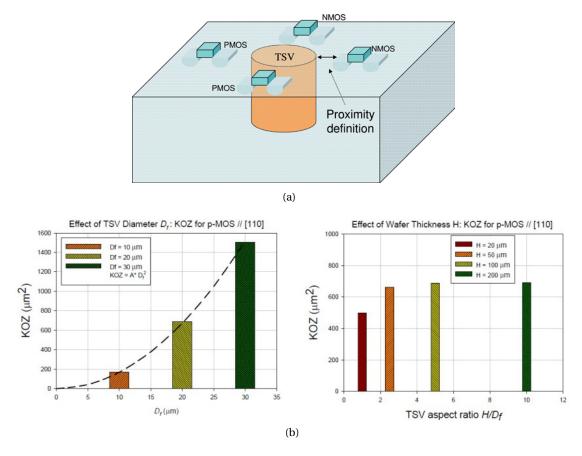

| 2.4  | a)Simplified TSV interconnect KOZ requirements and b) KOZ for different TSV          |    |

|      | diameters (on the left) and TSV height (on the right) [25].                          | 17 |

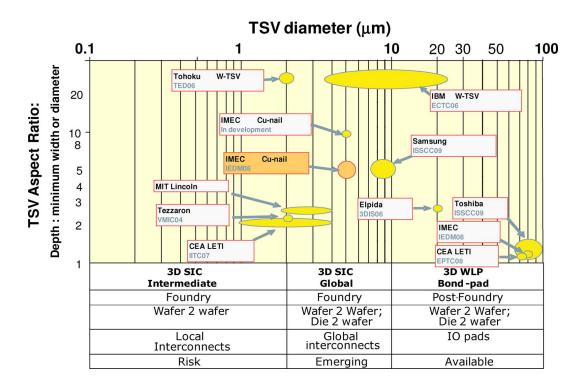

| 2.5  | Overview of the 3D TSV technologies as function of the TSV diameter and aspect       |    |

|      | ratio [33]                                                                           | 18 |

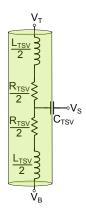

| 2.6  | Electrical model of a single TSV channel.                                            | 19 |

| 2.7  | TSV C-V curve computed with Sdevice simulator (dashed lines), measurements           |    |

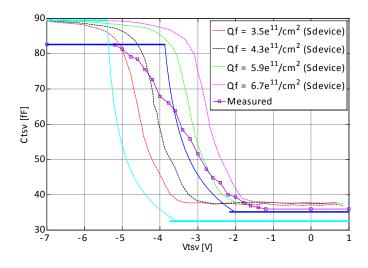

|      | [34] (squares) and the proposed analytical model (solid lines).                      | 22 |

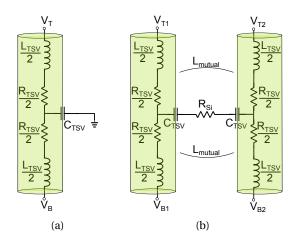

| 2.8  | TSV coupling a) directly to ground, b) to a neighbouring TSV                         | 23 |

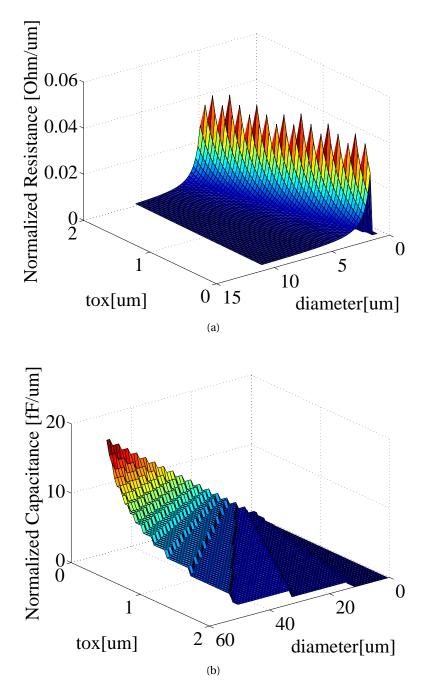

| 2.9  | Normalized TSV parasitics a) resistance and b) capacitance                           | 24 |

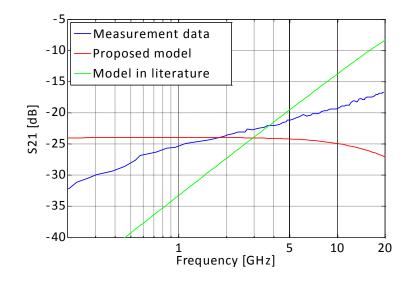

| 2.10 | S21 parameter from the proposed model                                                | 25 |

| 2.11 | a) Illustration of the two-tier chip stack used for the daisy-chain resistance       |    |

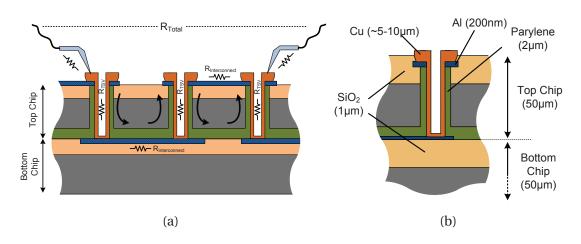

|      | measurements and b) illustration of the TSV used [23]                                | 26 |

| 2.12 | a) Resistance of 4 rows after 64 resistance measurements [23]                        | 26 |

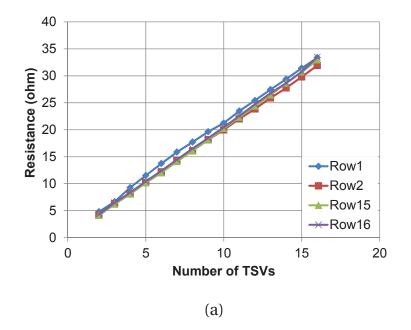

| 3.1  |                                                                                      | 32 |

| 3.2  |                                                                                      | 34 |

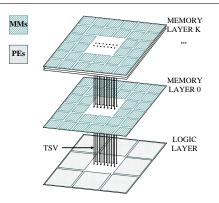

| 3.3  | 3D chip architecture                                                                 | 36 |

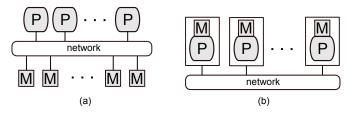

| 3.4  | Block schematic of the 3D-LIN                                                        | 37 |

|      |                                                                                      |    |

### List of Figures

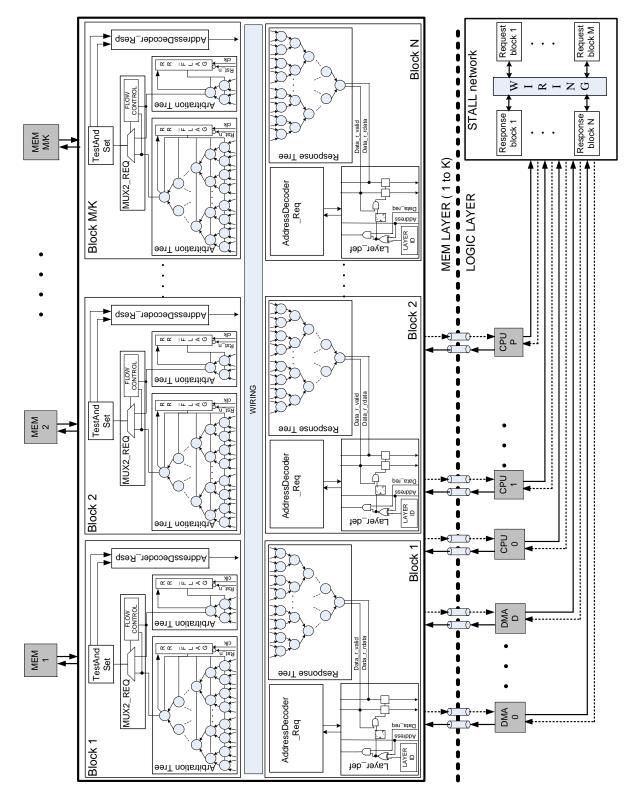

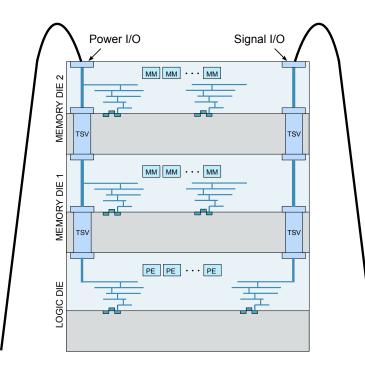

| 3.5  | Cross section schematic of the 3D stacked system.                                           | 38 |

|------|---------------------------------------------------------------------------------------------|----|

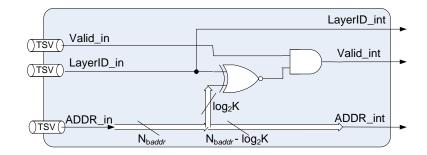

| 3.6  | Schematic of the layer selection block.                                                     | 39 |

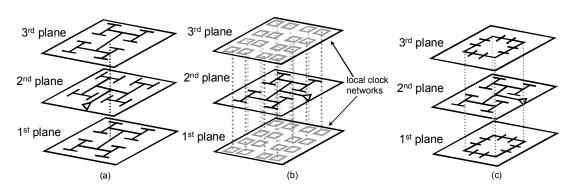

| 3.7  | Solutions for the 3-D clock distribution network [60], (a) H-trees, (b) H-tree and          |    |

|      | local rings/meshes, (c) H-tree and global rings.                                            | 40 |

| 3.8  |                                                                                             | 42 |

| 3.9  | Input/Output connections: I/O signals are connected to the logic layer, I/Os for            |    |

|      | power delivery are connected to all layers.                                                 | 43 |

| 3.10 | Area occupied by the network in the 3D system.                                              | 44 |

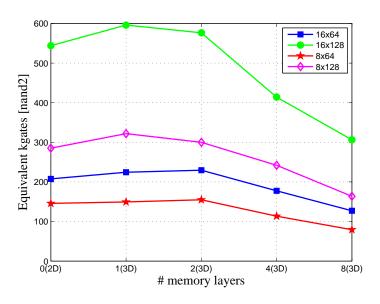

| 3.11 | Area of the Stall/Valid Network on the logic layer (blue) and area of the data              |    |

|      | Network on each memory layer (green) for different number memory layers                     |    |

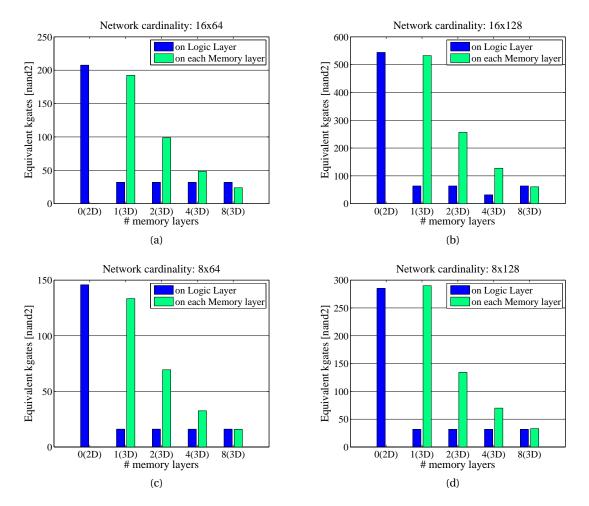

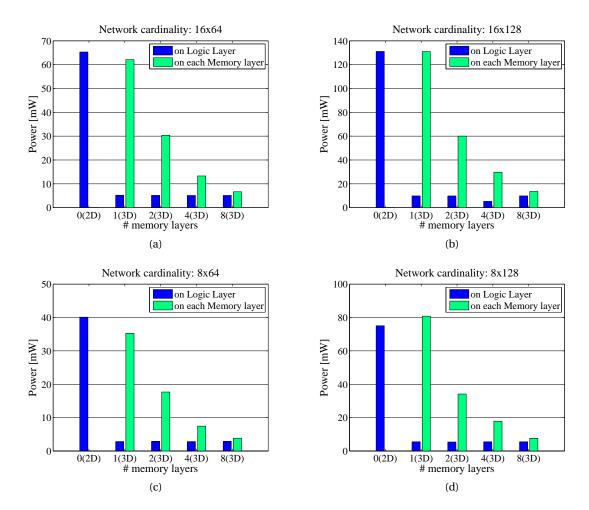

|      | stacked on top of the logic layer.                                                          | 45 |

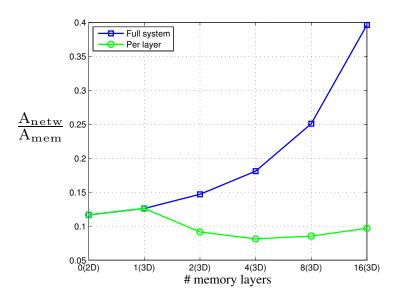

| 3.12 | Area of the network over the area of the memory for each memory layer(green),               |    |

|      | and for the whole system(blue).                                                             | 46 |

| 3.13 | Area of the 3D chip normalized to the area of the 2D implementation.                        | 47 |

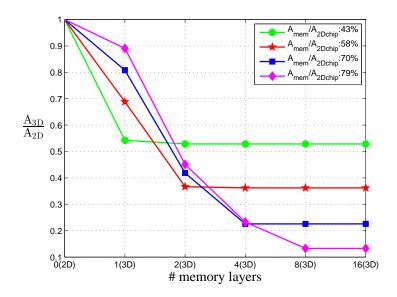

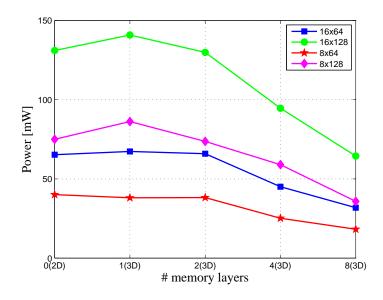

| 3.14 | Dynamic power consumed by the Stall/Valid Network on the logic layer (blue)                 |    |

|      | and dynamic power consumed by the data Network on each memory layer                         |    |

|      | (green) for different number memory layers stacked on top of the logic layer.               | 48 |

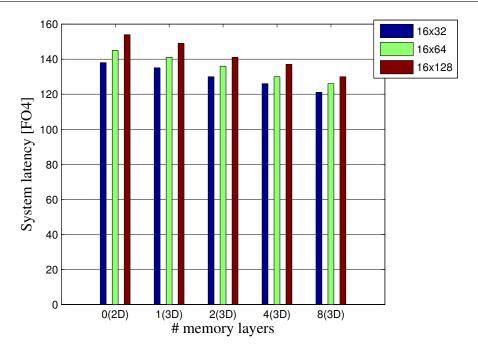

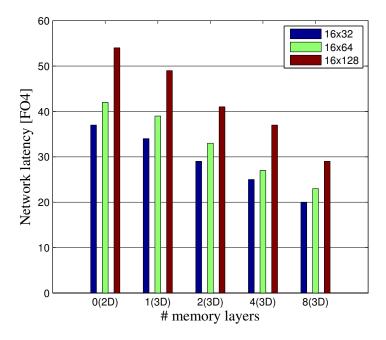

| 3.15 | Total dynamic power consumption of the network in the 3D system                             | 49 |

| 3.16 | System latency: Network delay plus memory access time.                                      | 50 |

| 3.17 | Network latency.                                                                            | 51 |

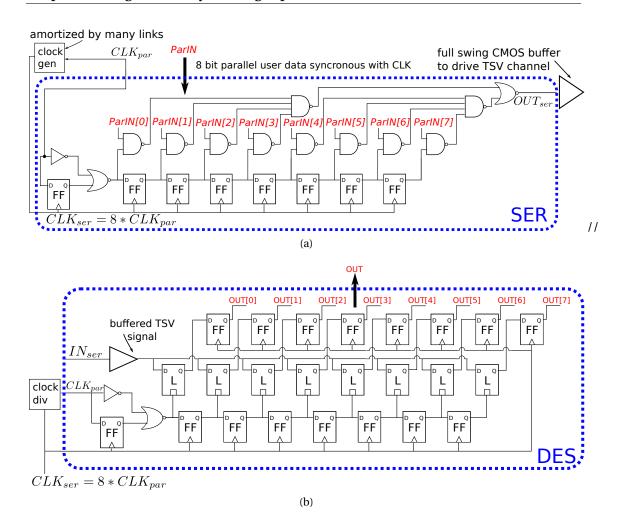

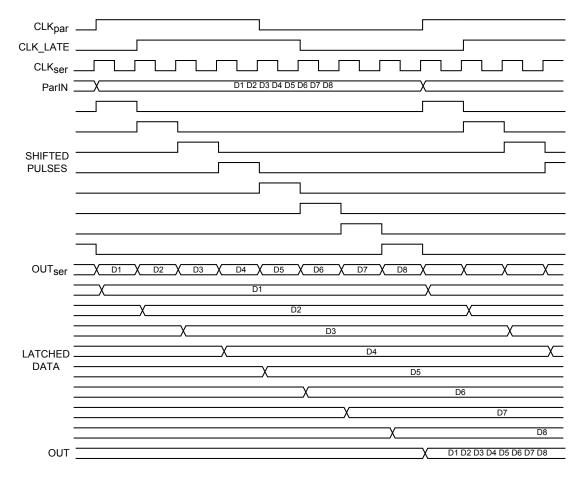

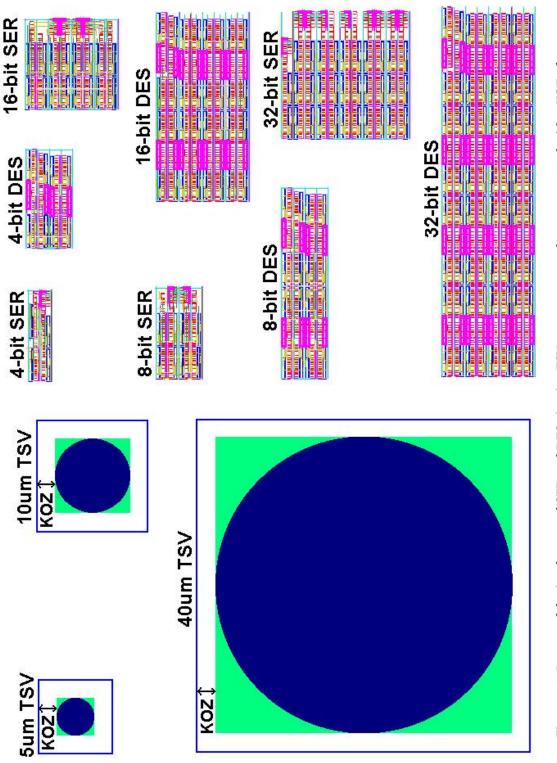

| 4.1  | (a) 1:8 SER circuit and (b) 1:8 DES circuit.                                                | 56 |

| 4.2  | Waveforms describing the SERDES functionality.                                              | 57 |

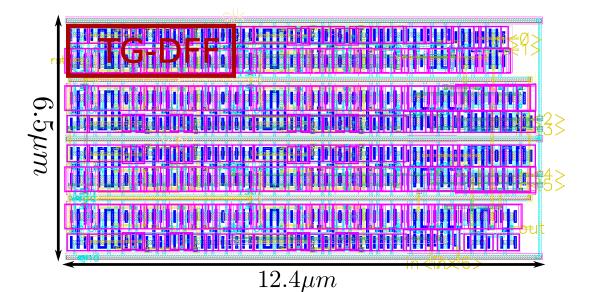

| 4.3  | Full custom layout view of the 8-bit SER in 40nm TSMC technology.                           | 58 |

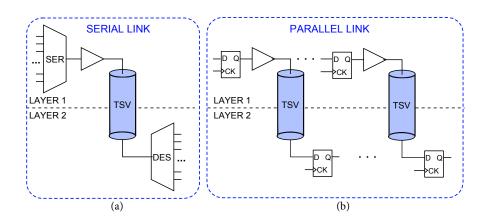

| 4.4  | (a) 3D serial link and (b) 3D parallel link scheme for a 2-layers stack                     | 59 |

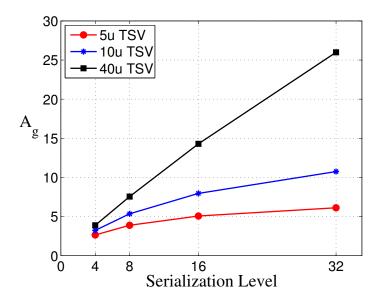

| 4.5  | $A_g$ of the 3D link for different serialization levels                                     | 60 |

| 4.6  | Layout of the implemented SER and DES circuits; TSVs are represented as a                   | 00 |

| 110  | square pad with a KOZ of $2.5\mu$ m                                                         | 61 |

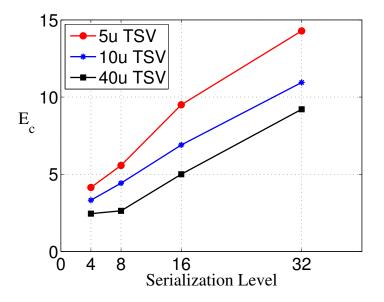

| 4.7  | Energy cost $E_c$ of the 3D link for different serialization levels for a 2-layers system.  |    |

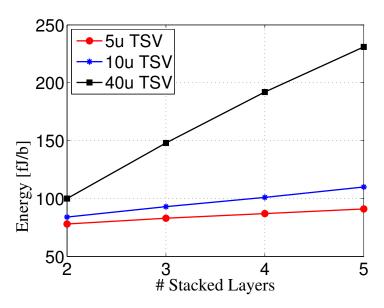

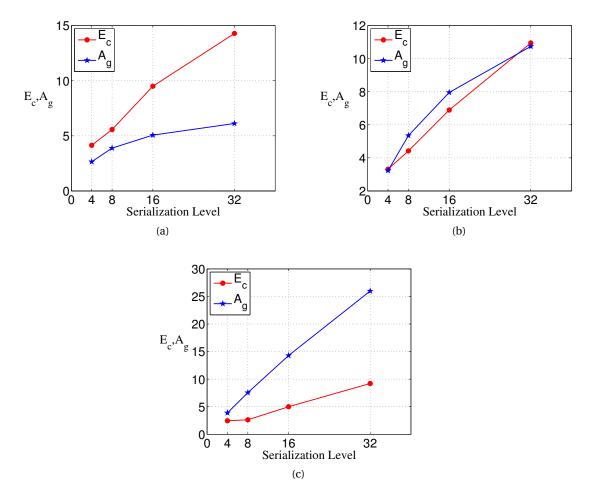

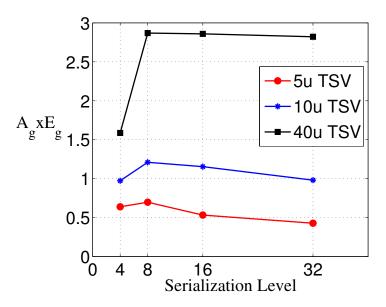

| 4.8  |                                                                                             | 63 |

|      | $A_g$ and $E_c$ for (a) 5 $\mu$ m TSVs (b) 10 $\mu$ m TSVs and (c) 40 $\mu$ m TSVs          | 64 |

|      | Area gain - energy gain product.                                                            | 65 |

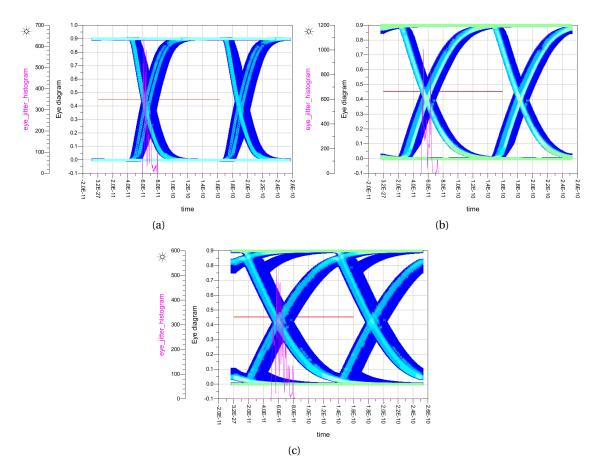

|      | Eye diagram and jitter histogram for the serializer driving a (a) $5\mu$ m (b) $10\mu$ m    |    |

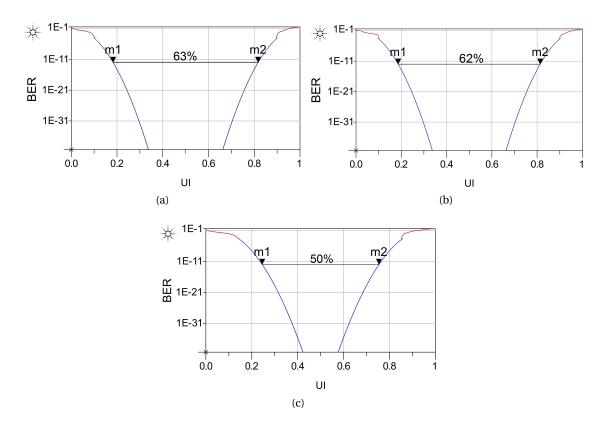

|      | and (c) $40\mu$ m TSV channel.                                                              | 66 |

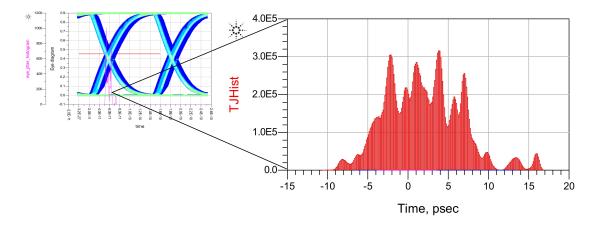

| 4.12 | Histogram of the total jitter for the serializer driving a $10\mu$ m TSV channel            | 67 |

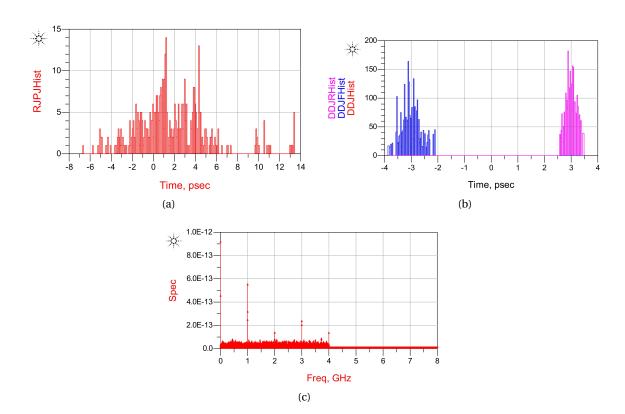

|      | (a) Histogram of the random and periodic jitter, (c) histogram of the data depen-           |    |

|      | dent jitter, (b) BER for the serializer driving a $10\mu$ m TSV channel.                    | 68 |

| 4.14 | BER for the serializer driving a (a) $5\mu$ m, (b) $10\mu$ m and (c) $40\mu$ m TSV channel. | 69 |

|      | Clock distribution scheme for the 10GB/s system                                             | 70 |

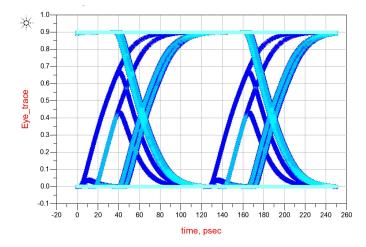

|      | Simulated eye diagram for one of the TSV channel in the system                              | 71 |

|      | Full custom layout views of the 8-bit double data rate (a)serializer and (b) deseri-        |    |

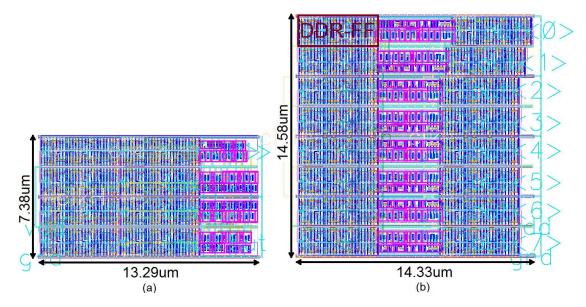

|      | alizer in 40nm TSMC technology.                                                             | 72 |

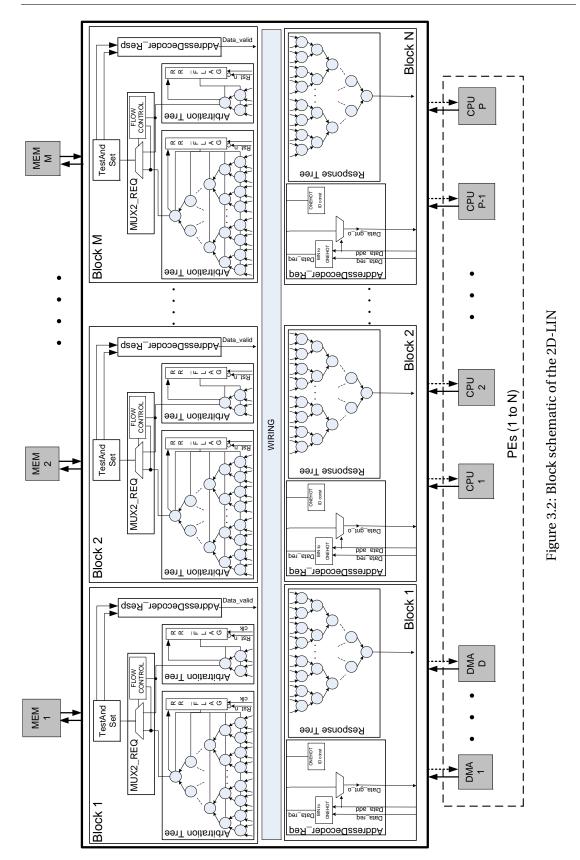

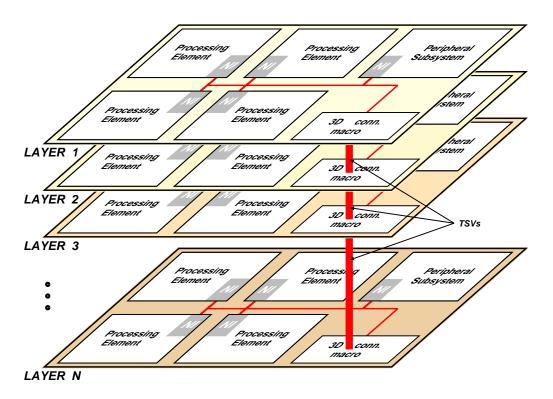

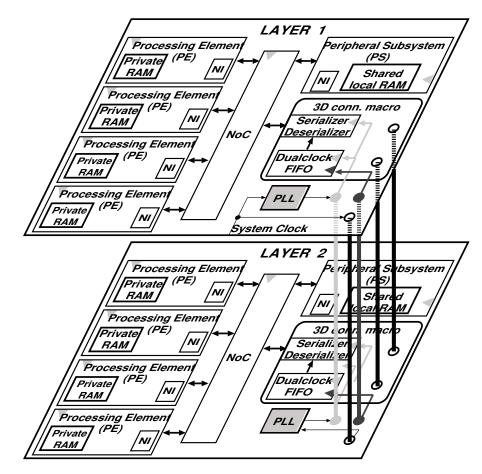

| 5.1 | Block diagram of the 3D-MMC architecture. The generic 3D connection macro<br>block on each identical layer allows the inter-layer communication among mul-                                                                                                                                                                                                                           |    |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | tiple layers, with serial multiplexed TSV arrays.                                                                                                                                                                                                                                                                                                                                    | 78 |

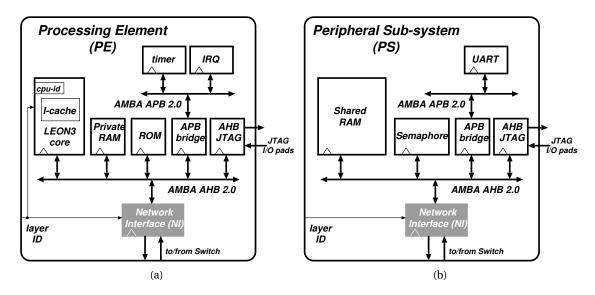

| 5.2 | (a) Processing element (PE) internal architecture, with the LEON3 core and                                                                                                                                                                                                                                                                                                           |    |

|     | its private modules. Each unit is accessible through JTAG ports for debugging                                                                                                                                                                                                                                                                                                        |    |

|     | purposes. The network interface (NI) routes packets from PE to the shared                                                                                                                                                                                                                                                                                                            |    |

|     | memories in the (b) Peripheral Subsystems (PS).                                                                                                                                                                                                                                                                                                                                      | 78 |

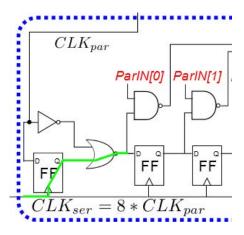

| 5.3 | Critical path of the serializer circuit.                                                                                                                                                                                                                                                                                                                                             | 80 |

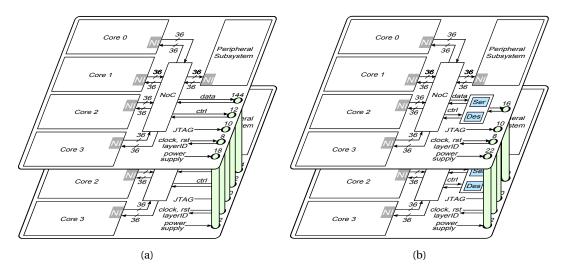

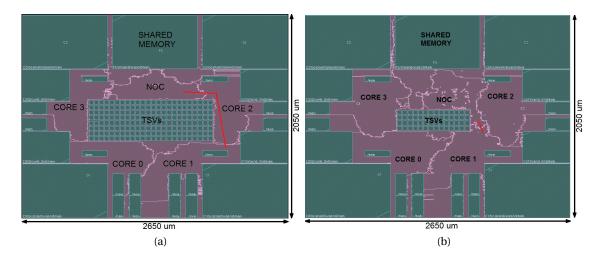

| 5.4 | View of the 3D-MMC (a) parallel and (b) serial configurations.                                                                                                                                                                                                                                                                                                                       | 81 |

| 5.5 | View of the 3D-MMC (a) parallel and (b) serial configurations design with $40 \mu m$ TSV channels. The red line depicts a path from CORE1 to the NoC                                                                                                                                                                                                                                 | 81 |

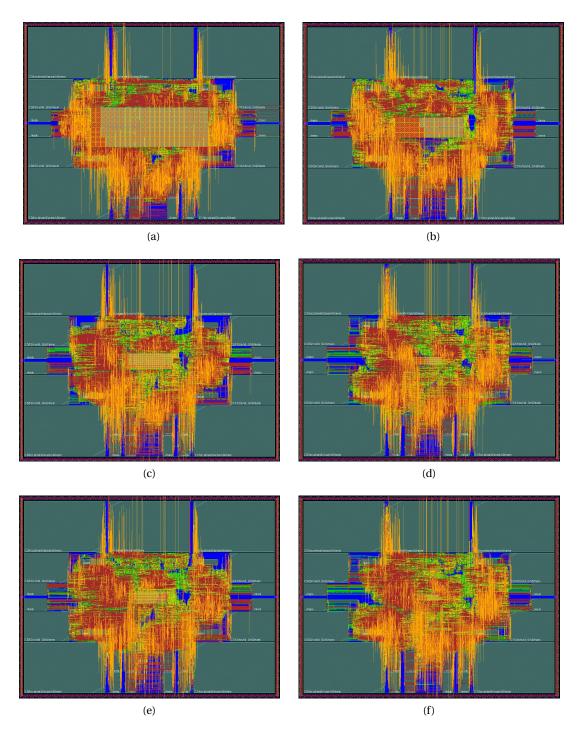

| 5.6 | Layouts of the 3D-MMC design with (a) a parallel vertical bus and (b) with serialization through $40\mu m$ TSV channels. Layouts of the 3D-MMC design with (c) a parallel vertical bus and (d) with serialization through $10\mu m$ TSV channels. Layouts of the 3D-MMC design with (e) a parallel vertical bus and (f) with serialization through $5\mu m$ TSV channels.            | 82 |

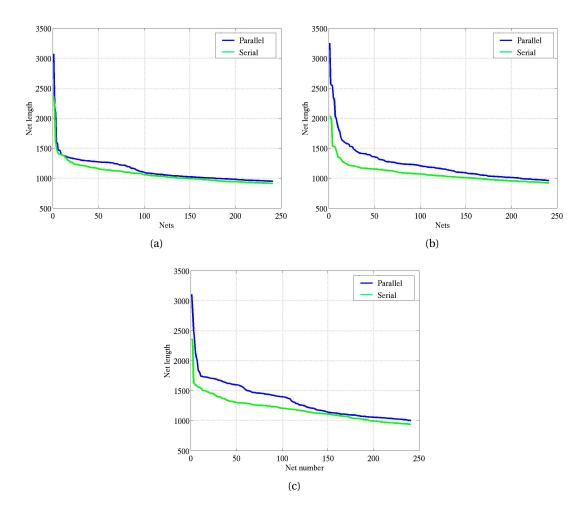

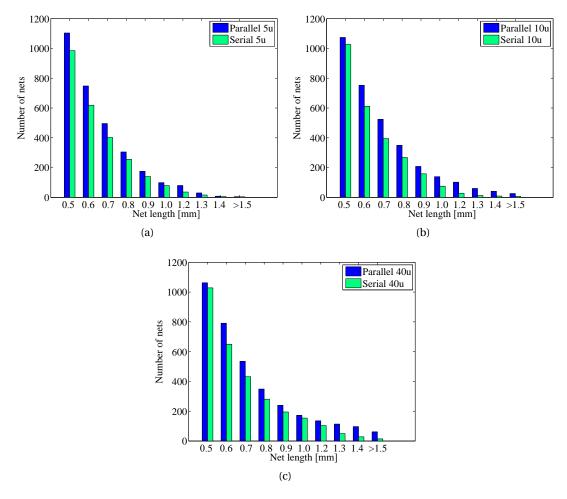

| 5.7 | Length trend of the longest 240 nets in the design for (a) $5\mu m$ (b) $10\mu m$ (c) $40\mu m$                                                                                                                                                                                                                                                                                      |    |

|     | TSVs for the parallel (blue) and serial (green) configuration.                                                                                                                                                                                                                                                                                                                       | 84 |

| 5.8 | Net statistics.                                                                                                                                                                                                                                                                                                                                                                      | 85 |

| 6.1 | Proposed architecture for the 3D-CMP in a 2-layer configuration: Four identical<br>Processing Elements (PE) and a Peripheral Subsystem (PS) are placed in each<br>layer. A 3D connection macro with TSVs is responsible of inter-layer communi-<br>cation. Note that only main building blocks and relevant TSVs are shown in the<br>diagram, the data TSVs are omitted for clarity. | 89 |

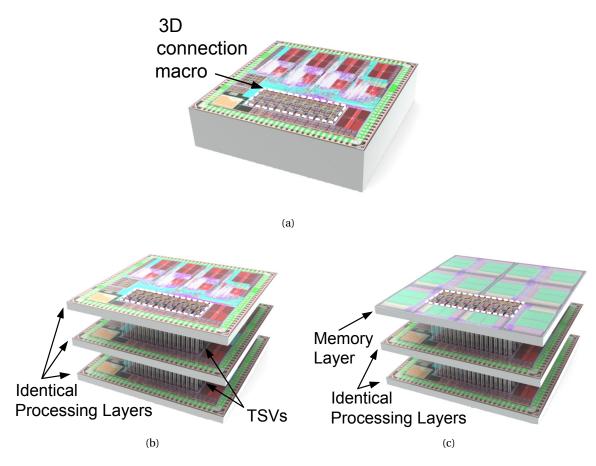

| 6.2 | Modular re-usability of 3D MMC: (a) Single die used as stand-alone 2D-CMP.<br>(b) Homogeneous stacking for high performance 3D-CMP (c) Heterogeneous<br>stacking for 3D-CMP, integrating additional layers (e.g. a memory die) that shares<br>the same 3D connection macro.                                                                                                          | 01 |

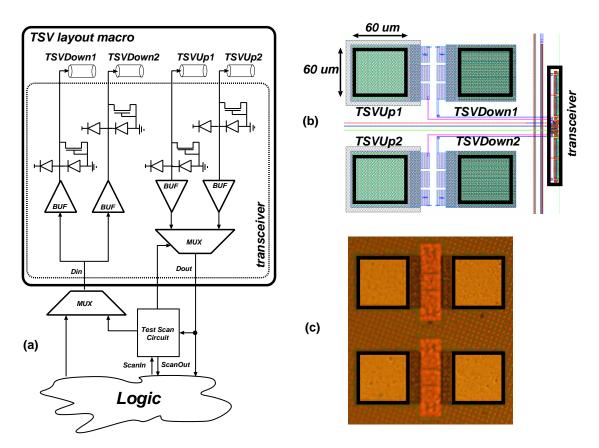

| 6.3 | (a) Circuit schematic of the TSV macro. (b) Layout of the TSV macro, highlighting the main blocks from the corresponding circuit schematic. The effective TSV pad area is put in evidence. (c) Optical microscope image of the TSV macro on                                                                                                                                          | 91 |

|     | the fabricated test vehicle.                                                                                                                                                                                                                                                                                                                                                         | 92 |

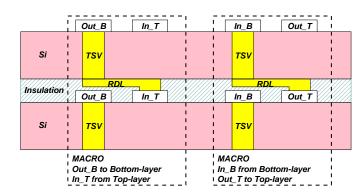

| 6.4 | TSV macro cross-section, highlighting the use of multiple pads and redistribu-<br>tion layer (RDL).                                                                                                                                                                                                                                                                                  | 93 |

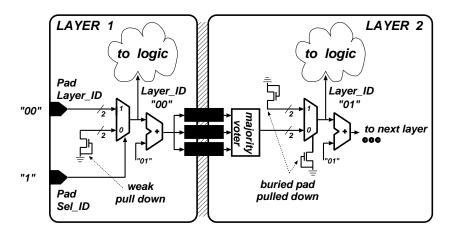

| 6.5 | LayerID generation and propagation between two stacked layers using three redundant TSVs for the signal interface. Schematic of the configured circuit in                                                                                                                                                                                                                            |    |

|     | each layer is shown, unrelated logic is not depicted.                                                                                                                                                                                                                                                                                                                                | 94 |

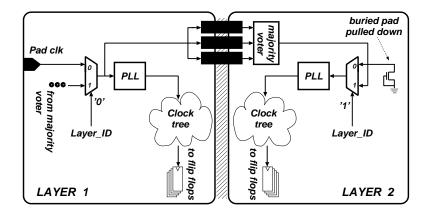

| 6.6 | Clock distribution and propagation between two stacked layers using three                                                                                                                                                                                                                                                                                                            |    |

|     | redundant TSVs for the signal interface. Schematic of the circuit configured                                                                                                                                                                                                                                                                                                         |    |

|     | through the LayerID is shown, unrelated logic is not depicted.                                                                                                                                                                                                                                                                                                                       | 95 |

|     |                                                                                                                                                                                                                                                                                                                                                                                      |    |

### List of Figures

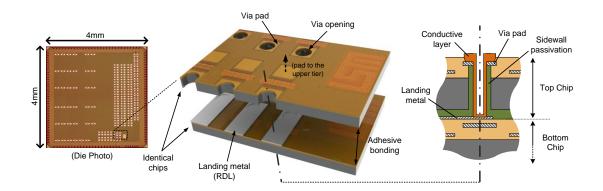

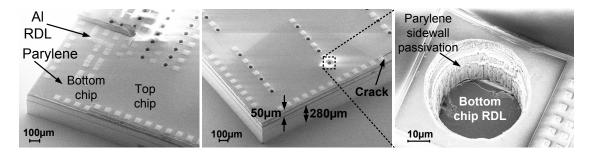

| 6.7  | Die photo of the multi-processor chip, and the illustration of the chip stacking approach with 40 $\mu$ m diamater TSVs fabricated on 60 x 60 $\mu$ m <sup>2</sup> CMOS pads. Since the two chips are identical, the surface of the bottom chip is passivated and RDL is patterned to re-route the signal to the upper tier.       | 97  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

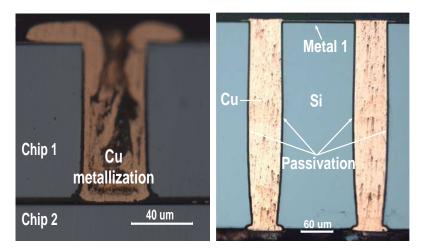

| 6.8  | SEM photos of the bonded chips and the close-up image of the via opening showing the sidewall parylene passivation and the RDL layer on the bottom chip. (An already broken chip is used as the top chip to inspect the alignment accuracy).                                                                                       | 97  |

| 6.9  | Cross section of the in-house developed TSVs: (a) Lined TSV connecting two stacked chips. (b) Fully-filled TSV developed for the characterization tests                                                                                                                                                                            | 98  |

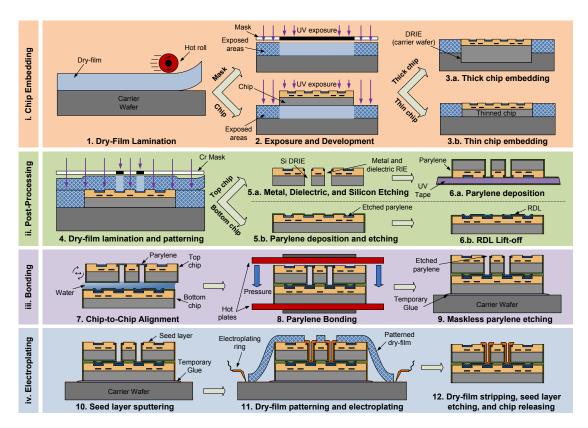

| 6.10 | Process flow for post-CMOS processing and chip-to-chip integration [23]                                                                                                                                                                                                                                                            | 99  |

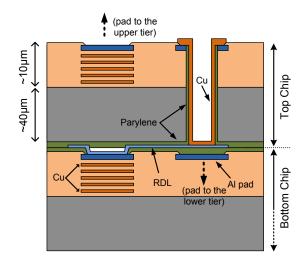

| 6.11 | Illustration of the TSV macro, showing the parylene sidewall passivation and Cu metallization connecting RDL to the Al pad on the top chip (not drawn to scale). Each TSV macro is composed of two adjacent pads; one for routing the signal to the upper tier through the RDL, the other for the lower tier through the TSV [23]. | 99  |

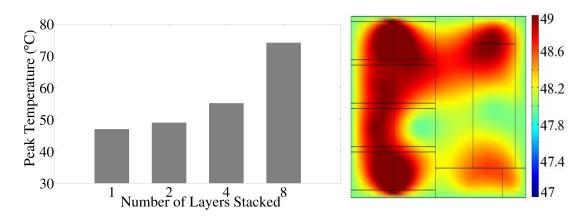

| 6.12 | The figure demonstrates the peak temperatures at steady state for a single layer as well as 2, 4, and 8-layered stack. On the right, we show the thermal map of the top layer for the 2-layered stack. Thermal variations are similarly low (limited to a few degrees only) for 4 and 8-layered stacks.                            | 101 |

| 6.13 | Single die microphotograph. Pads for signal and power TSVs are visible before the post-processing. Main blocks are identified in the image (PE, PS, Switch of the NoC, PLL). Size of the full-chip and of the PE footprint are also shown                                                                                          | 103 |

| 6.14 | Block diagram of the multiplexers interface between two stacked layers. The represented circuit is in charge of the scan-chain configurability allowing pre-<br>and post-bonding testability.                                                                                                                                      | 104 |

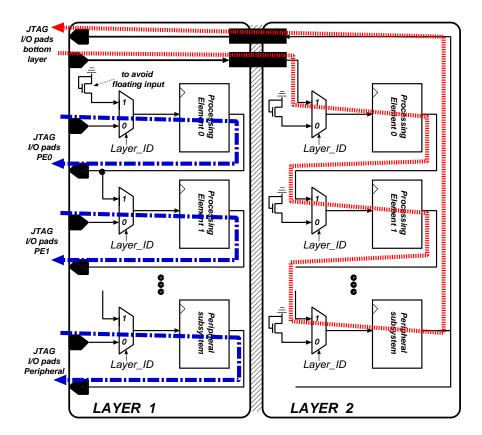

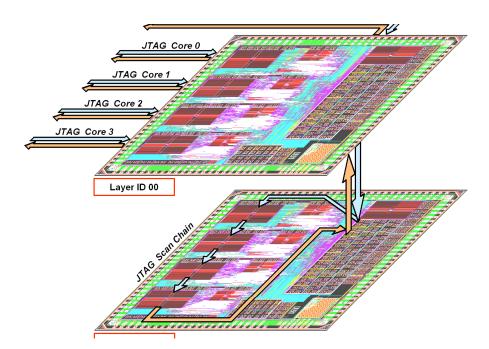

| 6.15 | Auto-configuration for testability. Top layer cores are accessed in parallel from the pads. The processors on bottom layer are configured in a scan chain for the debug procedure: JTAG inputs are transmitted from top to bottom die, the TDO produced on the bottom layer returns up to the top one.                             | 105 |

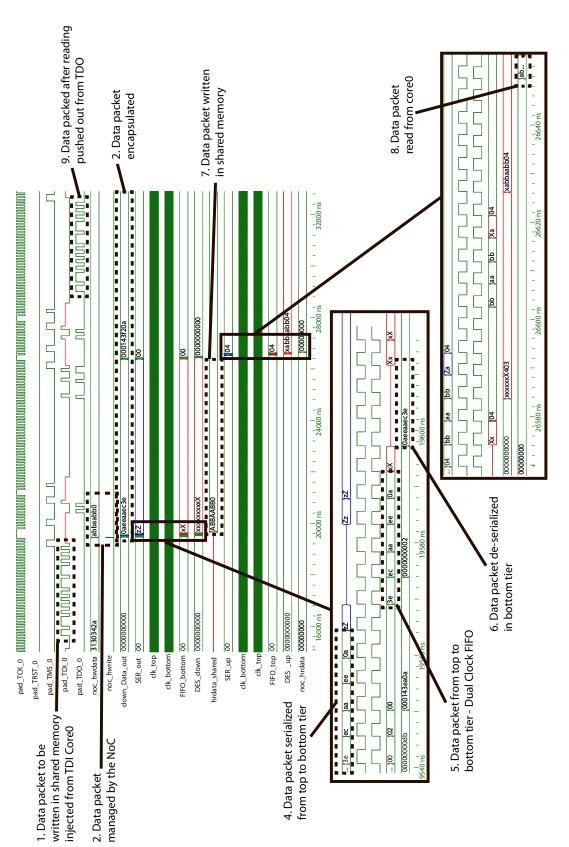

| 6.16 | Post-layout simulation waveforms describing a inter-layer operation: One core is requesting to write a word on the shared memory of the bottom tier, via JTAG.                                                                                                                                                                     | 106 |

| 6.17 | SEM image of the multi-core die with post-processed TSV openings                                                                                                                                                                                                                                                                   | 108 |

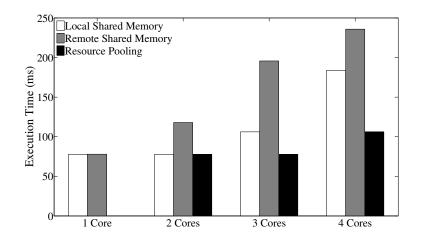

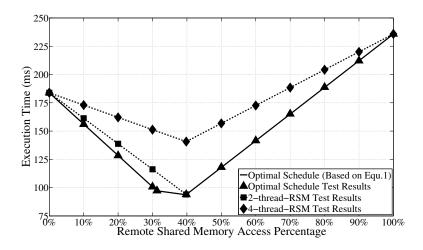

| 6.18 | Comparison of execution time of the memory intensive benchmark when all cores access local memory, all cores access remote memory, and when memory resource pooling is applied.                                                                                                                                                    | 109 |

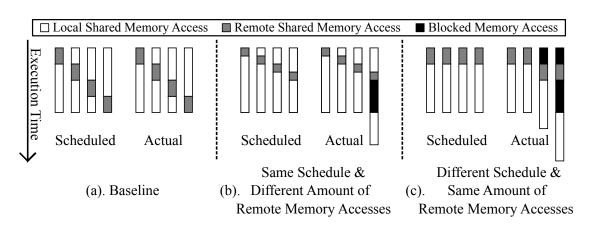

| 6.19 | Performance under different workload allocation and scheduling combinations.<br>(a) serves as the baseline, (b) has the same schedule as the baseline but fewer<br>remote memory accesses, while (c) has the same number of remote memory                                                                                          |     |

|      | accesses but has a different schedule.                                                                                                                                                                                                                                                                                             | 110 |

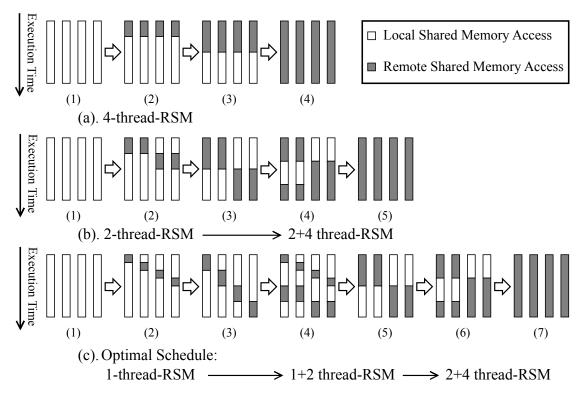

| 6.20 | Workload schedules for task level resource pooling. (a). 4 threads accessing           |     |

|------|----------------------------------------------------------------------------------------|-----|

|      | remote shared memory at the same time-4- <i>thread-RSM</i> ; (b). (1)-(3): 2 threads   |     |

|      | accessing remote shared memory at the same time– <i>2-thread-RSM</i> ; (c). (1)-(3): 1 |     |

|      | thread accessing remote shared memory– <i>1-thread-RSM</i>                             | 111 |

| 6.21 | Test results of different memory resource pooling schedules and the optimal            |     |

|      | schedule's curve based on Eqn.1.                                                       | 112 |

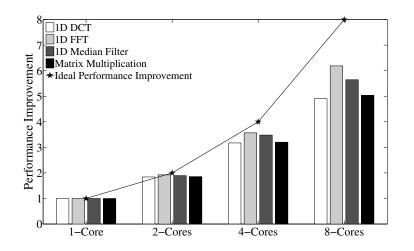

| 6.22 | Performance improvement compared to single core                                        | 113 |

# List of Tables

| 2.1 | ITRS roadmap 2011 [2]                                                       | 16  |

|-----|-----------------------------------------------------------------------------|-----|

| 2.2 | Fabricated TSV details                                                      | 18  |

| 2.3 | Process variations                                                          | 22  |

| 3.1 | Network main parameters.                                                    | 36  |

| 3.2 | 3D-LIN vs. 2D-LIN                                                           | 41  |

| 3.3 | Latency improvement                                                         | 50  |

| 4.1 | SERDES state of the art                                                     | 55  |

| 4.2 | SERDES area                                                                 | 58  |

| 4.3 | TSV parasitics for different geometries                                     | 59  |

| 4.4 | Energy efficiency at 8Gb/s per channel for a 2-layers 3D stack.             | 63  |

| 4.5 | Eye diagram measurements.                                                   | 67  |

| 4.6 | Energy efficiency of the system composed by 10 8bit SERDES TSV links for a  |     |

|     | 2-layers 3D stack delivering a total aggregate bandwidth of 10GB/s.         | 71  |

| 4.7 | Eye diagram measurements.                                                   | 71  |

| 4.8 | Energy efficiency at 8Gb/s per channel for a 2-layers 3D stack.             | 72  |

| 4.9 | Energy efficiency of the system composed by 10 8-bit SERDES TSV links for a |     |

|     | 2-layers 3D stack delivering a total aggregate bandwidth of 10GB/s.         | 73  |

| 5.1 | SERDES characteristics.                                                     | 80  |

| 5.2 | Physical design parameters.                                                 | 83  |

| 5.3 | Routing results.                                                            | 86  |

| 6.1 | TSVs features summary                                                       | 94  |

| 6.2 | Power Consumption and Thermal Properties of 3D-MMC                          | 100 |

| 6.3 | Summary of the tested functionalities                                       | 102 |

| 6.4 | Architecture details of 3D test vehicle                                     | 103 |

| 6.5 | Execution Time of Different Shared Memory Access Scenarios When All 8 Cores |     |

|     | are Active.                                                                 | 114 |

### **1** Introduction

Since 1965, with the postulation of Moore's law [1], the integration density has been increasing continuously thanks to the aggressive scaling of process technology. At the same time, the performance gains enabled by scaling have been gradually challenged by on-chip interconnects. As the request for increased performance and computing power rise, hundreds of millions of transistors are placed on a single chip occupying more and more area, but the realization of large dies impacts the global interconnects length, as well as reliability and manufacturing yield. At the same time, as feature size decreases, the cross section of the metal wires also shrinks.

Despite the advent of low-resistivity materials for the on-chip wires, the decrease of their cross-section area, *A*, due to scaling and the increased wirelength, *l*, are causing a rise in the

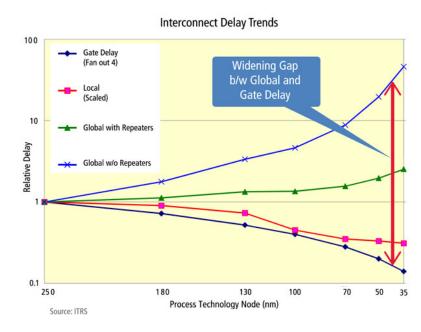

Figure 1.1: Delay of Metal 1 and global wiring vs. technology node [2].

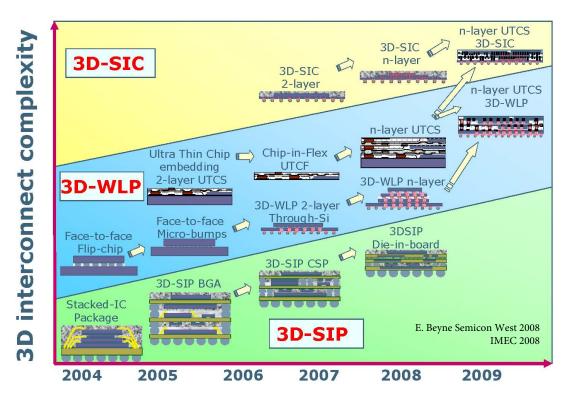

Figure 1.2: 3D interconnect roadmap by IMEC.

resistance  $R = \rho \frac{1}{A}$ . In addition, as the aggregated interconnect length increases since more wires are being used in each layer and more metallization layers are being added, their delay  $t = \frac{1}{2}RCl^2$  becomes dominant over the gate delay. Figure 1.1 depicts the delay of local and global wiring in future generations. The length of local wires usually shrinks with traditional scaling, hence the impact of the lower metal layers delay on performance is minimal. On the other hand, global interconnects are impacted the most by the degraded delay. Even though the insertion of repeaters can improve the delay in global wiring, this approach causes a significant increase in power consumption as well as the need for increased chip area. Furthermore, interconnect delay is just a part of the problem: as the clock frequencies continue to climb, any increase in interconnect loading significantly increases the power consumption of the ICs.

This dissertation focuses on the advantages of 3D stacking applied to microprocessors and related integrated microprocessor systems where more than 30% of the power can be consumed in backend interconnect wire [3]. In general, microprocessors are driving towards lower power consumption, increased performance, reduced form factor and increased integration. With 3D integration, multiple strata of different types can be stacked with a high bandwidth, low latency and low power interface. Additionally, wire reduction using 3D provides new microarchitecture opportunities to trade off performance, power and area.

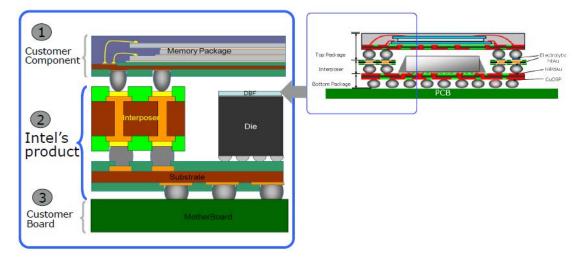

Figure 1.4: Intel Co-PoP technology.

### 1.1 From 2D to 3D ICs

During the last years several options have been studied as promising solutions for overcoming the interconnect bottleneck and continue the "More-than-Moore" trend [4]. An overview of the evolution of the interconnect and packing solutions studied by IMEC is shown in Figure 1.2.

### 1.1.1 System in package

A first step was taken with the advent of the *System-in-Package (SiP)* assemblies, which can be defined as an assembly of naked or packaged dies mounted on the same main package either in a 2D or a 3D manner. Integrating all the critical components within a package rather than on a *Printed Circuit Board (PCB)* significantly contributes to system miniaturization and communication bandwidth. Additionally, another advantage of the SiP is that each die can be implemented using the most appropriate technology process.

### **Chapter 1. Introduction**

For 2D SiP, the dies are connected through the metal interconnects on the SiP substrate. In case of 3D SiP, the interconnections through the z-axis can be implemented in different ways, such as wire bonding, vertical interconnects along the periphery, or long and wide, low density vertical interconnects.

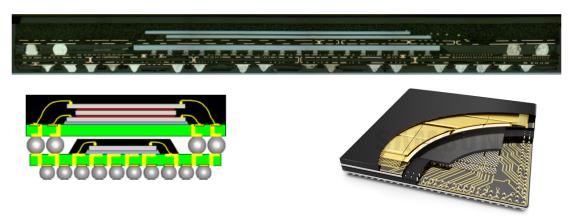

In the case of a SiP mounted on another SiP, the system is referred to as a *Package-on-Package* (*PoP*). Samsung devices, such as Samsung's Exynos 4210, already exploit PoP technique in order to integrate a logic layer at the bottom with memory layers at the top, as in Figure 1.3. Each die can be selected, tested independently and then assembled. This approach offers significant benefits, such as reduced physical size, high-density I/Os and high heat dissipation.

Also Intel has officially disclosed his Co-PoP solution, shown in Figure 1.4, at the Intel Developer Forum of 2012. Intel supplies bottom package, while customers can select the desired memory to be placed on top. A product already using this approach is the Atom Z2460.

### 1.1.2 2.5D IC

A further step towards a more compact integration was enabled by the usage of a silicon interposer. A Si-interposer is a double sided die with no active devices that is used to connect the active dies among each other, while the metallization layers on the top and bottom faces are connected with *Through Silicon Vias(TSVs)*. 2.5D ICs can be defined as an assembly of dies placed on a silicon interposer.

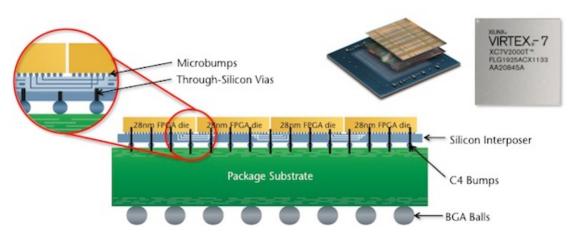

A successful product exploiting this technology was put on the market by Xilinx in 2011. The Virtex7 2000T is still the world's highest density FPGA, delivering greater than 2X the capacity and bandwidth offered by the largest monolithic devices [5]. A simplified cross-section of the Virtex-7 2000T FPGA is depicted in Figure 1.5: 4 FPGA are flip-chip bonded to the Si-interposer integrating 2 million logic cells, 6.8 billion transistors and 12.5 Gb/s serial transceivers on a single device. The system is optimized to reduce power dissipation, for noise isolation and to achieve high yield.

### 1.1.3 3D IC

Although 2.5D integration gained popularity because of the and its technological feasibility, it might still not be sufficiently effective for several high performance applications. With 3D integration, multiple dies can be directly stacked in top of each other and interconnected through TSVs so that they function as a single device. 3D ICs have the potential to provide significant advantages over traditional planar circuits without the need of any interposer.

Figure 1.5: Virtex-7 2000T FPGA from Xilinx.

### **3D opportunities**

The motivations driving the extensive research on 3D ICs are basically three: form factor, performances and heterogeneous integration. Folding a chip into a 3D configuration drastically improves the **form factor** since the same number of transistors can be integrated within a smaller area with respect to a 2D implementation. As a consequence of the higher packing density, the average interconnect length improves [6], which directly translates into a reduction of the RC delay boosting the system **performance**. Reducing the interconnect length also lowers the number of repeaters along the lines, hence the power dissipated to ensure signal integrity and propagation.

While traditional 2D *System-on-Chip(SoC)* struggles to reach the bandwidth demand of next generation computing device due to pad number limitation, the low parasitic, high vertical connect density provided by TSVs can potentially provide TB/s **data bandwidth**. Hence 3D technology has the potential to replace traditional off-chip signalling technology, in particular improving memory communication bandwidth.

The possibility of integrating **heterogeneous technologies** in the same system is also a main advantage of 3D ICs. For instance, DRAM and processors can be integrated in the same system helping to overcome the memory to processor performance bottleneck that plagues 2D ICs. Also the possibility of fabricating analog and digital circuits separately with different technologies and then stacking them is an interesting opportunity to optimize the functionality of each block and avoid problems related to noise.

### **3D challenges**

The benefits offered by the third dimension still have to be unlocked by overcoming several challenges, starting from design methodologies at the front-end until the mature manufacturing processes at the back-end.

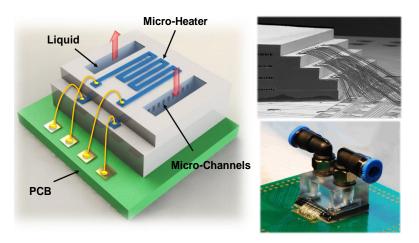

Figure 1.6: Micro-channel based liquid cooling test vehicle from a collaboration between EPFL and IBM, courtesy of LSM.

- **Manufacturing technology** Since TSV fabrication technologies are not yet mature, reliability is expected to be a limiting factor for 3D IC performance and yield [7]. For instance, unsuccessful wafer alignment during the bonding process and handling of very thin silicon wafers are the primary mechanisms of TSV failure, with a minimum TSV diameter of 1.2  $\mu m$  reported in the open literature [8]. The characteristics of the vertical interconnects are fundamental to enhance the performance enough to compensate the cost of this new technology.

- **CAD tools** Although it is possible to design 3D ICs with the available *Computer Aided Design(CAD)* tools by ad-hoc techniques which mostly consist of a divide-and-conquer approach. The design of a 3D IC is a challenging and risky task due to the lack of industry-standard CAD tools to automate the process. The CAD community is required to develop automated solutions for partitioning, floorplanning, placement and routing of 3D designs. Lately, leading companies in the CAD domain, such as Cadence [9] and Synopsys [10] have started proposing the first solutions for 3D IC development.

- **Power density** Even though the system power consumption is expected decrease, the high packing density and the lack of heat conduction paths will translate in a great increase of the power density. The thermal dissipation of the tiers far from the heat sink is expected to be a major concern, especially for power consuming applications. Several options have been studied to mitigate the effect of vertical integration, such as liquid cooling using micro-channels [11] [12] shown in Figure 1.6, thermal vias [13] [14] [15] or, in case of multi-processor systems, software solutions like scheduling algorithms performing thermal-aware task migration [16].

- **Testing** The testing strategy required by 3D stacked system is significantly more complicated than the traditional testing methodology for 2D ICs. Ideally, each die, or system, should be tested functional at each step. First, a pre-bonding test should identify *Known Good Dies(KGD)*. Then, after stacking each layer, a mid-bond test of the system should

be performed to guarantee that the system is still working before stacking another layer. Finally, the post-bond test should identify the functional system. Depending on the design, it may be extremely challenging to test all the layers before the bonding process. For Example some of the dies may not have real signal pads since their *Input/Output(I/O)* signals are transmitted through TSVs. Missing testing steps can cause a noticeable decrease of the final yield. R&D groups have, and still are, dedicating a lot of effort to find testing solutions and several design-dependent solutions have been proposed, however, the definition of a testing policy for 3D ICs is still in progress.

#### **3D architectures**

Depending on the type of layers stacked, the 3D system can be categorized within one of the following topologies.

• **Memory on Logic** generically includes stacking cache, main memory or strata with similar functions onto a logic device and has been one of the most studied architectural choice for 3D ICs. Some of the advantages of increasing the on-die cache capacity by stacking are increased performance by capturing larger working sets, reduction of off-die band-width requirements by accessing more data on die instead of externally, and reduction of system power by reducing bus activity through fewer main memory accesses.

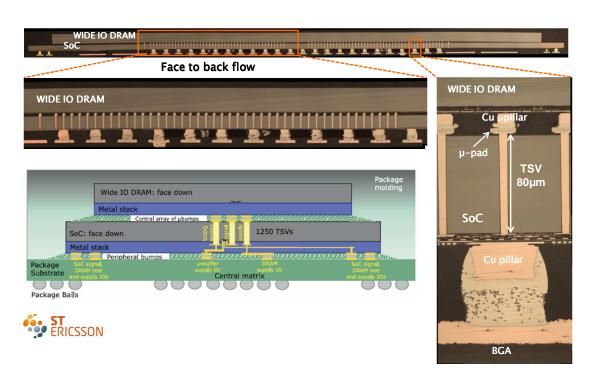

In December 2011, JEDEC Solid State Technology Association announced a new standard for Wide I/O mobile DRAM which uses chip-level 3D stacking with TSV interconnects and memory chip directly stacked upon a *System on Chip(SoC)*. The Wide I/O standard was released in order to meet the industry demands for increased level of integration, as well as improved bandwidth, latency, power and form-factor [17].

Based on the JEDEC standard, the *WideIO Memory Interface Next Generation (WIOM-ING)* was presented in 2013. The 3D system, shown in Figure 1.7, was developed from the cooperation among ST-Microelectronics for SoC wafers manufacturing and assembly, CEA-Leti for middle end process steps and ST-Ericsson for electrical test and project management. The stacked dies are connected by TSVs with a diameter of  $10\mu$  and a pitch of  $40\mu$ , drilled in the SoC die.

At the end of 2013, also Samsung moved from PoP to TSV based 3D technology by presenting its Widcon technology. The structure, depicted in Figure 1.8, brings better energy efficiency and higher bandwidth, up to 17GB/s.

Again Samsung, as part of a consortium with leading companies like Micron and IBM, released the DRAM Hybrid Memory Cube (HMC)in 2013. The goal is to break the memory wall by removing the logic transistors from each DRAM die and then stack them on top of a small logic die, which takes care of buffering and routing from/to the memory banks. This centralized logic driving a stack of 8 memory dies allows for higher and more efficient data rates, up to 320GBps, while consuming 70% less energy than DDR.

Figure 1.7: WIOMING chip from ST-Ericson, ST-Microelectronics and CEA-Leti.

Figure 1.8: Widcon technology from Samsung.

Figure 1.9: 2.5D+3D IC. Courtesy of Hsien-Hsin Lee.

• Logic on Logic A different approach is called logic-on-logic stacking and involves splitting a logic area between two or more strata. In particular, partitioning a microprocessor into multiple layers to reduce interconnect length. Block level partitioning is the simplest and most effective solution to rearrange a design onto multiple layers. Since the performance improvements linked to the 3D arrangement are directly dependent on the inter-strata via pitch and size, the via density limits the granularity at which a system can be divided. Block level of logic-on-logic stacking enables blocks to be moved closer in proximity, thus reducing the inter-block latency and power. The potentiality of this approach was explored by Morrow et al. [3] by splitting an Intel Pentium 4 family processor into two layers. Focusing on the layout arrangement of known performance sensitive pipelines several pipestages can be removed, eventually resulting in removal of approximately 25% of all pipestages. A 15% performance improvement from reduction of instruction execution latency and a 50% footprint reduction were demonstrated.

A further optimization can be envisaged by exploiting both the benefit of 3D integration and the interposer technology. This approach can be defined as 2.5 + 3D and is depicted in Figure 1.9. The Si-interposer can be used in order to integrate multiple 3D stacked system and 2D ICs. This approach is promising since it combines the extreme integration density and bandwidth offered by the 3D stacking technology with the ones of the 2.5D solution, such as better thermal management.

### 1.2 Objectives and contributions

3D-ICs can offer superior performance improvements over 2D equivalent. Nonetheless there are still several issues related to 3D design that need to be addressed before this technology can be widely adopted from the IC industry. This thesis work focuses on the two major TSV-related

challenges that can limit the benefits offered by 3D stacking technology: TSV area and delay overhead. According to the ITRS roadmap [2], TSV diameter will drop below the  $\mu$ m scale, remaining confined to 2-4  $\mu$ m for 3D-SoC. A TSV occupies a huge amount of silicon area compared to metal via in sub-micron technologies, which can turn into a reduction of the wirelength benefit of 3D-ICs. TSV parasitic capacitance is small compared to long on-chip interconnects. However, whenever a design is simply partitioned and folded in 3D without further optimizations, just a part of the intra-layer signals experience a real length reduction, while the rest may cope with a delay overhead compared to the 2D implementation. The eventual delay overhead on the 3D signal paths should be compensated by the insertion of buffers. Nevertheless, the additional silicon area required for buffer insertion and the related power overhead would be the price to pay. The TSV capacitance is dependent not only on the TSV diameter and height, but also on parameters related to the fabrication process, such as the oxide thickness and the doping concentration of the substrate. Hence smaller TSVs do not necessarily have smaller capacitance.

The aim of this thesis is to find design solutions that leverage the high bandwidth provided by TSV links minimizing the cost in terms of silicon area and capacitance load in order to meet the design requirements. Depending on the target application, different interconnection topologies have been explored and several solutions have been envisaged in this thesis.

First, a configurable network architecture exploiting a fully parallel TSV bus is presented. The architecture of the 3D interconnect has been optimized to be integrated in a 3D stacked *Chip Multi Processor(CMP)* featuring a shared L1 memory which provide a convenient shared memory abstraction while avoiding cache coherence overheads. The performance of the tightly-coupled processor cluster critically depends on the architecture of the interconnect between the processors and the memory banks, which should provides ultra-fast access to the largest possible L1 working set. The proposed 3D network guarantees single-cycle communication . The 3D implementation and the reconfigurability of the proposed network expand the storage capability of the system while still guaranteeing single cycle memory access time. The exploration of the trade-off between memory size and network latency for different partitioning choices demonstrates the potential of the proposed solution.

Using a TSV for each inter-layer signal may be extremely expensive in terms of silicon area for designs that require a high number of 3D connections. Moreover, since the TSV fabrication technologies are not yet mature, it may be required to implement hardware redundancy in order to improve yield [18], [19], while thermal TSVs have been already proposed to dissipate the internal heat of the 3D system [13] [14] [15]. In order to reduce the silicon area occupation exploiting the TSVs' excellent frequency properties, a high data-rate 3D serial link has been envisaged. Since 3D interconnects offer a reduced load compared to off-chip channels, high speed serial transmission through TSVs does not require complex and power-hungry equalization techniques, achieving high bandwidth with low silicon area and power. Low power *Serializer-Deserializer (SERDES)* circuits for inter chip 3D links have been designed and characterized for a variety of state-of-the-art TSV channels. The proposed serial 3D link has

no performance loss compared to a low frequency parallel 3D link. The effect of serialization on both area and energy for different TSV technologies has been analysed.

Once integrated in a complete system, the reduction in area demonstrated by the 3D serial solution also affects the chip routing. A TSV interferes with cell placement and, depending on the adopted technology, may become a routing obstacle. The reduction in the number of 3D vias obtained with the adoption of the serial vertical connection can relieve the routing congestion of the 3D system. In order to quantify the benefit of serialization on the routing of a 3D system, a *3D Modular Multi-Core (3D-MMC)* architecture has been designed and used as a test case. This innovative multi-processor platform is composed of completely identical stacked chips following a logic-on-logic stacking approach and creating an expandable 3D network of processing cores to improve performance. Analysis of the routing characteristic of the placed and routed layouts reveals an improvement in the average wirelength due to the serialization.

Finally, we present a test vehicle demonstrating the efficiency and applicability of a 3D serial link in a complete multi-processor system based on the 3D-MMC architecture. The prototype has been designed, fabricated using a UMC 90nm CMOS foundry process, tested, and the KGD has been vertically stacked using an in-house via-last TSV process. A comprehensive study of the system is presented together with a software approach to optimize the applications execution time. The system exhibits multiple Gbps vertical data bandwidth while limiting the number of TSVs. The experimental results obtained from simulations and measurements on the fabricated samples are provided.

### 1.3 Thesis organization

The remainder of this thesis is organized as follows.

- In Chapter 2, details of TSV fabrication technologies including the state-of-the-art TSV available from both foundries and research laboratories are presented. The analytical model of the TSV channel is then proposed and validated with measured in-house and literature data. This model will be fundamental to designing functional 3D circuits that meet the expected performance.

- Chapter 3 explores how to interconnect a Memory-on-Logic 3D stacked system. We propose a configurable 3D-Logarithmic Interconnection Network (3D-LIN) that exploits a parallel bus of small TSVs connecting multiple memory dies to a logic layer. The network is based on the 2D mesh-of-tree topology [20] and guarantees low-latency connection among multiple processing elements and a multi-banked memory.

- Chapter 4 investigates the possibility of producing high bandwidth, low delay inter-chip connection reducing the cost in silicon area due to the area footprint of the TSVs. An low power SerDes circuits for inter-chip 3D links is proposed. The area, performance

and energy efficiency of different serialization levels are explored for a variety of stateof-the-art TSV technologies and 3D systems.

- In Chapter 5 we explore the benefits of the proposed serial vertical interconnection on the routing congestion for a 3D chip multi-processor systems. To this end, a homogeneous multi-core architecture, 3D-MMC, has been designed. We first describe the architectural features of the 3D multiprocessor platform; then, we present a comparison between the routing characteristics of the parallel and the serial 3D communication solutions.

- In Chapter 6 we present a test vehicle based on the 3D-MMC architecture, MIRACLE. The test vehicle has been fabricated in 90nm UMC CMOS technology and stacked using an in-house TSV process. The results from a fabricated and tested test vehicle are presented.

- The conclusions of this thesis work are drawn in Chapter 7.

## **2** Through Silicon Vias Technology

With continued technology scaling, interconnect has emerged as the dominant source of circuit delay and power consumption. As discussed in Chapter 1, 3D stacking technology offers a promising architectural solution to overcome the on-chip interconnect bottleneck and integrate more functionality on the same chip. Since 3D architectures started gaining the attention of the IC community, several vertical communication topologies have been explored, e.g., TSV technology and contactless solutions like capacitive or inductive coupling.

In capacitive coupled signaling [21], the interplane communication is provided by small metal plates on different stacked silicon dies which create a capacitive channel. While the capacitor can be driven by a simple buffer, the receiving circuit requires more complex circuits. The received low voltage signal needs to be amplified to produce a full swing output. The advantage of capacitive coupling methods is the simple channel modelling and the low crosstalk due to a more confined electrical field. However, the communication distance is limited to several microns. In order to extend the communication range, the voltage across the capacitor should be increased, hence connecting more than two layers may reveal itself as a challenging task.

Wireless inductive coupling [22] methods rely on the coupled magnetic field between spiral inductors on the two stacked layers located at the same horizontal coordinates. The signal propagation is achieved through current pulses which generate magnetic flux inducing an electromagnetic induction in the receiving coil. With inductive coupling, the communication distance is not as constrained as for capacitive coupling, and signals can be propagated through more than two planes. However, the communication strength depends on the current in the transmitting coil and the coupling coefficient k between the coils, which is proportional to the coil size of the inductor. Hence, connecting more layers can be achieved either by consuming higher power consumption or by occupying a larger area.

Nonetheless, TSV-based 3D ICs have emerged as the most promising to achieve the desired vertical interconnect density. A TSV is a conductive connection between the two sides of a silicon waver or chip which can transmit a signal from a tier to another. The fabrication of 3D ICs involves three major processing steps: TSV fabrication, wafer/chip thinning and bonding.

Figure 2.1: (a) Capacitive coupling [21] and (b) Inductive inter-chip signaling [22] for 3D ICs.

The order of these steps may vary depending on the fabrication choices.

### 2.1 TSV fabrication technologies

TSVs can be categorized in different groups according to the process flow.

- Via First TSVs are fabricated before the Front-End-Of-Line (FEOL) CMOS processing;

- **Via Middle** TSVs are fabricated after the Si front-end (FEOL) device processing but before the *Back-End-Of-Line (BEOL)* interconnect process;

- Via Last TSVs are fabricated after the Back-End-Of-Line (BEOL) interconnect process.

In the case of via first TSVs, the advantage is that tiny and dense TSVs can be fabricated. However, the conductive material for the filling can just be polysilicon, since metal cannot withstand high temperatures and would not be compatible with the subsequent steps of the technological flow. The drawback of polysilicon vias is the higher resistivity compared to metal vias, which can be a major obstacle for certain applications. On the other hand, via last TSVs occupy more Si area, but can be filled with low resistive material. Moreover, choosing a via-last approach is extremely interesting since it allows the fabrication of the planar chip in a conventional foundry, then the stacking process can be performed separately. TSVs can be also discriminated depending on the order of TSV processing and 3D-bonding.

In terms of 3D-stacking process, there are 3 possibilities:

- **Die-to-Die (D2D)** bonding: complete wafers are stacked together before the the single 3D chip are sliced;

- **Die-to-Wafer (D2W)** bonding: a single die is stacked on top of another die integrated in a wafer;

Figure 2.2: Summary of the 3D integration scenarios based on the TSV type [23].

• Wafer-to-Wafer (W2W) bonding: single dies are stacked together.

W2W bonding is the simplest in terms of processing, however, integrating more layers leads to a yield loss due to stacking untested faulty dies. D2W bonding allows testing the individual dies before the assembly. D2D bonding is the most expensive solution in terms of fabrication, nevertheless, it is extremely interesting since the KGD from different foundries can be integrated in a 3D system allowing more freedom in the design. The bonding can be performed *Face-to-Face (F2F)* or *Face-to-Back (F2B)*. In F2F processing, the two wafer, or dies, are stacked so that the top metal layers are connected while TSVs are used for the external I/Os. This solution provides the shortest interconnects between the dies, nonetheless it is restricted to maximum two layers. With F2B bonding, on the other hand, multiple device layers can be stacked together with the top metal layer of one die bonded with the substrate of the other die. TSVs are used for the inter-layer connections and the system is no more restricted in the number of stacked dies. The different 3D integration scenarios are summarized in Figure2.2.

Depending on the fabrication process, the physical and electrical characteristics of a TSV can vary substantially. Although using smaller vias is desirable in order to reduce the chip footprint, the minimum TSV diameter is limited by the process yield. Unsuccessful wafer alignment during the bonding process and handling of very thin silicon wafers are the primary mechanisms of TSV failure, with a minimum TSV diameter of 1.2  $\mu m$  reported in the open

Figure 2.3: Typical TSV footprint compared to FEOL structures in a 45 nm CMOS process for 5  $\mu$ m, (a), 2  $\mu$ m (b) and 1  $\mu$ m (c) TSV diamater [24].

| TSV parameters                 | Intermed            | iate Level | Global level |           |  |

|--------------------------------|---------------------|------------|--------------|-----------|--|

|                                | 2011-2014 2015-2018 |            | 2011-2014    | 2015-2018 |  |

| Minimum diameter [ $\mu$ m]    | 1-2                 | 0.8-1.5    | 4-8          | 2-4       |  |

| Minimum pitch [µm]             | 2-4                 | 1.6-3.0    | 8-16         | 4-8       |  |

| Minimum depth [ $\mu$ m]       | 6-10                | 6-10       | 20-50        | 20-50     |  |

| Maximum aspect ratio $[\mu m]$ | 5:1-10:1            | 10:1-20:1  | 5:1-10:1     | 10:1-20:1 |  |

Figure 2.4: a)Simplified TSV interconnect KOZ requirements and b) KOZ for different TSV diameters (on the left) and TSV height (on the right) [25].