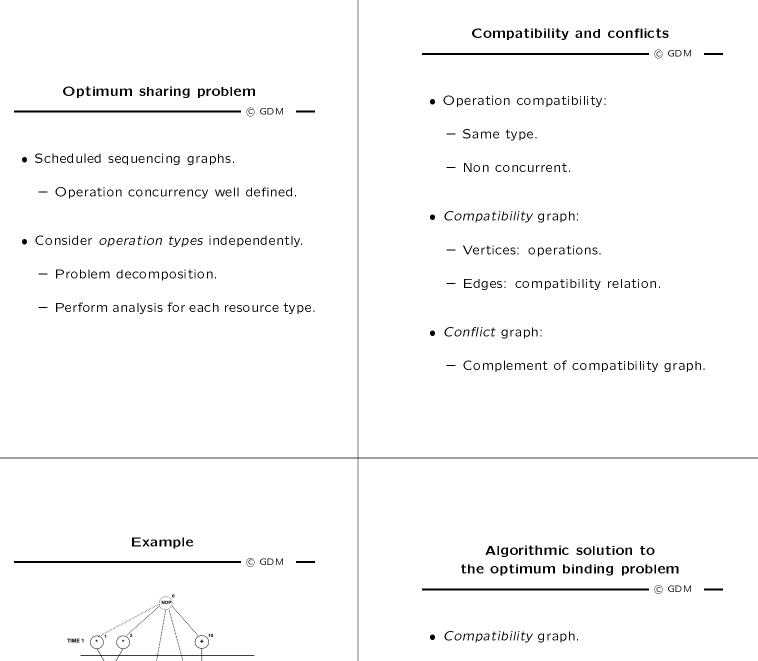

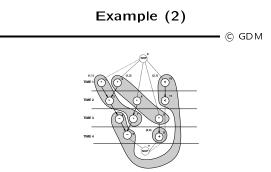

TIME 3

Multiplier

ALU

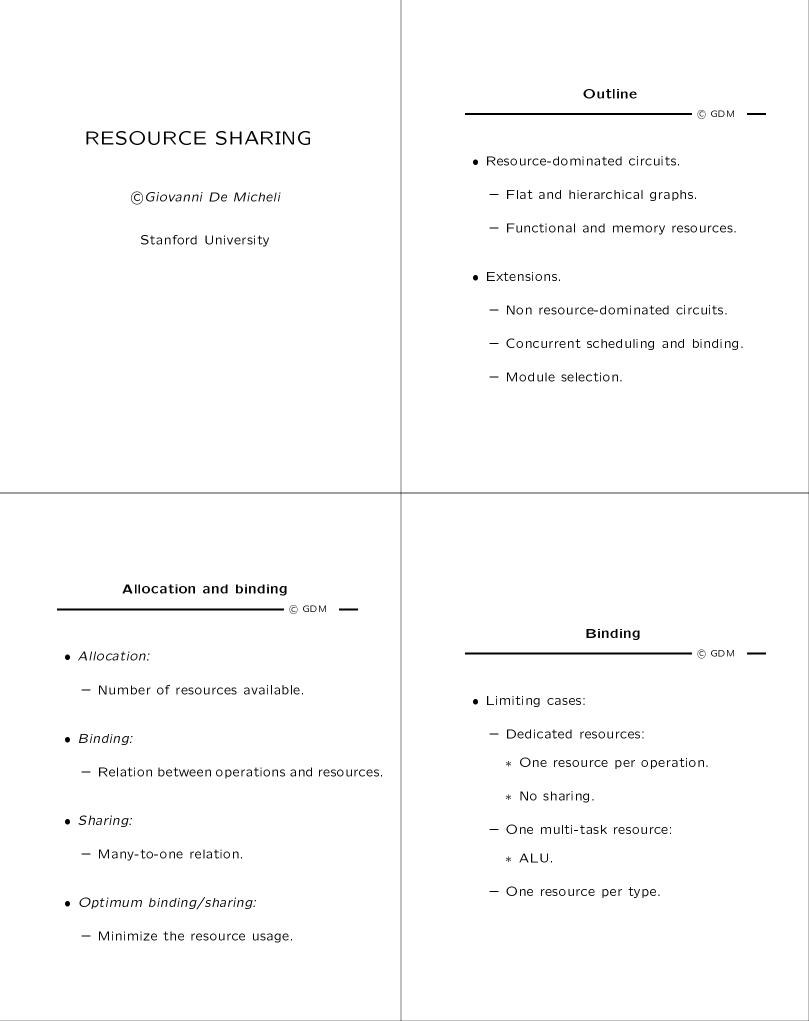

- Partition the graph into a minimum number of cliques.

- Find clique cover number  $\kappa(G_+)$ .

- Conflict graph.

- Color the vertices

by a minimum number of colors.

- Find chromatic number  $\chi(G_{-})$ .

- NP-complete problems Heuristic algorithms.

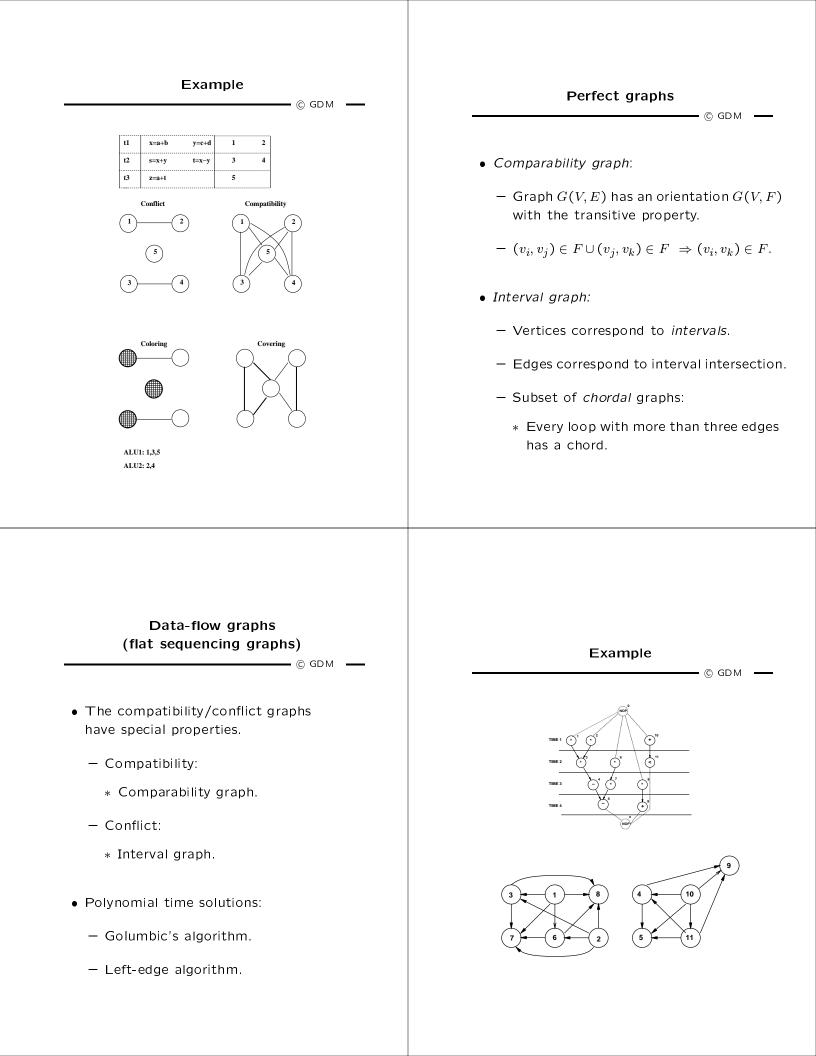

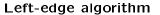

- Input:

- Set of intervals with left and right edge.

- Rationale:

- Sort intervals by left edge.

- Assign non overlapping intervals to first color using the sorted list.

- When possible intervals are exhausted increase color counter and repeat.

- © GDM -

```

\begin{array}{l} LEFT\_EDGE(I) \left\{ & \\ \text{Sort elements of } I \text{ in a list } L \text{ in ascending order of } l_i; \\ c=0; \\ \text{while (some interval has not been colored ) do } \left\{ & \\ S=\emptyset; \\ r=0; \\ \text{while (} \exists s \in L \text{ such that } l_s > r) \text{ do} \right\} \\ & \\ s=\text{First element in the list } L \text{ with } l_s > r; \\ S=S\cup \{s\}; \\ r=r_s; \\ \text{Delete } s \text{ from } L; \\ \\ \\ \\ c=c+1; \\ \text{Label elements of } S \text{ with color } c; \\ \end{array}

```

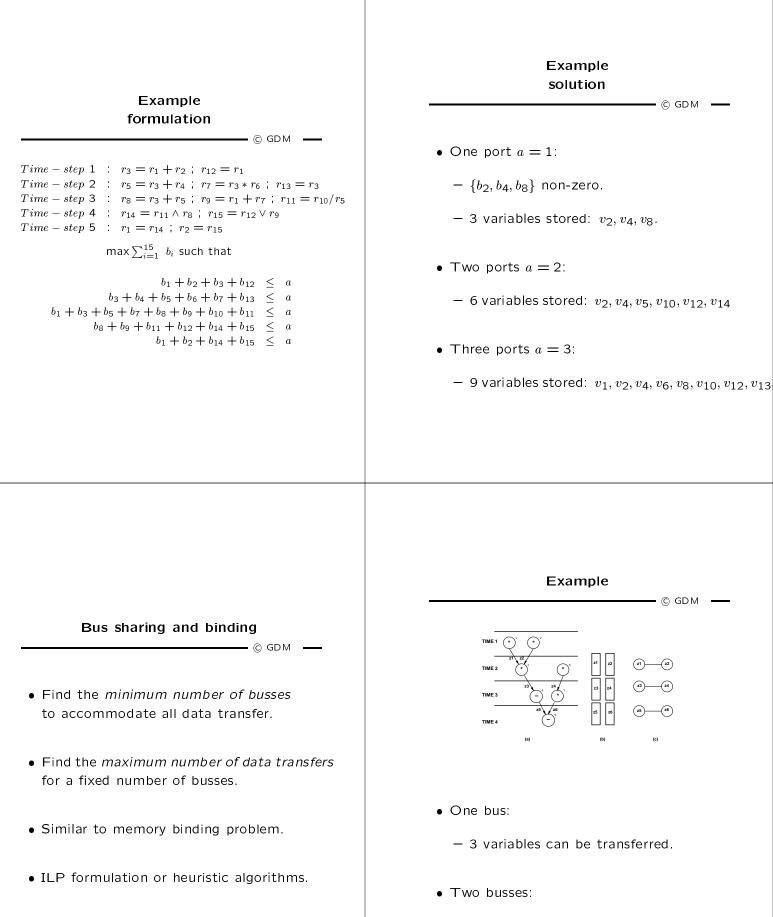

#### **ILP** formulation of binding

\_\_\_\_\_ © GDM \_\_\_\_

- Boolean variables  $b_{ir}$

- Operation i bound to resource r.

- Boolean variables  $x_{il}$

- Operation i scheduled to start at step l.

$$\sum_{r=1}^{a} b_{ir} = 1 \quad orall i$$

$\sum_{i=1}^{n_{ops}} b_{ir} \quad \sum_{m=l-d+1}^{l} x_{im} \leq 1 \quad orall l \; orall r$

— © GDM -

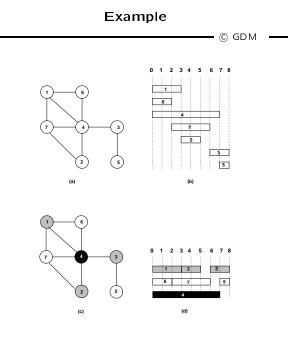

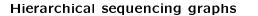

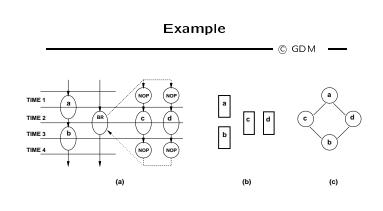

- Hierarchical conflict/compatibility graphs.

- Easy to compute.

- Prevent sharing across hierarchy.

- Flatten hierarchy.

- Bigger graphs.

- Destroy nice properties.

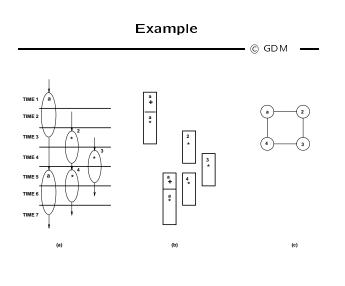

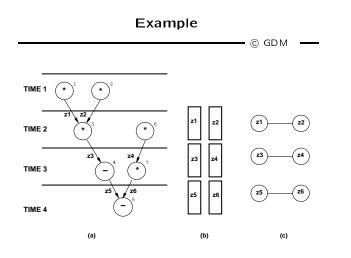

#### Register binding problem

\_\_\_\_\_ © GDM \_\_\_

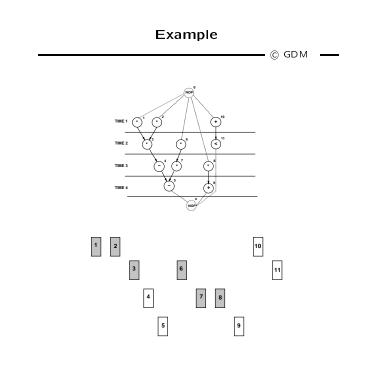

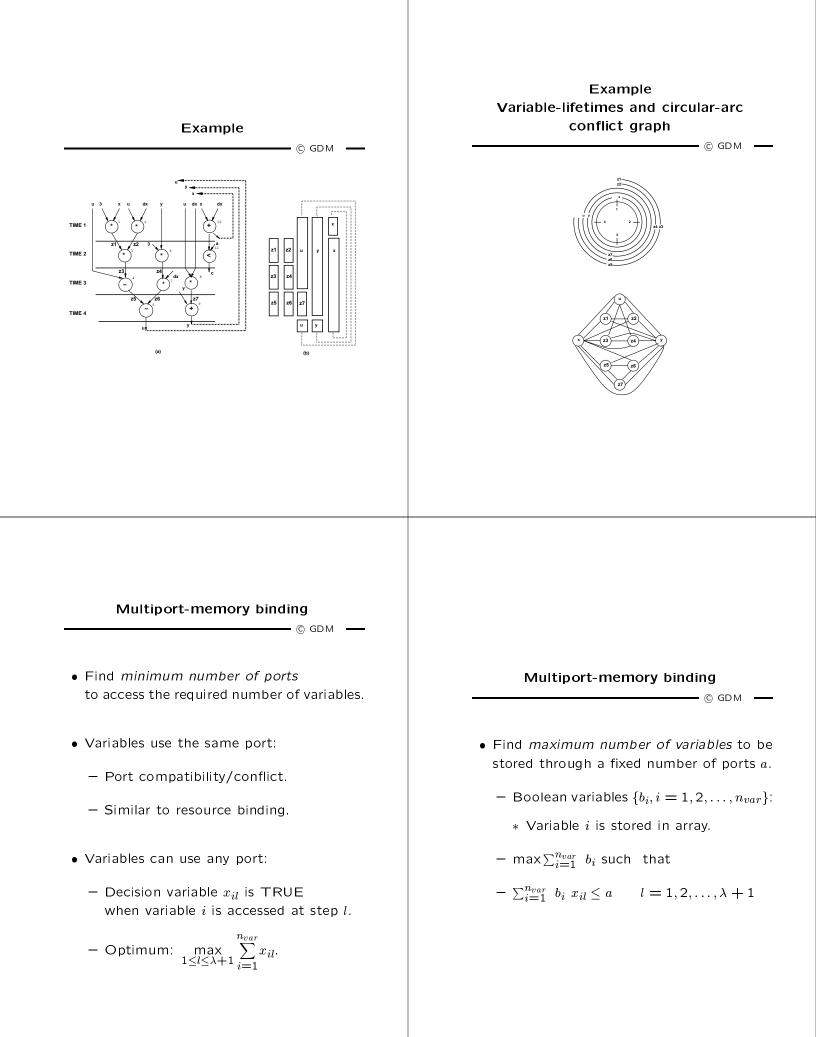

- Given a schedule:

- Lifetime intervals for variables.

- Lifetime overlaps.

- Conflict graph (*interval graph*).

- Vertices  $\leftrightarrow$  variables.

- Edges  $\leftrightarrow$  overlaps.

- Interval graph.

- Compatibility graph (comparability graph).

- Complement of conflict graph.

- © GDM •

- Given:

- Variable lifetime conflict graph.

- Find:

- Minimum number of registers storing all the variables.

- Key point:

- Interval graph:

- \* Left-edge algorithm. (Polynomial-time).

• Heuristic algorithms.

<sup>-</sup> All variables can be transferred.

## Scheduling and binding Resource dominated circuits

\_\_\_\_\_© GDM \_\_\_\_

- Area and delay of resources dominate.

- Strategy:

- Scheduling under area constraints:

- \* Minimize latency.

- Binding.

- \* Share resource within bounds.

- Decoupling between scheduling and binding.

### Scheduling and binding General circuits

— © GDM -

- Area and delay influenced by:

- Sparse logic, wiring, registers and control circuit.

- Binding affects the cycle-time:

- It may invalidate a schedule.

- Scheduling after binding:

- Binding under restrictive assumptions.

- Time-frame of operations not yet known.

# Scheduling and binding approaches

— © GDM —

- Concurrent scheduling and binding.

- ILP model- exact.

- Some heuristic algorithms.

- Scheduling before binding:

- Good for DSP application.

- Binding before scheduling:

- Iterative techniques.

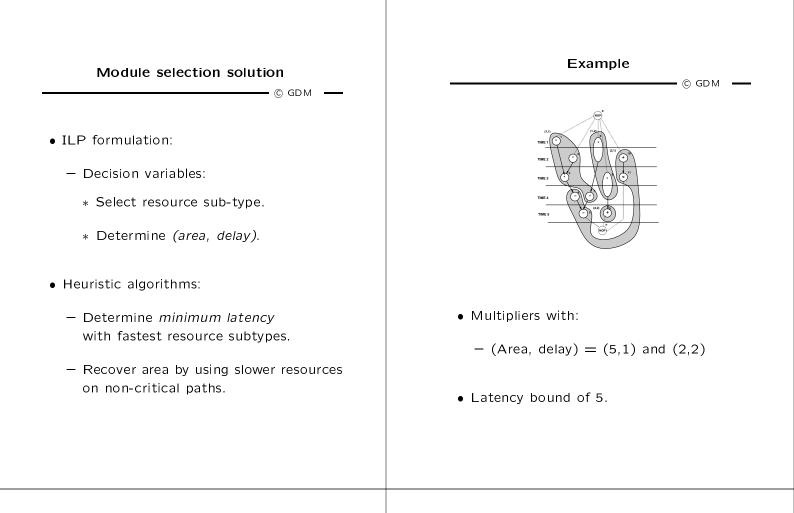

#### Module selection problem

\_\_\_\_\_ © GDM -

- Library of resources:

- More than one resource per type.

- Example:

- Ripple-carry adder.

- Carry look-ahead adder.

- Resource modeling:

- Resource *subtypes* with:

- \* (area, delay) parameters.

- Latency bound of 4.

- Fast multipliers for  $\{v_1, v_2, v_3\}$ .

- Slower multipliers can be used elsewhere.

- \* Less sharing.

- Minimum-area design uses fast multipliers only.