# Design of Thermal Management Control Policies for Multiprocessor Systems on Chip

Francesco Zanini

Submitted for the degree of Doctor of Philosophy in Science EPFL, Lausanne October 2011

# **Abstract**

The contribution of this thesis is a thorough study of thermal aware policy design for MPSoCs. The study includes the modelling of their thermal behavior as well as the improvement and the definition of new thermal management and balancing policies.

The work is structured on three main specific disciplines. The areas of contributions are: modeling, algorithms and system design.

This thesis extends the field of modeling by proposing new techniques to represent the thermal behavior of MPSoCs using a mathematical formalization. Heat transfer and modelling of physical properties of MPSoCs have been extensively studied. Special emphasis is given to the way the system cools down (i.e. micro-cooling, natural heat dissipation etc.) and the heat propagates inside the MPSoC.

The second contribution of this work is related to policies, which manage MPSoC working frequencies and micro-cooling pumps to satisfy user requirements in the most effective possible way, while consuming the lowest possible amount of resources. Several families of thermal policies algorithms have been studied and analyzed in this work for both 2D and 3D MPSoCs including liquid cooling technologies.

The discipline of system design has also been extended during the development of this thesis. Thermal management policies have been implemented in real emulation platforms and contributions in this area are related to the design and implementation of proposed innovations in real MPSoC platforms.

**Keywords:** Thermal, Management, Model, Predictive control, Temperature, Algorithm, 3D-MPSoC, Optimization, Accuracy.

# Riassunto

Il contributo di questa tesi e' uno studio dettagliato dei sistemi di gestione termica(thermal management) per sistemi a multiprocessore(MPSoC). Lo studio prende in considerazione ogni singolo aspetto della tematica trattata: dalle equazioni matematiche che descrivono il comportamento termico degli MPSoC, agli algoritmi di gestione termica, alle politiche di smistamento del workload. La tesi e' multidisciplinare e si sviluppa a partire da tre tematiche principali: modellizzazione, algoritmi e architettura del systema.

Questa tesi estende la tematica della modellizzazione proponenedo nuove tecniche utilizzando un formalismo matematico il comportamento termico di un MPSoC. I meccanismi di trasferimento termico interni all' MPSoC sono stati studiati in dettaglio. Una speciale attenzione e' stata data ai sistemi di raffreddamento(micro-cooling) con liquido refrigerante.

Il secondo contributo di questa tesi riguarda le politiche di gestione energetica e termica per quanto riguarda la scelta della frequenza di funzionamento e della velocita' della pompa dei sistemi di raffreddamento a liquido. Come obbiettivo, il sistema di gestione dell' MPSoC deve rispondere in modo pronto alle richieste dell' utente impiegando il minor numero possibile di risorse e con il minor dispendio energetico possibile. In questa tesi mettiamo a confronto alcune famiglie di algoritmi per sistemi di tipo MPSoC sia planari che utilizzando tecnologie 3D con raffreddamento a liquido.

Il terzo contributo riguarda l'architettura implementativa dei sistemi di gestione termica degli MPSoC proposti in questa tesi. Questi sistemi sono stati sviluppati su piattaforme di simulazione e le principali innovazioni sono legate alla definizione di tali piattaforme software.

Parole chiave: Modellizzazione, Controllo predittivo, Gestione termica, Temperatura, Algoritmi, 3D-MPSoC, Ottimizzazione, Accuratezza.

# **Acknowledgements**

First of all I would like to thank GOD for having given me everything I have achieved

I would like to thank my advisor, Prof. Giovanni De Micheli who gave me the opportunity to pursue research in the beautiful research. He's a person with great vision, who is always interested in exploring new research directions and ideas. He gave me complete freedom in performing research. He has given excellent personal support to all his students, being more of a mentor. During my Ph.D., he gave me the opportunity to travel and see many realities in the best research labs in my field.

I am also thankful to Professor David Atienza for his help in the development of my thesis. He guided me with patience and he also helped me in developing the skills I have now. I thank also him for always finding the time in his busy schedule to read my papers during the night or in the early mornings.

I really thank Professors Luca Capisani, Luca Benini and Colin Jones as well as Dr. Srinivasan Murali for helping me in understanding the theory behind my research work and at the same time giving me directions on how to solve mathematical problems encountered during my research.

I really thank Professor Stephen Boyd for giving me the opportunity to visit his lab at Stanford University and let me see the beauty of the research environment in Silicon Valley. I also thank him for spending a lot of his precious time with me. I really thank also Professor Subhasish Mitra and Yang Wang for the inspiring discussions I had with them during my Stanford experience.

I thank Mohamed Mostafa Sabry Aly for his greatful collaboration in the development of some of my papers. I also thank my colleague Ciprian Seiculescu for his help in correcting homeworks in the Design Technology course at EPFL. Both these people are very friendly, smart and extremely hard working. For me it has been a pleasure to work with them.

I really thank Dr. Sandro Carrara, Nicolas Genko, Alessandro Cevrero, Andrea Bartolini, Martino Ruggiero, Giacomo Paci, Prof. Babak Falsafi, Prof. Heinrich Meyr for the time spent with me and the interesting ideas inspiring discussions.

I also thank the professors and the people who collaborated to the En-

trepreneurial Thought Leaders Seminars (Stanford University) and to the program Venture Challenge (EPFL) for their ideas inspiring and motivational lectures.

I would like to thank Rodolphe Buret for his kindness in resolving the many technical issues that would crop up from time to time. Special thanks must go to Christina Govoni who were helpful beyond words in addressing administrative issues in all my years at EPFL.

I'd like also to thank all the professors from Stanford University, University of Parma, the National University of Ireland, ALaRI and EFPL that helped me in improving my skills.

I am also grateful to my PhD jury members for reading and evaluating my thesis in detail and for providing constructive feedback.

I really would like to thank my parents Fulgenzio and Franca, my brothers Roberto and Davide, my sister Linda for psychologically supporting me during my studies. I'd like also to thank my grandmother Adele for preparing me good food when I was coming back home from Lausanne. I'd like also to thank the support of my uncles Ersilia and Luigi and all my relatives in general. I'd like to thank my uncles Umberto, Sarro, Riccardo for showing me that high achievements in life can be obtained without loosing humility or faith in God. I also Would like to thank all the people who prematurely died before the end of my Ph.d: my grandfathers Pietro and Franco, my grandmother Lea and my uncles Ermete and Maria Teresa.

I'd like also to thank my parents, the University of Parma, EPFL, National University of Ireland, the Franchetti Institute and the ALaRI partners for the economical support that they gave me during my studies.

Special thanks to all my Stanford University and EPFL friends that I made during my studies. For the conversations I had with them and for all the time they always had for me.

# **Contents**

| Al            | bstra | ct                                            | i            |

|---------------|-------|-----------------------------------------------|--------------|

| $\mathbf{Ri}$ | assu  | nto                                           | iii          |

| A             | cknov | wledgements                                   | $\mathbf{v}$ |

| Co            | onten | nts                                           | vii          |

| Li            | st of | Figures                                       | xi           |

| 1             | Intr  | roduction                                     | 1            |

|               | 1.1   | Motivation                                    | 1            |

|               | 1.2   | Contributions                                 | 6            |

|               |       | 1.2.1 Modeling                                | 6            |

|               |       | 1.2.2 Algorithms                              | 7            |

|               |       | 1.2.3 System design                           | 8            |

|               | 1.3   | Assumptions and Limitations                   | 9            |

|               | 1.4   | Thesis Organization                           | 10           |

| <b>2</b>      | Bac   | kground                                       | 11           |

|               | 2.1   | Modeling Background                           | 12           |

|               |       | 2.1.1 Dynamic voltage and frequency scaling   | 12           |

|               |       | 2.1.2 3D-MPSoC and liquid cooling             | 13           |

|               |       | 2.1.3 Thermal modelling                       | 14           |

|               |       | 2.1.4 Thermal sensing                         | 16           |

|               | 2.2   | Algorithms Background                         | 16           |

|               |       | 2.2.1 Reactive policies                       | 16           |

|               |       | 2.2.2 History based policies                  | 17           |

|               | 2.3   | System Design Background                      | 20           |

|               |       | 2.3.1 Validation of policies                  | 21           |

|               |       | 2.3.2 Real-time hardware simulation framework | 21           |

|               |       | 2.3.3 Simulation platform                     | 23           |

| 3             | The   | ermal Models                                  | <b>25</b>    |

viii Contents

|   | 3.1       | Therm   | nal Modeling                                 | 26           |

|---|-----------|---------|----------------------------------------------|--------------|

|   |           | 3.1.1   | State-space heat propagation model           | 26           |

|   |           | 3.1.2   | First order ODE solvers                      | 28           |

|   |           | 3.1.3   | Second order ODE solvers                     | 30           |

|   |           | 3.1.4   | Multi-step fourth order ODE solver           | 30           |

|   |           | 3.1.5   | Changing the sampling rate                   | 31           |

|   | 3.2       | Therm   | nal Simulation Analysis                      | 32           |

|   |           | 3.2.1   | Stability analysis                           | 32           |

|   |           | 3.2.2   | Cell size influence                          | 35           |

|   |           | 3.2.3   | Simulation time step                         | 36           |

|   |           | 3.2.4   | Matrix calculation period                    | 37           |

|   | 3.3       | Liquid  | Cooling                                      | 37           |

|   |           | 3.3.1   | Straight and bent microchannels              | 38           |

|   |           | 3.3.2   | Interlayer cooling layer modeling            | 39           |

|   | 3.4       |         | ary                                          | 41           |

|   |           |         | V                                            |              |

| 4 | Ene       | ergy an | d Workload Models                            | 43           |

|   | 4.1       | System  | n Energy                                     | 44           |

|   |           | 4.1.1   | Energy efficiency quantification             | 44           |

|   |           | 4.1.2   | Energy bounds                                | 46           |

|   | 4.2       | Workle  | oad Model                                    | 48           |

|   |           | 4.2.1   | System architecture                          | 48           |

|   |           | 4.2.2   | Task arrival process                         | 48           |

|   |           | 4.2.3   | Workload model                               | 49           |

|   |           | 4.2.4   | Frequency and power model                    | 50           |

|   | 4.3       | Workle  | oad Prediction                               | 50           |

|   |           | 4.3.1   | Workload arrival process                     | 50           |

|   |           | 4.3.2   | Prediction accuracy                          | 52           |

|   |           | 4.3.3   | Maximum energy concentration based estimator | 52           |

|   |           | 4.3.4   | Polynomial least squares workload prediction | 55           |

|   | 4.4       | Summ    | ary                                          | 57           |

| _ | D 1       |         |                                              |              |

| 5 | 5.1       |         | r Thermal Control with Air Cooling uction    | <b>59</b> 60 |

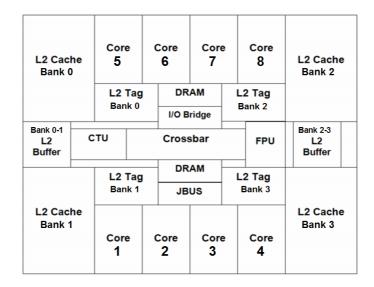

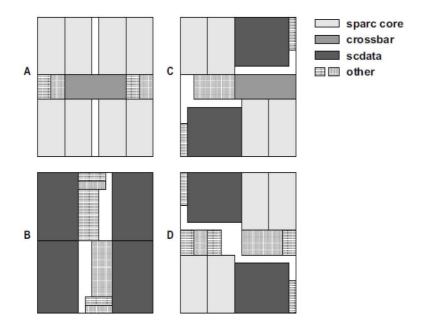

|   | 5.1 - 5.2 |         | PSoC case study                              | 61           |

|   | 5.2       | 5.2.1   | · ·                                          | 61           |

|   |           |         | The Niagara processor                        | 62           |

|   |           | 5.2.2   | Layout                                       |              |

|   |           | 5.2.3   | Frequency Setting and DVFS                   | 62<br>62     |

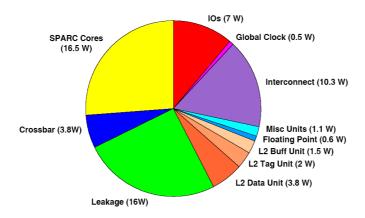

|   |           | 5.2.4   | Power Consumption                            | 63           |

|   | F 0       | 5.2.5   | Benchmarks and Workload Statistics           | 63           |

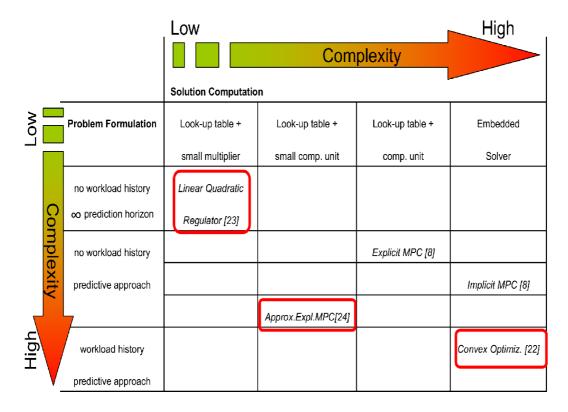

|   | 5.3       | v       | Classification                               | 64           |

|   | 5.4       | _       | arison of Receding Horizon Algorithms        | 67           |

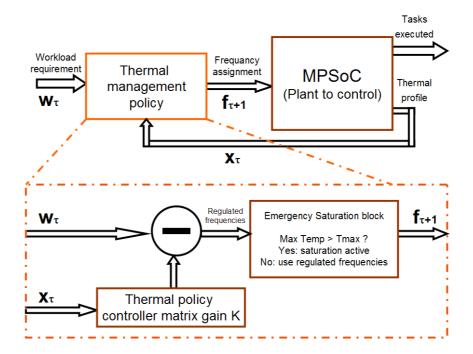

|   |           | 5.4.1   | Linear quadratic regulator                   | 68           |

|   |           | 5.4.2   | Explicit/Implicit MPC                        | 70           |

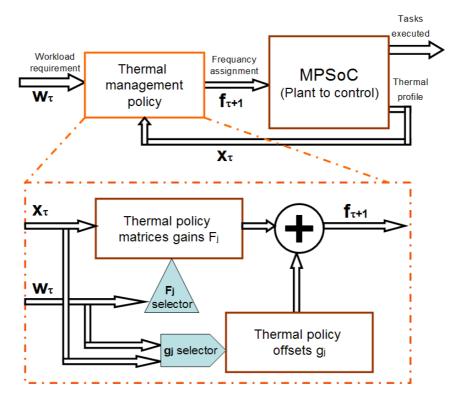

|   |           | 5.4.3   | Approximated explicit predictive policy      | 72           |

Contents ix

|   |      | 5.4.4    | Convex optimization based policies                                                                                         |

|---|------|----------|----------------------------------------------------------------------------------------------------------------------------|

|   | 5.5  | Experi   | imental Results                                                                                                            |

|   |      | 5.5.1    | Policies setup                                                                                                             |

|   |      | 5.5.2    | Executed workload and working temperature 76                                                                               |

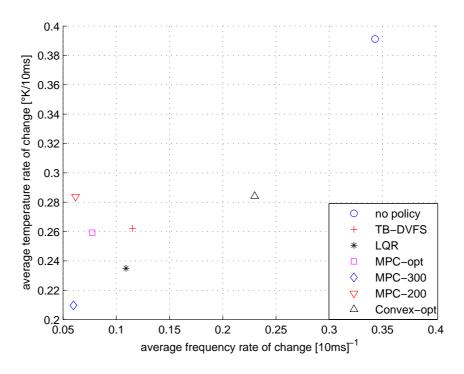

|   |      | 5.5.3    | Thermal and frequency variations                                                                                           |

|   | 5.6  | Summ     | ary 81                                                                                                                     |

| 6 | Poli | icies fo | r Thermal Control with Liquid Cooling 83                                                                                   |

|   | 6.1  | Introd   | uction $\dots \dots \dots$ |

|   |      | 6.1.1    | Centralized thermal management 84                                                                                          |

|   |      | 6.1.2    | Hierarchical thermal management 84                                                                                         |

|   | 6.2  | 3D-MI    | PSoC case study                                                                                                            |

|   |      | 6.2.1    | Layout and Technology Specifications                                                                                       |

|   |      | 6.2.2    | Frequency Setting and DVFS 86                                                                                              |

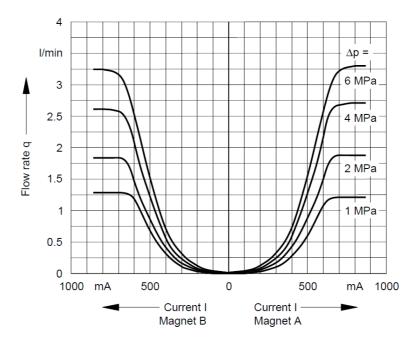

|   |      | 6.2.3    | Cooling Model                                                                                                              |

|   |      | 6.2.4    | Cooling System Power Consumption                                                                                           |

|   |      | 6.2.5    | 3D-MPSoC Power Consumption                                                                                                 |

|   |      | 6.2.6    | Benchmarks                                                                                                                 |

|   | 6.3  | Centra   | alized Thermal Management                                                                                                  |

|   |      | 6.3.1    | Policy computation                                                                                                         |

|   |      | 6.3.2    | Policy setup                                                                                                               |

|   |      | 6.3.3    | Experimental results                                                                                                       |

|   | 6.4  | Distrib  | outed Hierarchical Thermal Policy                                                                                          |

|   |      | 6.4.1    | Hierarchical structure                                                                                                     |

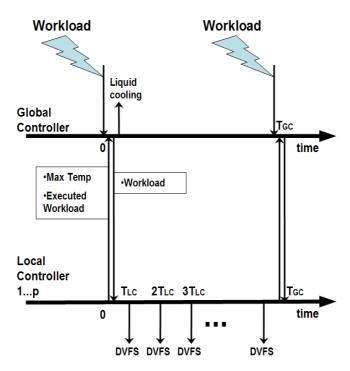

|   |      | 6.4.2    | Run-time interaction: global and local controllers 97                                                                      |

|   |      | 6.4.3    | Design and implementation                                                                                                  |

|   |      | 6.4.4    | Policy computation: global thermal controller 99                                                                           |

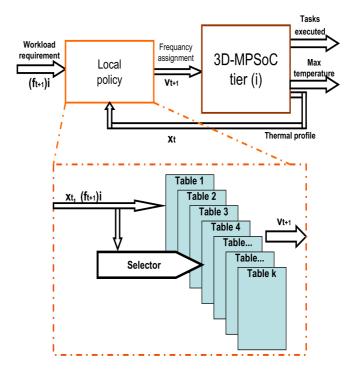

|   |      | 6.4.5    | Policy computation: local controllers                                                                                      |

|   |      | 6.4.6    | Policy setup                                                                                                               |

|   |      | 6.4.7    | Compared 3D-MPSoC thermal management policies 104                                                                          |

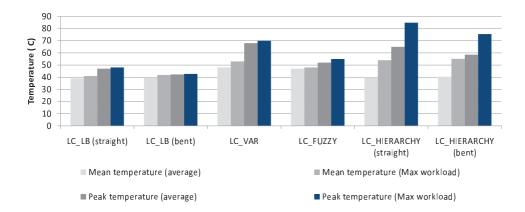

|   |      | 6.4.8    | Results                                                                                                                    |

|   | 6.5  | Summ     | ary                                                                                                                        |

| 7 | Sen  | sor Pla  | acement 10                                                                                                                 |

|   | 7.1  | Therm    | nal Profile Estimation                                                                                                     |

|   |      | 7.1.1    | Temperature estimation by sensing devices 110                                                                              |

|   |      | 7.1.2    | Temperature estimation by observability 112                                                                                |

|   | 7.2  | Full M   | Iodel Placement Algorithm                                                                                                  |

|   |      | 7.2.1    | Methodology                                                                                                                |

|   |      | 7.2.2    | Placement results                                                                                                          |

|   |      | 7.2.3    | Comparison with state-of-the-art methods 117                                                                               |

|   | 7.3  | Model    | Order Reduction Placement Algorithm                                                                                        |

|   |      | 7.3.1    | Introduction                                                                                                               |

|   |      | 7.3.2    | Model: from structure-centric to energy-centric 118                                                                        |

|   |      | 7.3.3    | Identification of relevant states                                                                                          |

x Contents

|    | 7.4         | 7.3.4<br>7.3.5<br>Summ | Balanced state transformation analysis  | 122<br>123<br>125 |

|----|-------------|------------------------|-----------------------------------------|-------------------|

| 8  | Exr         | erime                  | ntal Framework                          | 127               |

| O  | 8.1         |                        | l Infrastructure Overview               | 128               |

|    | 0.1         | 8.1.1                  | Thermal policy computation              | 128               |

|    |             | 8.1.2                  | MPSoC simulation infrastructure         | 129               |

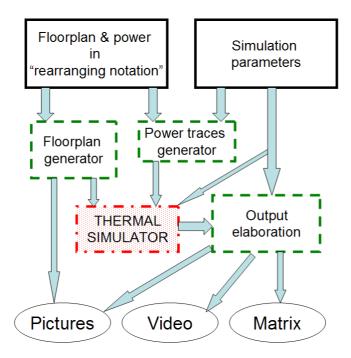

|    |             | 8.1.3                  | Thermal simulator                       | 129               |

|    | 8.2         |                        | nal policy: Matlab code architecture    | 130               |

|    | 0.2         | 8.2.1                  | Optimization algorithm                  | 130               |

|    |             | 8.2.2                  | Reduced order thermal model             | 131               |

|    |             | 8.2.3                  | Thermal profile estimator               | 131               |

|    | 8.3         |                        | C emulator: SystemC code architecture   | 131               |

|    | 0.0         | 8.3.1                  | Virtual Platform Environment            | 131               |

|    |             | 8.3.2                  | DVFS Support                            | 132               |

|    |             | 8.3.3                  | Support for Thermal Management Policies | 133               |

|    | 8.4         |                        | nal Simulator                           | 133               |

|    | 0.1         | 8.4.1                  | Challenges in thermal simulators design | 133               |

|    |             | 8.4.2                  | Proposed syntax and output types        | 134               |

|    |             | 8.4.3                  | Functional diagram of the simulator     | 137               |

|    | 8.5         |                        | ive Thermal Simulation Algorithm        | 138               |

|    | 0.0         | 8.5.1                  | Methodology                             | 138               |

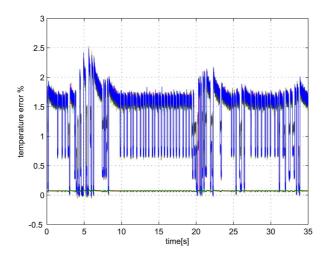

|    |             | 8.5.2                  | Experimental validation results         | 140               |

|    | 8.6         |                        | ary                                     | 141               |

| 9  | Conclusions |                        |                                         |                   |

|    | 9.1         | Thesis                 | Summary and Contributions               | 143               |

|    | 9.2         |                        | e Work                                  | 144               |

| Bi | bliog       | graphy                 |                                         | 147               |

| Cu | ırric       | ulum <b>\</b>          | Vitae                                   | 155               |

# **List of Figures**

| 1.1          | (left) Data center power use in the U. S. (right) Approximate break-                                                         |    |

|--------------|------------------------------------------------------------------------------------------------------------------------------|----|

|              | down of total power used by digital electronics in the U. S. [67] .                                                          | 1  |

| 1.2          | California average residence electricity price. [85]                                                                         | 2  |

| 1.3          | Smartphone Battery Capacity vs. Power Requirements [1]                                                                       | 2  |

| 1.4          | Power density trend of microprocessors [67]                                                                                  | 3  |

| $1.5 \\ 1.6$ | Thermal profile of Sun UltraSPARC T1(niagara) platform [43] Mean Time To Failure Predicted at 90% Confidence Level (courtesy | 3  |

|              | of: ASB inc.)                                                                                                                | 4  |

| 1.7          | Cross-section of a test stack with liquid cooling                                                                            | 5  |

| 1.8          | Comparison in the data center power consumption for an air cooled versus water cooled system [28]                            | 5  |

| 1.9          | Example of a micro-cooling system from [78]                                                                                  | 7  |

| 1.10         | Block model representation of the system                                                                                     | 8  |

| 2.1          | Operating Points in the voltage Vs frequency design space for an ARM Cortex A8 CPU                                           | 12 |

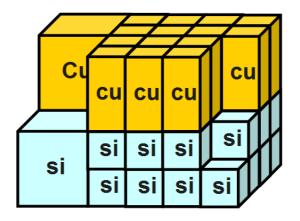

| 2.2          | Simplified illustration of 3D stack with inter-tier liquid cooling                                                           | 13 |

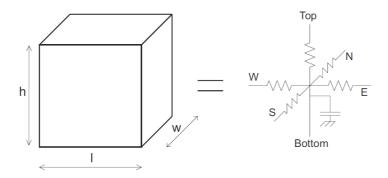

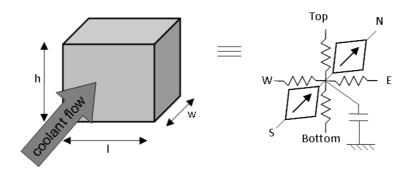

| 2.3          | Cubic cells Model of the MPSoC                                                                                               | 14 |

| 2.4          | Equivalent RC circuit of a cell                                                                                              | 15 |

| 2.5          | Equivalent circuit of a fluid thermal cell                                                                                   | 15 |

| 2.6          | Predictive policies using history information, graphical representa-                                                         | 10 |

| 2.0          | tion [courtesy of Martin Behrendt]                                                                                           | 18 |

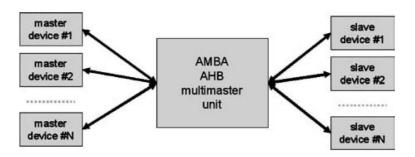

| 2.7          | System architecture [3]                                                                                                      | 22 |

| 2.8          | Processing module architecture [3]                                                                                           | 22 |

| 3.1          | Modeling of the heat transfer inside a 2D-MPSoC                                                                              | 26 |

| 3.2          | Silicon thermal conductivity and linear fit                                                                                  | 27 |

| 3.3          | Circuit for the determination of $\Delta T_{cs}$ and $\Delta T_{ss}$                                                         | 33 |

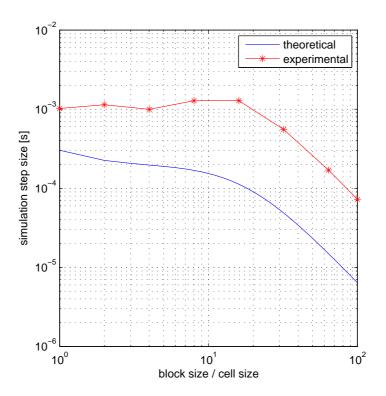

| 3.4          | Experimental vs. theoretical values of $\Delta_{max}$ for various grid reso-                                                 |    |

| <b>.</b>     | lution values.                                                                                                               | 34 |

| 3.5          | Accuracy vs. grid resolution of the floorplan                                                                                | 35 |

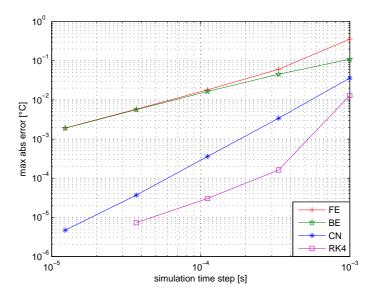

| 3.6          | Accuracy vs. simulation time step $\Delta_{\tau}$                                                                            | 36 |

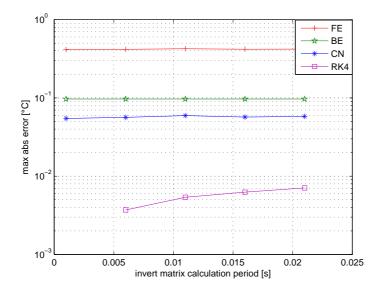

| 3.7          | Accuracy vs. matrix calculation period                                                                                       | 37 |

xii List of Figures

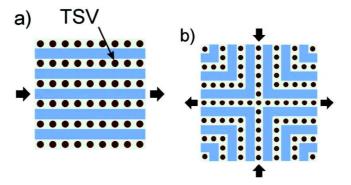

| 3.8        | Top view of a) 2-port and b) 4-port microchannel fluid delivery architecture compatible with area-array interconnects                                                                                                 | 38 |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

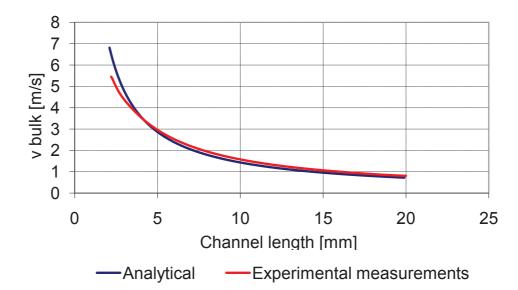

| 3.0        | between the analytical method (Equations 3.48-3.51) and the experimental results shown in Brunschwiler et al. [15]                                                                                                    | 40 |

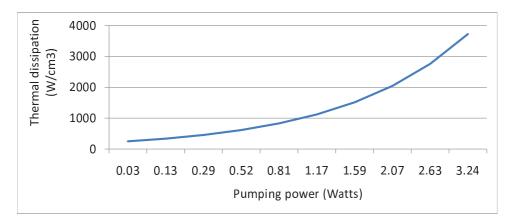

| 3.10       | Rate of change of thermal capability of interlayer liquid cooling $TC$ with respect to pumping power $P_{pump}$                                                                                                       | 41 |

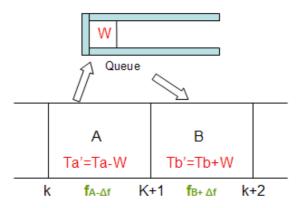

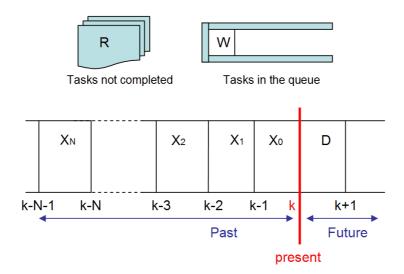

| 4.1<br>4.2 | Scheduler viewpoint snapshot of the MPSoC at time $k$ Effect of a frequency estimation error from a frequency perspective in a DVFS system. (top): ideal case; (bottom) real case with an estimation error $\Delta f$ | 44 |

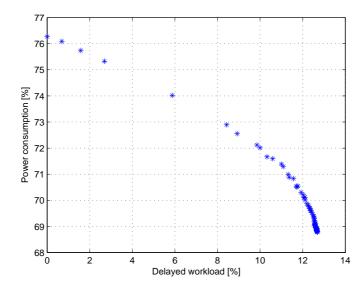

| 4.3        | Example of normalized power consumption versus delayed workload for different optimization criteria ranging from power-oriented to                                                                                    | 47 |

| 4.4        | performance-oriented optimizations                                                                                                                                                                                    | 48 |

| 4.4        | Snapshot of the task arrival process at time $k$                                                                                                                                                                      | 48 |

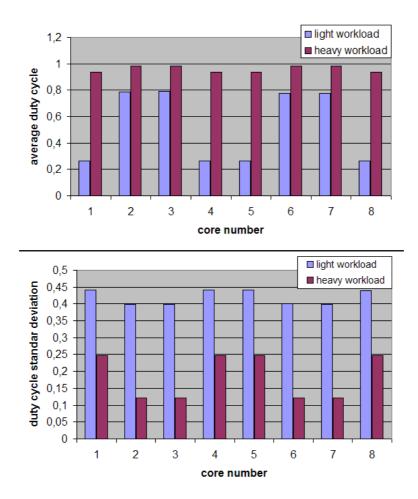

| 4.6        | Duty factor mean and standard deviation of cores during system                                                                                                                                                        | 10 |

| 1.0        | operation                                                                                                                                                                                                             | 51 |

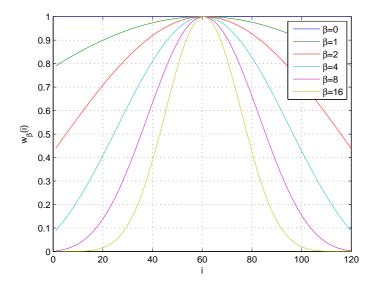

| 4.7        | Kaiser window function for $N=120$ and different values of $\beta$                                                                                                                                                    | 53 |

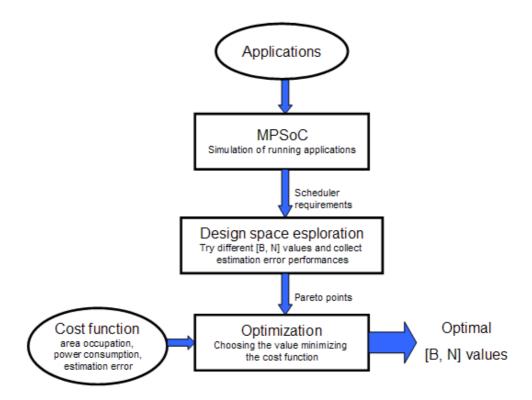

| 4.8        | Block diagram description of the method used to derive $\beta$ and $N$                                                                                                                                                |    |

|            | parameters from real applications or benchmarks                                                                                                                                                                       | 54 |

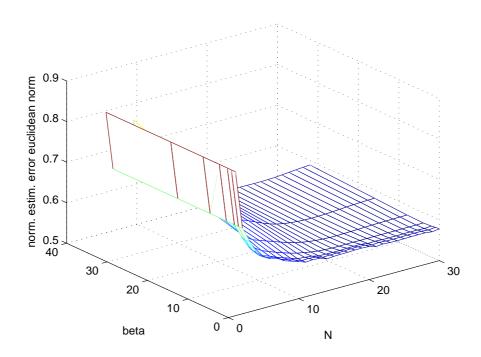

| 4.9        | Euclidean norm of the estimation error normalized to the average                                                                                                                                                      |    |

|            | maximum number of tasks executable by the MPSoC                                                                                                                                                                       | 55 |

| 4.10       | Structure of matrix A                                                                                                                                                                                                 | 56 |

| 5.1        | Diagram of a generic DVFS-based thermal management system .                                                                                                                                                           | 60 |

| 5.2        | UltraSPARK T1 processor, die photograph by courtesy of SUN [49]                                                                                                                                                       | 61 |

| 5.3        | Floorplan of the Niagara-1 multicore case study                                                                                                                                                                       | 62 |

| 5.4        | Niagara, chip power consumption.                                                                                                                                                                                      | 63 |

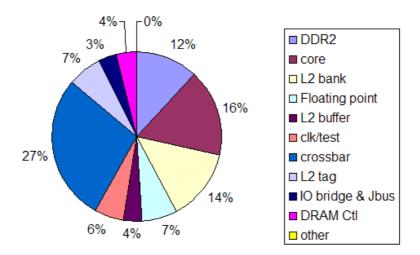

| 5.5        | Niagara, chip power consumption by unit type                                                                                                                                                                          | 64 |

| 5.6        | Classification of compared thermal management policies                                                                                                                                                                | 65 |

| 5.7        | Linear Quadratic Regulator-based policy block diagram                                                                                                                                                                 | 68 |

| 5.8        | Explicit model predictive control-based policy block diagram                                                                                                                                                          | 70 |

| 5.9        | Explicit model predictive control example: (a) state values $x(t)$ and                                                                                                                                                |    |

|            | resulting input $u(t)$ , (b) state-space partition and corresponding                                                                                                                                                  |    |

|            | control trajectories                                                                                                                                                                                                  | 71 |

|            | Embedded solver-based policy block diagram                                                                                                                                                                            | 74 |

| 5.11       | Temperature Vs executed workload normalized to the one that can<br>be executed by the MPSoC running with the highest possible fre-                                                                                    |    |

|            | quency setting                                                                                                                                                                                                        | 77 |

| 5.12       | Temperature gradients analysis. Normalized executed workload Vs                                                                                                                                                       |    |

|            | temporal temperature gradient (top); normalized executed work-                                                                                                                                                        |    |

|            | load Vs spatial temperature gradient (center); spatial Vs temporal                                                                                                                                                    |    |

|            | temperature gradient (bottom)                                                                                                                                                                                         | 78 |

| List of Figures | 2 | xiii |

|-----------------|---|------|

| •               |   |      |

| 5.13       | Temperature rate of change Vs frequency rate of change                                                                           | 80         |

|------------|----------------------------------------------------------------------------------------------------------------------------------|------------|

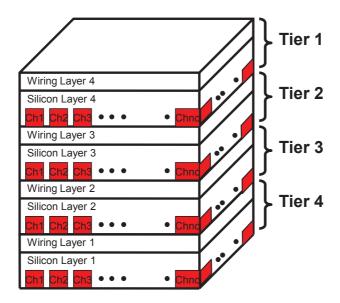

| 6.1        | Structure of the 4-tier 3D-MPSoC model with interlayer liquid cooling                                                            | 85         |

| 6.2        | Floorplan of the used silicon tiers in our 3D-MPSoC model                                                                        | 86         |

| 6.3        | Electric current absorption (power consumption) and flow rates of                                                                |            |

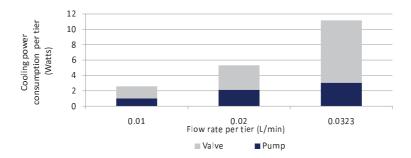

|            | the cooling infrastructure per one tier. Data from [32]                                                                          | 88         |

| 6.4        | Power consumption and flow rates of the cooling infrastructure per                                                               | 00         |

| 6.5        | one tier                                                                                                                         | 89         |

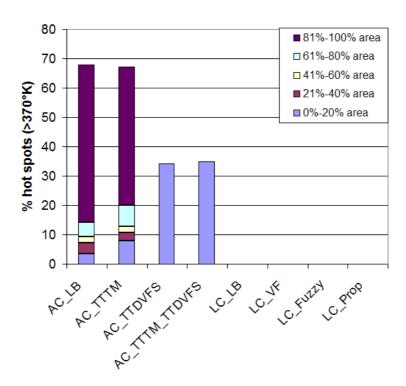

| 0.5        | perature is higher than the threshold $(370^{\circ}K)$ . The area of the                                                         |            |

|            | hotspot is also provided as a percentage of the overall MPSoC area                                                               | 93         |

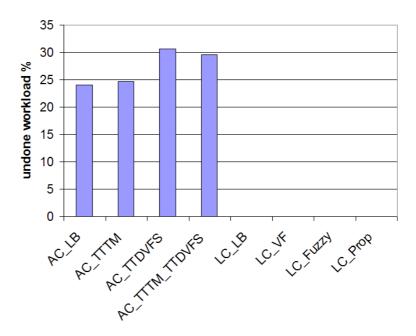

| 6.6        | Undone work as a percentage of the overall requested workload .                                                                  | 94         |

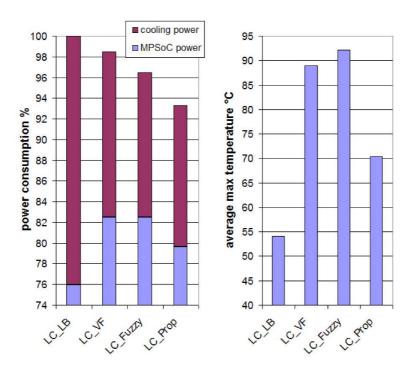

| 6.7        | left graph: energy consumption of the overall system: 3D MPSoC                                                                   |            |

|            | power consumption and cooling network. Values are normalized to                                                                  |            |

|            | LC_LB; right graph: average maximum 3D MPSoC temperature                                                                         | o <b>-</b> |

| <i>c</i> o |                                                                                                                                  | 95         |

| 6.8<br>6.9 | Structure of the proposed hierarchical thermal management system<br>Communication protocol between the global and the local con- | 96         |

| 0.9        | trollers of the proposed method                                                                                                  | 97         |

| 6.10       |                                                                                                                                  | 01         |

| 0.10       | mal management                                                                                                                   | 98         |

| 6.11       | Local policy controller block diagram                                                                                            | 102        |

| 6.12       | Peak and average temperatures observed using all the policies, both                                                              |            |

|            | for the average case across all workloads and maximum workload                                                                   |            |

| 0.10       | on 4-tier 3D-MPSoC                                                                                                               | 105        |

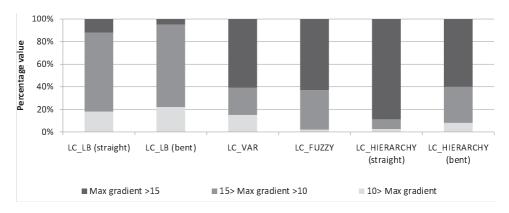

| 6.13       | Maximum thermal gradient of the whole 3D-MPSoC stack, using the average case of all workloads                                    | 106        |

| 6 14       | Average intralayer thermal gradient of the whole 3D-MPSoC stack,                                                                 | 100        |

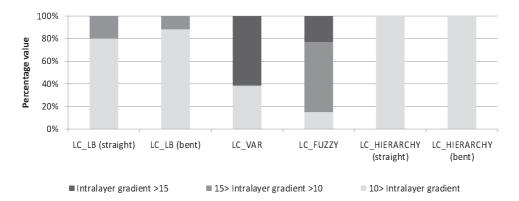

| 0.14       | using the average case of all workloads                                                                                          | 107        |

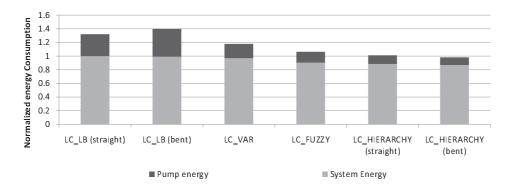

| 6.15       | The normalized energy consumption in the whole system (chip and                                                                  |            |

|            | cooling network) averaged per stack                                                                                              | 107        |

| 7.1        | Percentage error between every cell of the silicon layer and the one                                                             |            |

| 1.1        | of the copper layer on it normalized to the difference between the                                                               |            |

|            | silicon temperature and the ambient one $(300^{\circ}C)$                                                                         | 111        |

| 7.2        | Maximum chip temperature estimation (in Kelvin degrees): real                                                                    |            |

|            | versus thermal sensors                                                                                                           | 112        |

| 7.3        | Graphical representation of selection matrix ${\bf C}$ for the case study                                                        |            |

|            | floorplan described in the experimental setup chapter                                                                            | 113        |

| 7.4        | Proposed method block diagram                                                                                                    | 114        |

| 7.5        | Design space exploration of the case study (step 2)                                                                              | 116        |

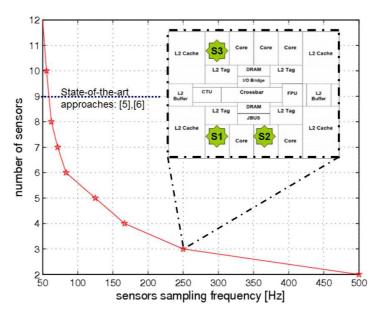

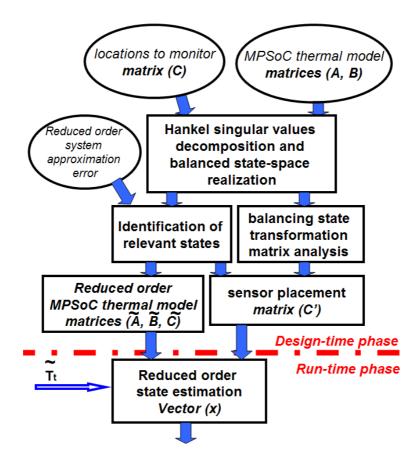

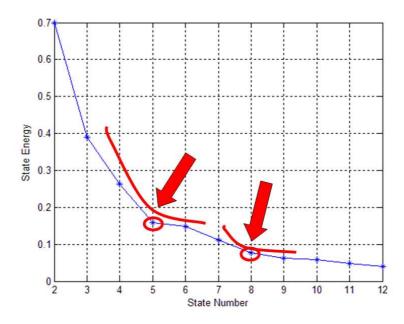

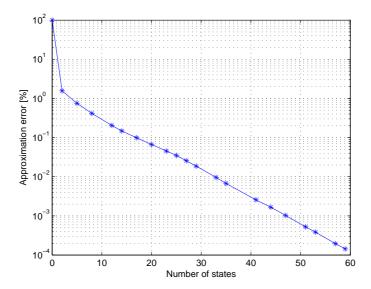

| 7.6<br>7.7 | Pareto points (steps 3+4) and comparison with [5],[6]                                                                            | 116<br>119 |

| 1.1        | Troposed memod block diagram                                                                                                     | T T O      |

xiv List of Figures

| 7.8  | Decay rate analysis for the normalized energy related to Hankel singular values for our case study. Red arrows points to change in       |     |

|------|------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | the decay rate.                                                                                                                          | 121 |

| 7.9  | Model approximation error [%] versus number of states in the reduced model for our case study                                            | 121 |

| 7.10 | Sensor location according to the most relevant component identifying each state of the new thermal model. Horizontal lines delimits      |     |

|      | one layer from another                                                                                                                   | 122 |

| 7.11 | Sensor placement algorithm: percentage of accurate temperature estimation according to the number of sensors placed with the pro-        |     |

|      | posed methodology                                                                                                                        | 124 |

| 7.12 | Sensor placement for our case study with sensors (marked as red stars on the floorplan) sampling frequency $T_s$ of $1ms$                | 125 |

| 8.1  | Global infrastructure block diagram                                                                                                      | 128 |

| 8.2  | Global infrastructure block diagram                                                                                                      | 130 |

| 8.3  | Simulation infrastructure block diagram                                                                                                  | 132 |

| 8.4  | First example of a description using the new description language.                                                                       | 134 |

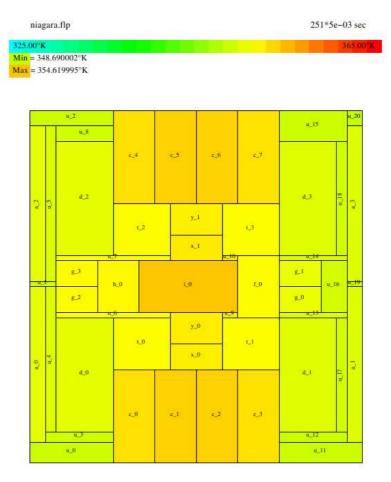

| 8.5  | Niagara, chip thermal profile at time 1.255ms                                                                                            | 136 |

| 8.6  | Functional block diagram of the developed framework                                                                                      | 137 |

| 8.7  | Thermal simulator design flow                                                                                                            | 138 |

| 8.8  | Design space exploration using our adaptive thermal simulator                                                                            | 139 |

| 8.9  | Normalized comparison of the proposed method (accuracy= $3\cdot10^{-3}$ °C with RK4-based thermal simulators (as HotSpot) and (FE)-based | ")  |

|      | thermal simulators                                                                                                                       | 141 |

Introduction

#### 1.1 Motivation

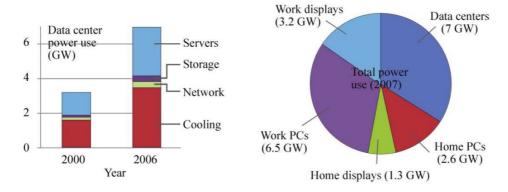

Some of the greatest challenges of modern society are related to energy consumption, dissipation, and waste. Among these, present and future technologies based on nanoscale materials and devices hold great potential for improved energy conservation, conversion, and harvesting. A prominent example is that of integrated electronics, where power dissipation issues have recently become one of its greatest challenges. For example, Figure 1.1 shows that data center energy consumption have doubled in the last five years, with waste heat requiring drastic cooling solutions like air conditioning systems. These cooling solutions increase even more the energy consumption of data centers. If present growth trends are maintained, data center and overall electronics power use

**Figure 1.1:** (left) Data center power use in the U. S. (right) Approximate breakdown of total power used by digital electronics in the U. S. [67]

2 Introduction

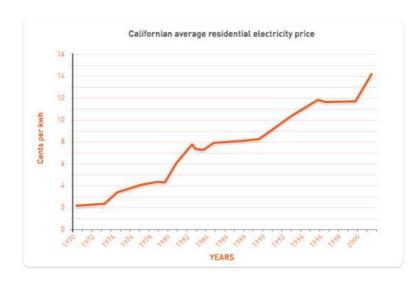

Figure 1.2: California average residence electricity price. [85]

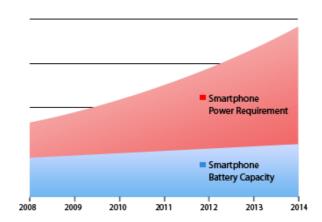

**Figure 1.3:** Smartphone Battery Capacity vs. Power Requirements [1]

could reach one third of total U. S. consumption by 2025 [67].

Moreover the cost of electricity keeps on growing. Figure 1.2 shows the cost for electricity in California where many data centers are located nowadays. Since 1980, the annual electric rates have increased an average of 2.91% and can reasonably be assumed to continue to rise at least that much over the next 25 years.

Energy consumption has become one of the primary concerns in electronic design due to the recent popularity of portable devices such as smartphones and laptops. Figure 1.3 shows battery capacity versus power requirements in the case of smartphones. The battery capacity has improved very slowly (a factor of 2 to 4 over the last 30 years), while the computational demands have drastically increased over the same time frame.

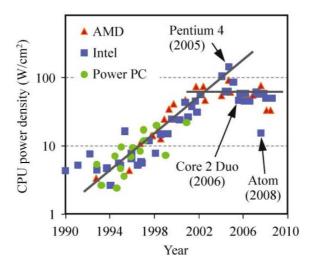

Figure 1.4 shows two power density trends in microprocessors power den-

1.1. Motivation 3

**Figure 1.4:** Power density trend of microprocessors [67]

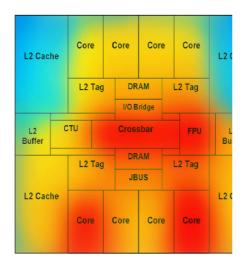

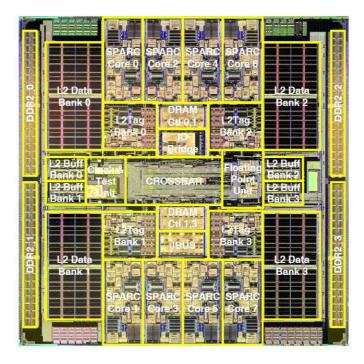

Figure 1.5: Thermal profile of Sun UltraSPARC T1(niagara) platform [43]

sity. The first trend is the one of high-performance microprocessors such as pentium 4, where performance is guaranteed by allowing heat spreaders, fans and liquid cooling technologies on the device. The second trend is the one of low-performance devices such as core 2 Duo and Atom where the power density has to be limited to a fixed maximum value. The reason is because either the limited heat extraction capabilities of the portable device or the fact that the device has to last long without recharging its battery.

A further problem is shown in Figure 1.5. As it can be noted, the thermal profile of a commercial MPSoC is quite nonuniform and hot spots (localized MPSoC areas with unsafe working temperature) may arise. This effect does not only affect the performance of the system, but also leads to unreliable circuit operation and affects the life-time of the chip [79]. Figure 1.6 shows

4 Introduction

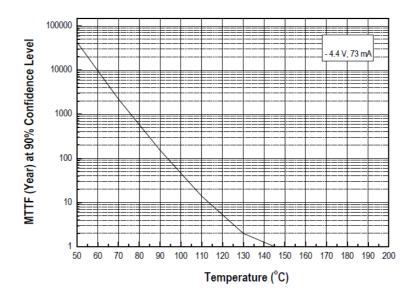

**Figure 1.6:** Mean Time To Failure Predicted at 90% Confidence Level (courtesy of: ASB inc.)

how temperature affects the lifetime (Mean Time to Failure) of a silicon device. As it can be noted there is an approximately exponential behavior between the junction temperature and the lifetime of the silicon device. Thus, thermal management for multicore architectures is a critical matter to tackle.

In the last years, thermal management and balancing techniques received a lot of attention. Many state-of-the-art thermal control policies operate power management by employing dynamic frequency and voltage scaling (DVFS) based techniques [60],[37]. This technique scales down the frequencies and the voltages of some specified units to save power and optimize performance. The problem with this technique is that the frequent abrupt change in working frequencies and voltages produces thermal cycling that raises the failure rate of the system [35], [90]. In addition, discontinuous power-mode transitions, both in voltage and frequencies scaling, waste additional power [42]. For the aforementioned reasons there are many trade-offs in power management techniques that are not easy to handle properly during the runtime execution of the MPSoC and with a low computational overhead.

Moreover, new challenges are related to emerging technologies for heat extraction. Heat extraction is based on a "heat sink". A heat sink is a component or assembly that transfers heat generated within a solid material to a fluid medium, such as air or a liquid. Examples of heat sinks are the heat exchangers used in refrigeration and air conditioning systems and the copper dissipator placed on top of microprocessors in desktop computers. A heat sink is physically designed to increase the surface area in contact with the cooling fluid surrounding it, such as the air. In past decades the research to increase the heat extraction performed by this element was focused on changing design

1.1. Motivation 5

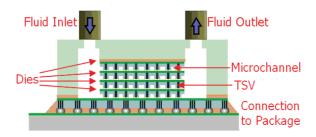

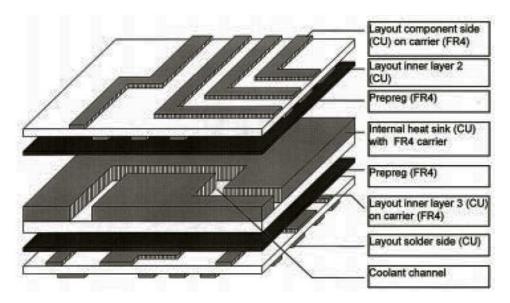

**Figure 1.7:** Cross-section of a test stack with liquid cooling.

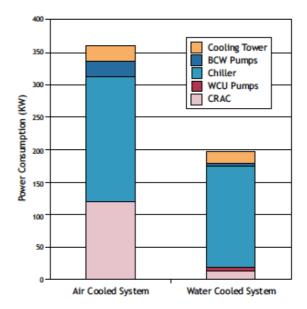

**Figure 1.8:** Comparison in the data center power consumption for an air cooled versus water cooled system [28]

factors such as: air velocity, choice of material, fin (or other protrusion) design and surface treatment. In recent years with the increase of power density the research has been focused on changing the coolant fluid. Not only air is used nowadays but also fluids circulating and exchanging heat with the heat spreader. The pipes where the coolant liquid is circulating can be either integrated inside MPSoCs [51]-[50] or placed on top of them [78]-[73] as shown in Figure 1.7. Experiments have shown that when a coolant fluid is pumped through the microchannels, up to  $3.9KW/cm^3$  [15] of heat can be extracted. Figure 1.8 shows the power saving of using liquid cooling in data centers versus air cooling. Energy consumption within the data center is reduced because computer room air conditioners (CRACs) are replaced by more efficient modular water cooling units (WCUs). These new cooling technologies represent a key perspective for novel thermal management policies to both reduce cooling power consumption and at the same time increase performance.

6 Introduction

#### 1.2 Contributions

The contribution of this thesis is a thorough study of thermal aware policy design for MPSoCs. The study includes the modelling of MPSoCs thermal behavior as well as the improvement and the definition of new thermal management and balancing policies. MPSoC modelling, input parameters required by the optimization process as well as all the factors that improve its quality are analyzed in detail. Thus, the project has been develop on three main axes:

- Modeling: heat transfer and modelling of physical properties of MPSoCs.

The goal is to model with a mathematical formalization the thermal

behavior of MPSoCs. Special emphasis is given to the way the system

cools down (i.e. micro-cooling, natural heat dissipation etc.) and the

heat propagates inside the MPSoC.

- Algorithms: control theory based and convex optimization based optimization algorithm to manage the MPSoC to maximize performance, increase reliability and minimize power consumption. The policy manages MPSoC working frequencies and micro-cooling systems to reach its goal in the most effective possible way and consuming the lowest possible amount of resources.

- System design: design and implementation of proposed innovations in real MPSoC platforms. Policies are implemented in real emulation platforms. This field deals with constraints and problems related to the design of real implementation of proposed policies in 3D MPSOC systems.

## 1.2.1 Modeling

The objective of this part of the thesis is to improve the accuracy of current models and extend them from a 2-D to a 3-D perspective including liquid cooling methods. Contributions are the following:

A study of the integration method with reference to stability and accuracy. The integration method is used by the thermal management policy to predict the future thermal profile of the chip based on power dissipation values, current chip thermal profile and MPSoC floorplan. Stability and accuracy are two important points in discrete-time integration methods. New mathematical methods have been proposed.

Micro-cooling in 3D MPSoC. With the increasing of power density in new technologies, new cooling devices have been introduced. These device are integrated either inside MPSoCs [51], [93], [50] or they are placed on their heat spreading layers [78], [73]. An example of micro-cooling is shown in figure 1.9 [78]. New modelling techniques have been proposed to address the inclusion of new active and passive MEMS-based cooling systems for MPSoCs.

1.2. Contributions 7

Figure 1.9: Example of a micro-cooling system from [78]

#### 1.2.2 Algorithms

The contribution is a novel set of thermal management algorithms. These algorithms are based on a receding horizon approach that is called *model predictive* control (MPC) [2].

This mathematical technique tries to solve the thermal management problem inside an MPSoC in a similar way to playing chess. The control problem is indeed formulated over an interval of L time steps. The result of the optimization is an optimal sequence of future control moves, in the same way a player in chess is predicting future movements of the other player. Only the first sample of such a sequence is actually applied to the process, the remaining moves are discarded. At the next time step, a new optimal control problem based on new temperature measurements is solved over a shifted prediction horizon.

The goal of the thermal management algorithm is to satisfy performance user constraints while keeping the chip in a reliable condition. This condition implies that there are no localized areas in the chip where the silicon temperature is above a manufacturer specified vale (i.e.  $370^{\circ}$ ). Another requirement is the fact that the chip does not have rapid thermal variations or large gradients in its thermal profile.

Algorithms have been analyzed according to their hardware implementation requirements and also to their optimality. Indeed there is a trade-off in designing the algorithm between its accuracy and its optimality. All aforementioned issues have been considered while designing and comparing proposed families of algorithms for both air and liquid cooling technologies.

8 Introduction

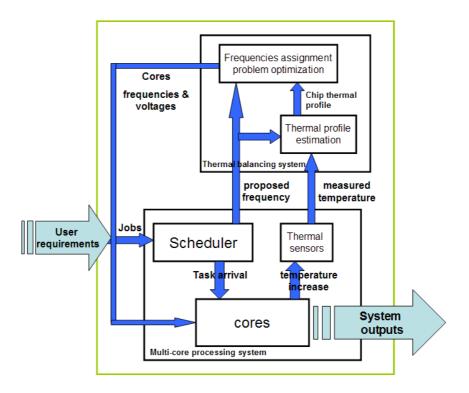

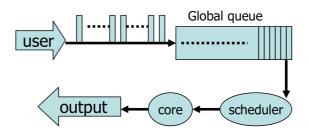

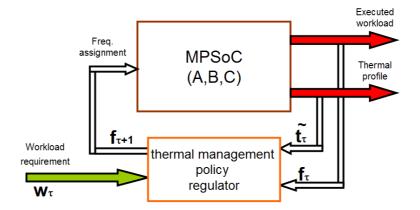

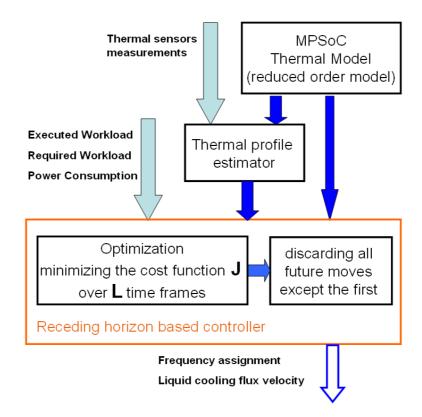

Figure 1.10: Block model representation of the system

#### 1.2.3 System design

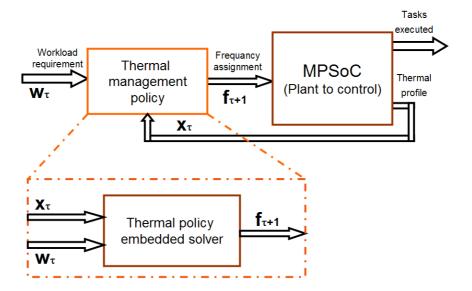

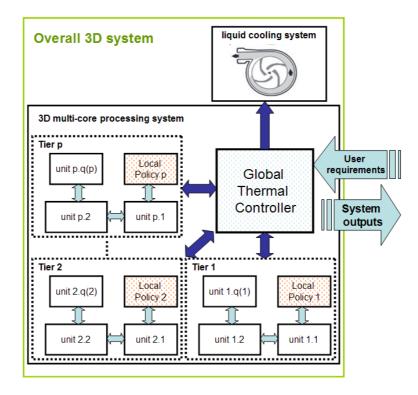

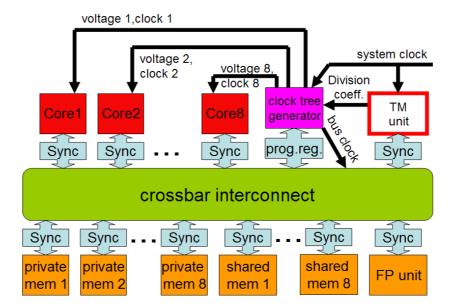

I describe contributions related to the design of implementations of proposed policies in 3D MPSOC systems. Figure 1.10 shows the block model representation of the system. The system can be divided into two main parts: the *multi-core processing system* (MPS) and the *thermal management system* (TMS).

The first one is the part of the MPSoC that takes user requirements and produces desired outputs. It can be seen as the plant to control. It consists of the cores, a scheduler and some thermal sensors that make some temperature measurements in some specific points of the chip.

The second part can be seen as the control system of the plant. It tries to optimize its performance by using information it receives from the MPS. The TMS consists of two subparts: one that estimates the thermal profile and one that solves the frequency assignment problem. The first one has to estimate and reconstruct the thermal profile starting from measurements coming from sensors. The second subpart has to find the optimum frequencies and voltages assignment for the cores in order to both meet performance requirements, reduce power consumption and improve chip reliability preventing hotspots. Constraints on the maximum temperature of the MPSoC are also respected in the optimization process. The optimization algorithm can be implemented with a look-up table(explicit) or an embedded solver(implicit).

The feasibility of the thermal management policy implementation has been addressed. To compare policies we consider trade-offs between the optimality and its implementation requirements. The policies have been tested with real scenarios common in many applications.

# 1.3 Assumptions and Limitations

As with any research work, there are some realistic assumptions that are used for building the proposed methods:

- Application and architecture scaling: The first assumption is that the number of cores on a chip is increasing and MPSoCs integrate several applications. This is a realistic assumption, as the chip complexity has been scaling roughly in accordance with the Moore's law. Today, there is indeed a convergence of several different applications onto the same platform, with massive computation and communication complexity.

- Synchronous design: It is assumed that the entire MPSoC supports different working frequencies. We also assume that functional units composing the MPSoC can be grouped into specific frequency islands each one working at a specific frequency (which can, if needed, be varied dynamically). Because of the aforementioned considerations, globally asynchronous locally synchronous (GALS) architectures are not supported.

- Power model: It is assumed that the power model of every functional unit inside the MPSoC is dependent on its working frequency. This is true in most applications, However for memories it is true only when cache misses are in the order of few percent (true in most architectures nowadays).

The main purpose of this work is to provide design methods. Thus, we tested our methods only on few specific case studies. However, without any loss of generality, every technique presented in this thesis can be applied to a large variety of MPSoCs. I envision that the methods presented in this work will have wide applicability, dealing with different architectures and operating conditions.

Due to the above assumptions, methods presented in this work do have some limitations:

Methods presented in this work can be applied only to architectures that can provide different frequency modes. Power data used in this work are abstracted at the component level and not at the transistor level. This means that we know the power consumption of the many blocks or functional units composing the MPSoC, however we do not know how this power is distributed among the different transistors. This is because of the lack of detailed power consumption information related to most commercial MPSoC architectures.

10 Introduction

# 1.4 Thesis Organization

This thesis is divided into the following sections:

Chapter 2 gives a background on state-of-the-art techniques about the fields related to this work. Modeling, algorithms and system design are the main areas described by this survey.

Chapter 3 introduces mathematical models used in this thesis. Models are related to the heat transfer model of the MPSoC. A liquid cooling model of a 3d-MPSoC is also provided.

Chapter 4 introduces the concepts developed to model the workload of an MPSoC system. Moreover some considerations are made about the system energy models used in this thesis. Workload prediction is also introduced and two estimation techniques are presented.

Chapter 5 introduces air cooling algorithms. Four families of policies are analyzed and compared by both theoretical studies and experimental tests. We also provide a classification of the policies according to their problem formulation complexity and their computational effort requirements. The 2D-MPSoC case study used to run the simulations is also presented in detail.

Chapter 6 introduces liquid cooling algorithms. Two novel algorithms are proposed here. The first one is based on a centralized controller based on convex optimization. The second controller is a distributed structure based on the interaction between a global unit and many small controllers. The 3D-MPSoC case study used to run the simulations is also presented in detail.

Chapter 7 introduces techniques to perform a detailed thermal profile estimation of the MPSoC structure. Two techniques are presented here to achieve a temperature estimation by using few thermal sensors placed in specific locations on the MPSoC.

Chapter 8 presents the thermal simulation infrastructure used to test and compare policies presented in this thesis. The infrastructure consists of many parts written with three different programming languages and simulated on different simulation platforms.

Chapter 9 concludes the dissertation by summing up the contribution of this research and highlighting some possible extensions of this work in other areas.

# Background

In this chapter we give a background material helpful for understanding the algorithms and methods proposed subsequently in this thesis. The background material is presented grouped into the three main areas of contribution of this work: Modeling, Algorithms and System design.

12 Background

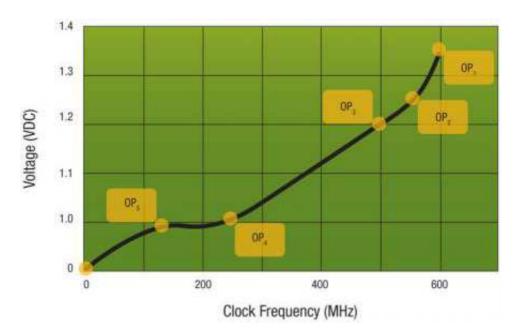

**Figure 2.1:** Operating Points in the voltage Vs frequency design space for an ARM Cortex A8 CPU

# 2.1 Modeling Background

The goal of this section is to give the basic background material to be able to understand innovations proposed in this thesis about new mathematical thermal models for MPOSoCs.

# 2.1.1 Dynamic voltage and frequency scaling

Dynamic voltage and frequency scaling (DVFS) is a technique to reduce energy consumption by changing processor speed and voltage at run-time depending on the needs of the applications running. This method is widely used as part of strategies to manage switching power consumption in battery powered devices such as cell phones and laptop computers. Low voltage modes are used in conjunction with lowered clock frequencies to minimize power consumption associated with components such as CPUs and DSPs; only when significant computational power is needed will the voltage and frequency be raised. Special supply regulation circuits are required to be able to deliver a multiple set of voltages to the SoC. Figure 2.1 shows possible voltages and frequencies operating points for the case of an ARM core.

It is important to vary both the voltage and the frequency because if only processor frequency is scaled, the total energy savings would be small or zero as power is inversely proportional to cycle time and energy is proportional to the execution time and power. The switching power dissipated by a chip using static CMOS gates is  $CV^2f$ , where C is the capacitance being switched per clock cycle, V is voltage, and f is the switching frequency, so this part of

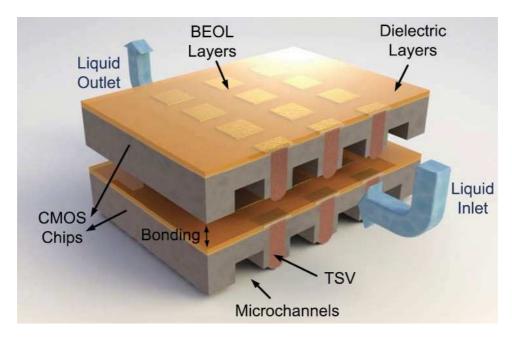

Figure 2.2: Simplified illustration of 3D stack with inter-tier liquid cooling

the power consumption decreases quadratically with voltage [70]. The formula is not exact however, as many modern chips are not implemented using only CMOS, but also uses pseudo nMOS gates, domino logic etc.

Moreover, there is also a static leakage current, which has become more and more accentuated as feature sizes have become smaller (below 90 nanometers) and threshold levels lower. When leakage current is a significant factor in terms of power consumption, chips are often designed so that portions of them can be powered completely off. This capability is an additional challenge to be managed in new thermal management systems.

## 2.1.2 3D-MPSoC and liquid cooling

A three-dimensional integrated circuit (3D IC, 3D-IC, or 3-D IC) is a chip in which two or more layers of active electronic components are integrated both vertically and horizontally into a single circuit. 3D integration [8] is a recently proposed design method for overcoming the limitations with respect to delay, bandwidth, and power consumption of the interconnects in large multiprocessor system-on-chip (MPSoC) chips, while reducing the chip footprint and improving the fabrication yield. The main reason of all these benefits is the introduction of connections from one die to the other. These vertical wires are called Through Silicon Vias (TSV) and they allow us to make connections shorter as compared to a normal 2D chips [59]. A simplified illustration of a TSV in a 3D stack is shown in Figure 2.2.

Figure 2.2 is an example of 3D MPSoC where liquid cooling(liquid inlet/liquid outlet) is used as cooling mechanism. The reason for using liquid 14 Background

Figure 2.3: Cubic cells Model of the MPSoC

cooling is because of the higher thermal resistivity [39],[68], which irregularly spread in the 3D chip stack. Hence, it is more difficult to remove the heat from 3D systems with respect to conventional 2D MPSoCs.

Conventional back-side heat removal strategies, such as, air-cooled heat sinks and micro-channel cold-plates only scale with the die size and are insufficient to cool 3D MPSoC with hot spot heat fluxes up to 250W/cm2, as expected in forthcoming 3D MPSoC stacks [14]. On the contrary, inter-tier single and two-phase liquid cooling is a potential solution to address the high temperatures in 3D MPSoCs, due to the higher heat removal capability of liquids in comparison to air [16].

The use of convection in microchannels to cool down high power density chips has been an active area of research since the initial work by Tuckerman and Pease [88]. The heat removal capability of interlayer heat-transfer with pin-fin in-line structures for 3D chips is investigated in Brunschwiler et al. [14].

## 2.1.3 Thermal modelling

Skadron et al. [81] and Paci et al. [64] have developed a thermal-power model for super-scalar architectures. It not only predicts the temperature variations between the different components of a processor, but also accounts for the increased leakage power and reduced performance. Their results clearly prove the importance of hot spots in high performance systems. Based on this model, many architectural extensions have been proposed.

The model exploits the well known analogy between electrical circuits and thermal models. It decomposes the silicon die and heat spreader in elementary cells which have a cubic shape (Figure 2.3) and use an equivalent RC-model for computing the temperature of each cell. By varying the cell size can trade-off the simulation speed of the thermal with its accuracy. The coarser the cells become, the fewer cells we need to simulate, but the less accurate the temperature estimates become.

Figure 2.4: Equivalent RC circuit of a cell

Figure 2.5: Equivalent circuit of a fluid thermal cell.

A thermal capacitance and five thermal resistances are associated with each cell (Figure 2.4). Four resistances are used for modeling the horizontal thermal spreading whereas the fifth is used for the vertical thermal behavior. See [64] for further details.

These concepts model with a good accuracy 2D and 3D chips using air cooling. In the case of liquid cooling, the model has been modified to the one presented by Sridhar et al. [83]. This model is exactly the same for any silicon or metal structure. The only difference is the introduction of the way the liquid cooling flow has been modelled. A graphical representation is shown in Figure 2.5.

Cells corresponding to microchannels containing the cooling fluid are modelled like any other cell with the addition of a current source and a current sink. To model the heterogeneous characteristics of the variable flow rate in microchannels, Sridhar et al. [83] introduced the ability to change the intensity of the current source and the resistance value of the cell at runtime. Thus, the interlayer material composing the MPSoC is divided into grid cells, where each grid cell except for the cells of the microchannels has a fixed thermal resistance value depending on the characteristics of the interface material. Thermal properties of the microchannel cells are computed based on the liquid flow rate through the cell at runtime as presented in Sridhar et al. [83].

16 Background

#### 2.1.4 Thermal sensing

Any thermal management algorithm to control the system must know the overall state (or thermal profile) of the MPSoC. This means that the temperature of every single cell in which the floorplan has been divided must be known.

A study of the thermal profile estimation problem has been presented in Memik et al. [56] and Sharifi and Rosing [80]. The proposed solutions are based on techniques trying to reduce temperature differences between thermal sensors and hot-spots by using the minimum possible number of sensors for a certain accuracy. The problem with these approaches is that since hot-spots are application dependent, there is no guarantee that all hot-spots are detected during the lifetime of the device.

A better approach to estimate these temperatures is to use a state estimator [33]. A state or thermal profile estimator is an algorithm able to derive the current thermal profile based on measurements in some specific locations on the chip with a specific rate. The parameter that measures how much a system is observable is called Observability. Observability refers to the property of a system that enables the reconstruction of the state variables given the inputs [33]. It means that we are able to reconstruct completely the thermal profile of the chip given the inputs only by looking at the measurements coming from the sensors.

The placement problem in an MPSoC is the problem of selecting right locations of thermal sensors to both minimize the number of sensors and maximize the observability of the system. Sumana and Venkateswarlu [86] select the location of the sensing element according to a sensor strategy using just described observability concept. Joshi and Boyd [41] solved the problem of making a system observable by employing of graph theory. The problem of choosing a set of measurements from a much larger set that also minimizes the estimation error is solved by Boukhobza and Hamelin [10] using a convex optimization based approach. This last method approximately solves the problem and has no guarantee that the performance gap is always small.

## 2.2 Algorithms Background

The goal of this section is to give the basic background material to be able to understand concepts behind the family of algorithms proposed in this thesis.

## 2.2.1 Reactive policies

This family of methods does not exploit history information. The policy takes reactive decisions based on information related to the current thermal profile and frequency setting of the MPSoC to control. For this reason they are defined as reactive policies.

The problem with this family of policies is that they react only when the thermal situation starts to be critical. For this reason their reaction is usually fast and abrupt frequency and corresponding temperature variations are generated. These variations undermine the reliability of the system.

#### Clock gating and DVFS-based policies

Dynamic power management, (see Benini and Micheli [5] for more details), was developed first for single processors. Lu et al. [52] devised a software architecture that enables system designers to investigate power management algorithms in a systematic fashion.

Merchant et al. [58] devised a variable speed processor which is thermally controlled based on an estimation on the hottest junction temperature of the chip. The problem with this method is that it uses a simplistic thermal model to predict the hottest junction temperature of the chip. This assumption degrades the quality of results.

Benini et al. [4], Paleologo et al. [65] and Qiu et al. [69] proposed policies based on stochastic optimum control. These methods take power management decisions based on theories of Markov decision processes and stochastic networks. Markov processes have by definition no memory of the past history of the system.

Early methods based on monitoring the idle time in processors have been presented by Halfhill [36], where DVFS has been used to turn off functional units when they were not being used. Later, more refined power management policies working at the OS-level were proposed. Rosing and Boyd [76] designed a methodology for managing power consumption in networks on chip. Xie and Hung [94] presented a set of scheduling mechanisms for MPSoCs that perform temperature management at the system-level.

Donald and Martonosi [26] reduced significantly localized hotspots by using thread migration techniques. Coskun et al. [24] designed a dynamic scheduling algorithm with negligible performance overhead. Bircher and John [7] used processor counters to get an online monitoring of the overall power consumption. Reda et al. [74] achieved temperature and hotspot tracking by a smart sensor allocation technique.

## 2.2.2 History based policies

To improve the efficiency of thermal management policies, memory has been introduced inside thermal management algorithms. This family of methods indeed, take decisions based on past information related to thermal profile, power consumption, frequency and liquid cooling setting and thermal model of the MPSoC. Past history information is used to predict the consequence that decisions taken by the policy have on the MPSoC.

18 Background

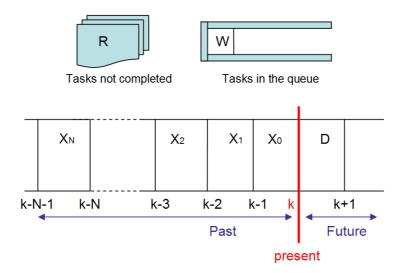

**Figure 2.6:** Predictive policies using history information, graphical representation [courtesy of Martin Behrendt]

#### Model predictive control and convex optimization

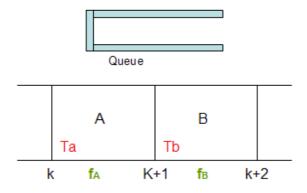

Model Predictive Control (MPC) is a technique that uses information on the MPSoC model and on the history to improve the desired performance target. A graphical representation is shown in Figure 2.6. The red line on Figure 2.6 shows the reference trajectory that in our case represents the requirements that the MPSoC has to satisfy. The yellow line is the measured output that the system can provide (i.e. MPSoC executed workload). At time  $\tau$  the current state of the system is sampled and a specific control strategy is computed (light-blue line) (via a numerical minimization algorithm) for a relatively short time horizon in the future:  $[\tau, \tau + L]$ . The prediction horizon is called L. Specifically, the policy explores state trajectories (brown line) that emanate from the current state at time  $\tau$  and find a control strategy until time  $[\tau, \tau + L]$ .

Only the first step of the control strategy is implemented, then the plant state is sampled again and the calculations are repeated starting from the new current state (now at time  $\tau+1$ ), yielding a new control and new predicted state path. The prediction horizon keeps being shifted forward and for this reason this approach is also called receding horizon control. The control problem is indeed formulated over an interval of L time steps. The result of the optimization is an optimal sequence of future control moves, in the same way a player in chess is predicting future movements of the other player.

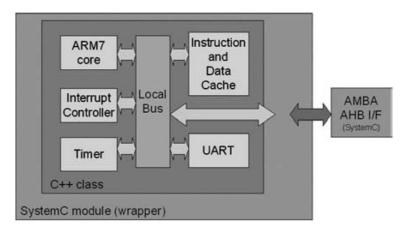

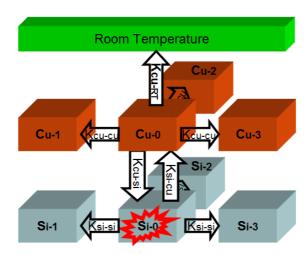

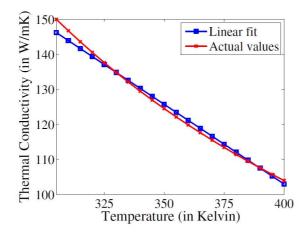

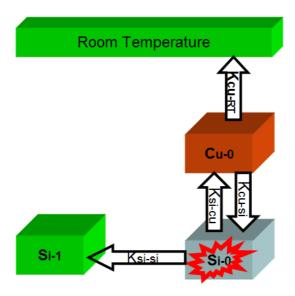

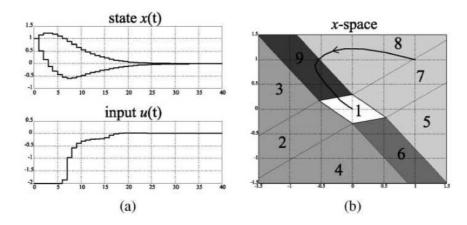

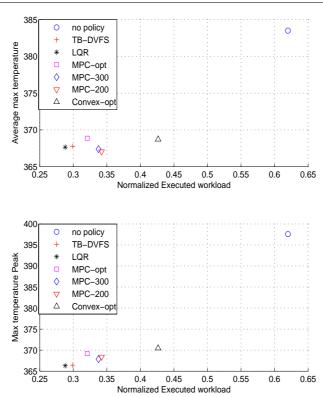

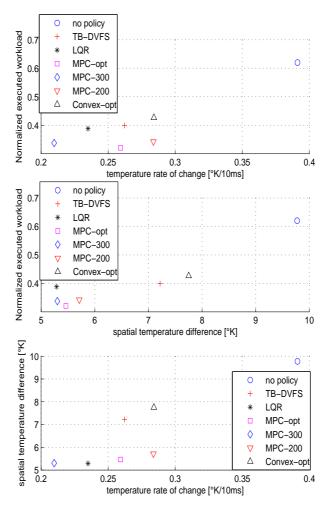

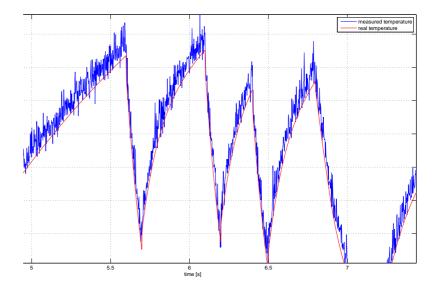

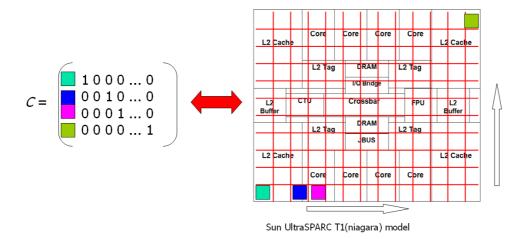

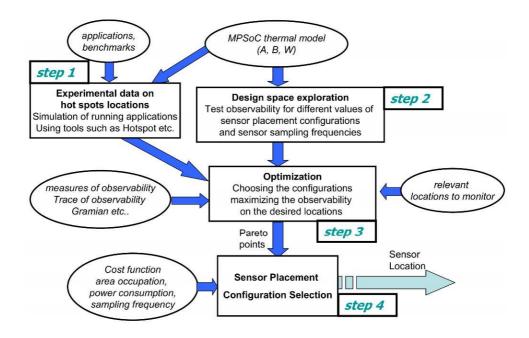

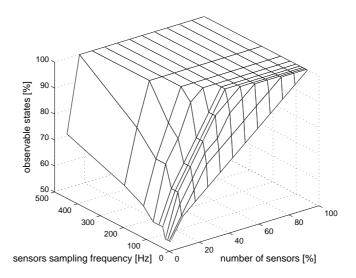

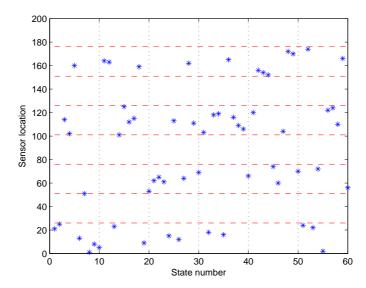

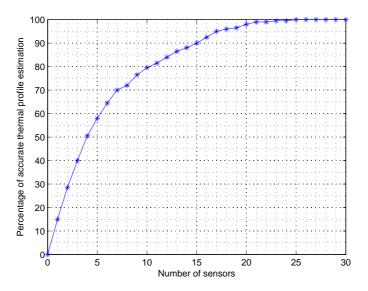

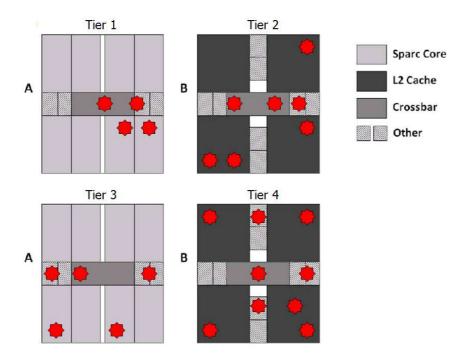

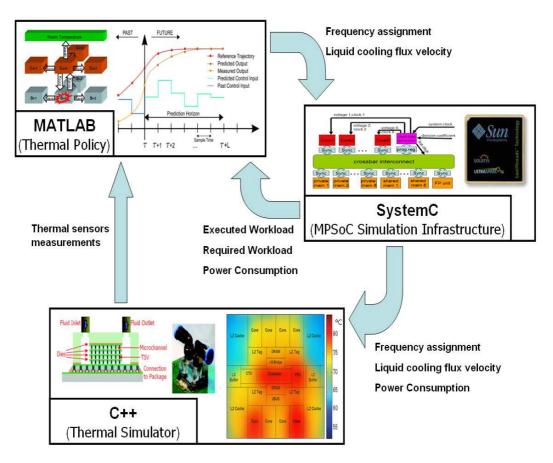

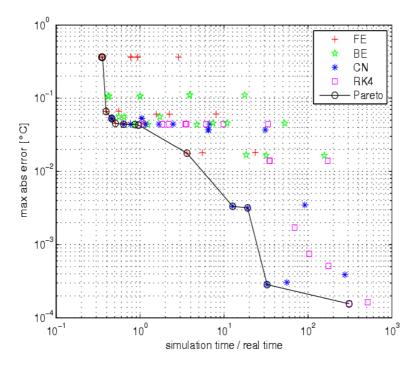

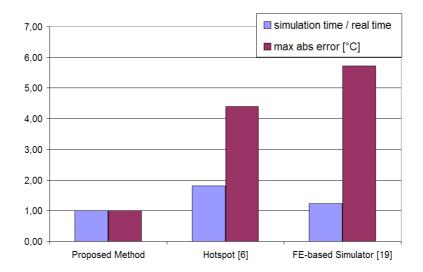

In this thesis, we propose many different ways to solve the optimization problem. The first one is implicit and requires to solve on-line the minimization problem every time the policy is applied. With the second approach the optimization problem is solved off-line in a way that makes explicit the dependence of the solution on input parameters. Bemporad et al. [2] have shown