### SAT-Based Exact Synthesis for Multi-Level Logic Networks

Thèse N°9404

Présentée le 31 mai 2019

à la Faculté informatique et communications Laboratoire des systèmes intégrés (IC/STI) Programme doctoral en informatique et communications

pour l'obtention du grade de Docteur ès Sciences

par

### Winston Jason HAASWIJK

Acceptée sur proposition du jury

Prof. P. lenne, président du jury

Prof. G. De Micheli, Dr M. Soeken, directeurs de thèse

Dr A. Mishchenko, rapporteur Prof. P. Beerel, rapporteur Prof. D. Atienza, rapporteur

Beware of bugs in the above code; I have only proved it correct, not tried it. — Donald Knuth

To my family.

## Acknowledgements

Writing a PhD thesis is not an easy task. It is clear to me that this work would not have been possible without the kind help of many people. Unfortunately, there is no way for me to do justice to all of them here. Nevertheless, I will do my best.

First, I would like to thank all of my friends and colleagues at the LSI. The relaxed and friendly atmosphere at the office made a big difference in my PhD experience, especially knowing that not everyone is so lucky.

Second, I want thank my original co-advisor Pierre-Emmanuel Gaillardon. It was PE who showed me how the academic sausage is made when I first came to EPFL.

Next, I would like to mention some of our friends and partners from Synopsys Inc. for being such gracious hosts and supporters of my work. My thanks especially goes out to Luca Amarù, Patrick Vuillod, Jiong Luo, and Janet Olson.

I have to mention and thank Alan Mishchenko for our many valuable discussions. A true logic synthesis guru, his ideas were always inspiring. After our conversations I would be ready play around with new and exciting concepts.

Academic research is a skill, and I have not received more practical tips and tricks about it from anyone else than Mathias Soeken. I am indebted to him for our countless discussions and collaborations. Without his help my time in Switzerland would have been much more difficult.

Speaking of research, there is one last academic I have not mentioned yet. I sincerely thank Giovanni De Micheli for allowing me to do my PhD research at the LSI. Nanni was always patient and gave me the time, space, and freedom to pursue the projects that I was interested in. I could not have asked for more.

My time in Switzerland would not have been the same without a great social support system. I would like to thank all of my friends in Switzerland, from EPFL and beyond. Thanks for making this time such a great adventure.

Finally, I want to express my deep thanks and gratitude to my family. A PhD can sometimes be a selfish pursuit and I know it was not always easy to see me buried in work. I thank you for your patience and support and I hope to pay some of it back in the years to come. Thank you all.

Jerusalem, April 21, 2019

W. J. H.

## **Preface**

How many two-input gates are needed in a logic network to compute an arbitrary six-input Boolean function? How many majority-of-three operations suffice to compute the majority of nine Boolean variables? Precise answers to these seemingly tractable questions surprisingly do not exist. Exact synthesis describes a practical approach to tackle these difficult problems. Answers to the above and many more similar other questions have significant impact to state-of-the-art logic synthesis applications. However, until recently exact synthesis algorithms have mainly been used in order to strengthen theoretical upper bounds on circuit complexity results. Their intensive run-time requirements have rendered them infeasible in a robust scalable logic optimization flow.

In this thesis, Winston has thoroughly investigated exact synthesis and unfolded the existing proof-of-concept SAT-based algorithms into a robust methodology that enables practical application. To this end, he proposes solutions from various different angles. He motivates the careful study of encodings and symmetry breaking techniques in an elaborated experimental evaluation that compares various encodings—including a new one proposed in this thesis—and various symmetry breaking constraints.

The strongest contribution by Winston begins with the observation that exact synthesis essentially solves the two tasks of finding a logic network topology and assigning gate operators at the same time. The thesis shows that separating these tasks can significantly simplify the complexity of the problem and therefore lead to tremendous run-time improvements. The two tasks can be separated by preassigning topology information of the logic network. Such separations know two extremes: (i) not assigning any topology information which results in a single monolithic SAT problem which is difficult to solve; or (ii) assigning full topology information which results in many simple and easy to solve SAT problems, one for each possible topology—a number that quickly explodes already for a small number of gates.

Winston proposes two alternatives for non-trivial partial topologies that suggest a good compromise between the number of subproblems and their complexity. These are fences and partial dags. Both come with theory, practical algorithms, and experimental evaluations. Further, the partition into subproblems naturally enable parallel execution, which outperforms parallel SAT solving techniques that are not aware of the topology separation in the problem. All techniques that are described in this thesis are implemented in the open source C++ library percy. The quality of the library is quite remarkable. It will help researchers to extend the

state-of-the-art in SAT based exact synthesis and help practitioners to easily evaluate the impact of exact synthesis in existing logic optimization flows. This thesis marks the end of the fruitful PhD studies of Winston and the beginning of the field of practical exact synthesis techniques. They will shape the field of logic synthesis as did the emergence of algebraic and Boolean techniques in the past.

Montreux, April 21, 2019

Mathias Soeken

## **Abstract**

Today, the design of electronic systems is largely automated. The practice of using software automation technologies for the design of electronic hardware is commonly referred to as Electronic Design Automation (EDA). EDA comprises a large set of tools, from languages that specify high-level hardware designs, to software that determines the layout of nanoscale devices on an integrated circuit. Within this collection, an important role is played by so-called *logic synthesis* algorithms. A substantial field of research onto itself, logic synthesis can be roughly thought of as the problem of finding good representations for Boolean functions. Such functions are the backbone of digital circuits, which can be thought of, to a first approximation, as devices that compute with Boolean values. In other words, circuits can be viewed simply as large Boolean functions. Logic synthesis, then, is assigned the important task of finding good structural representations for such circuits. Choosing the right logic synthesis algorithm can have a significant impact on the efficiency of an electronic design.

Depending on one's reckoning, the development of logic synthesis tools can be traced back to Claude Shannon's famous 1937 master's thesis on switching circuits, or perhaps even further back to George Boole's seminal work from the 1800s on what is now known as Boolean algebra. Development of multi-level logic synthesis started some decades ago, in the late 1970s. Due to the complexity of multi-level logic synthesis, current algorithms are mostly based on heuristic methods.

In this thesis, we consider a special type of logic synthesis algorithm known as exact synthesis. Specifically, we analyze and develop multi-level exact synthesis algorithms based on a SAT formulation. Such algorithms attempt to solve a very difficult problem in which, given any Boolean function, they find the optimum (i.e. best possible) circuit that represents it. Our contributions can be roughly split into two parts: (i) core exact synthesis algorithms, and (ii) applications of exact synthesis. In the first part, we start by examining, in detail, different ways to encode the exact synthesis problem into CNF formulas. These formulas are given as input to SAT solvers, which solve them to find solutions. Finally, the solutions to these formulas can be decoded to obtain optimum Boolean circuits. We will compare and contrast the different encodings and show, quantitatively and experimentally, that a proper encoding can greatly influence the efficiency of exact synthesis algorithms. Next, we will show how such exact synthesis algorithms can be improved by adding domain-specific information. This information takes the form of families of DAG topologies which contain some additional

structure to guide the SAT solver in its search. Furthermore, using these DAG topology families, we show how the exact synthesis problem can be transformed into an embarrassingly parallel one. This essentially means that, as long as we have processors available, we can throw more and more parallel computing power at the problem to solve it more quickly. After analyzing and improving the core exact synthesis algorithm, we arrive at the second part of the thesis. In this part, we show how exact synthesis can be applied to different problems that are of both theoretical and practical interest. On the theoretical side, we show how exact synthesis can be used to classify Boolean functions in terms of their intrinsic difficulty. On the practical side, we introduce a new data structure and logic representation called XOR-Majority Graphs (XMGs). We use XMGs, in concert with exact synthesis, to develop a novel logic rewriting methodology which achieves significant improvements over the state-of-the-art. We then generalize this methodology into one that can be used to restructure arbitrary Boolean networks, again enabling new improvements in logic synthesis.

Overall, the contributions of this thesis show how exact synthesis can be improved and applied in the modern age of parallel hardware and software. We expect that it will be an essential part of any EDA toolbox in the years to come, during which design goals are likely to become even more ambitious than they have been in the past.

*Keywords:* electronic design automation, EDA, logic synthesis, exact synthesis, Boolean satisfiability, SAT, SAT solvers, formal methods.

## Zusammenfassung

Der Entwurf elektronischer Systeme ist heutzutage weitestgehend automatisiert. *Electronic Design Automation* (engl., etwa elektronische Entwurfsautomatisierung) ist das Gebiet, welches automatische Softwarelösungen zum Entwurf elektronischer Hardware verwendet. EDA beinhaltet eine große Anzahl an Werkzeugen, beginnend von Sprachen zur abstrakten Beschreibung von Hardwaremodellen, bis hin zu Software, die das konkrete Layout von Bauteilen im Nanobereich auf dem integrierten Schaltkreis berechnet. Als substantielles Teilgebiet beschreibt Logiksynthese das Problem gute Darstellungen für Boolesche Funktionen zu finden. Boolesche Funktionen sind essentiell für digitale Schaltkreise, welche als elektronische Systeme verstanden werden können, die mit Booleschen Wahrheitswerten rechnen. In anderen Worten können Schaltkreise auch als große Boolesche Funktionen verstanden werden. Die wichtige Aufgabe von Logiksynthese ist gute strukturelle Darstellungen für solche Schaltkreise zu finden. Die Wahl des Logiksynthesealgorithmus hat einen signifikanten Einfluss auf die Effizienz des zu entwerfenden elektronischen Systems.

Die Entwicklung von Logiksynthesewerkzeugen geht zurück auf Claude Shannon's berühmte Masterarbeit über *Switching Circuits*, vielleicht sogar auf George Boole's einführende Werke aus dem 19. Jahrhundert, die mittlerweile als Boolesche Algebra bekannt sind. Die Entwicklung effizienter Softwaretools begann in den späten 70er Jahren des letzten Jahrhunderts. Wegen der hohen Komplexität von Logiksynthesealgorithmen, basieren fast alle existierenden und derzeit verwendeten Methoden auf Heuristiken.

Diese Dissertation betrachtet *exakte* Synthese, eine spezielle Art von Logiksynthese. Wir betrachten insbesondere SAT-basierte exakte Synthesealgorithmen. Diese Algorithmen versuchen ein besonders schweres Problem zu lösen: finde die beste Darstellungen zu einer beliebigen Booleschen Funktion. Unser Beitrag umfasst grob zwei Teile: (i) Kernalgorithmen für exakte Synthese und (ii) Anwendungen exakter Synthese. Im ersten Teil untersuchen wir im Detail unterschiedliche Arten exakte Synthese als KNF Formeln zu kodieren. Diese KNF Formeln sind Eingaben für SAT Beweiser, welche erfüllende Lösungen zu den Formeln finden. Schaltkreise können aus den Lösungen dekodiert werden. Wir vergleichen verschiedene Kodierungen und stellen sie gegenüber, und zeigen quantitativ sowie experimentell, dass die Wahl der Kodierung einen starken Einfluss auf die Effizienz exakter Synthesealgorithmen haben kann. Anschließend zeigen wir wie exakte Synthesealgorithmen durch das Hinzufügen von domänenspezifischen Informationen verbessert werden können. Diese Informationen

beinhalten Mengen von Graphstrukturen, welche den Suchraum für die SAT Beweiser signifikant reduzieren können. Wir zeigen außerdem wie diese Graphstrukturen zur effizienten Parallelisierung des SAT Beweisers verwendet werden können. Im zweiten Teil der Dissertation zeigen wir wie exakte Synthesealgorithmen für verschiedene Probleme von praktischem und theoretischem Interesse verwendet werden können. Wir zeigen eine theoretische Anwendungen zur Klassifizierung Boolescher Funktionen basierend auf ihrer Komplexität. Als praktische Anwendung zeigen wir einen Optimierungsalgorithmus für XOR-Majority Graphen (XMGs), eine neue Logikrepräsentation. Die Ergebnisse dieses Optimierungsalgorithmus zeigen signifikante Verbesserungen gegenüber existierender Methoden. Zudem haben wir den Optimierungsansatz für generelle Boolesche Logiknetzwerke verallgemeinert.

Zusammenfassend zeigen die Beiträge dieser Dissertation wie exakte Synthese unter der Verwendungen moderner paralleler Hardware und Software eingesetzt sowie verbessert werden. Wir gehen davon aus, dass die vorgestellten Techniken ein essentieller Bestandteil zukünftiger EDA Softwarelösungen sein werden, um die immer zu ambitionierteren Hardwaresysteme effizient entwerfen zu können.

*Schlagworte:* Elektronische Entwurfsautomatisierung, Logiksynthese, exakte Synthese, Boolesches Erfüllbarkeitsproblem, SAT Beweiser, Formale Methoden

## Samenvatting

Het ontwerp van elektronische systemen is tegenwoordig grotendeels geautomatiseerd. De term *Electronic Design Automation* (EDA, Nederlands: elektronische ontwerpautomatisering) verwijst naar de tak van de informatica die zich bezighoudt met het ontwikkelen van softwareoplossingen voor het ontwerpen van elektronische hardware. EDA omvat een groot aantal hulpmiddelen, van talen waarmee we op een hoog niveau het gedrag van hardwareontwerpen kunnen omschrijven, tot software die op nanoschaal de concrete opmaak bepaald voor de bouwstenen van elektronische circuits. Een belangrijke onderdeel van EDA zijn de zogenaamde *logicasynthese*-algoritmes. Logicasynthese is een substantieel onderzoeksgebied waarin men probeert goede representaties van Booleaanse functies te vinden. Zulke functies zijn essentieel voor digitale apparaten, aangezien we deze kunnen beschouwen als apparaten die rekenen met Booleaanse waarden. Anders gezegd kunnen we digitale circuits simpelweg beschouwen als grote Booleaanse functies. Het doel van logicasynthese is het vinden van goede structurele representaties voor zulke circuits. De keuze voor het juiste logicasynthesealgoritme kan van grote invloed zijn op de efficiëntie van een elektronisch systeem.

De ontwikkeling van logicasynthesealgoritmes is terug te leiden naar Claude Shannon's beroemde masterscriptie uit 1937, of zelfs nog eerder naar het baanbrekende werk van George Boole uit de 19<sup>e</sup> eeuw waaruit het idee van de Booleaanse Algebra is ontstaan. De ontwikkeling van meer geavanceerde (en geautomatiseerde) algoritmes begon laat in de jaren zeventig van de 20<sup>e</sup> eeuw. Vanwege de enorme complexiteit van het fundamentele logicasyntheseprobleem zijn huidige algoritmes grotendeels gebaseerd op heuristieke methodes.

In dit proefschrift onderzoeken we een speciaal soort logicasyntheseprobleem dat bekend staat als *exacte* logicasynthese. We analyseren en ontwikkelen verschillende multi-level exacte logicasynthesealgoritmes die gebaseerd zijn op een SAT formulering. Deze algoritmes proberen een bijzonder moeilijk probleem op te lossen. Namelijk, gegeven een Booleaanse functie vinden zij het optimale (best mogelijke) circuit voor die functie. Onze bijdragen in dit proefschrift kunnen grofweg worden opgedeeld in twee onderdelen: (i) kernalgoritmes voor exacte logicasynthese en (ii) toepassingen van exact synthese. In het eerste gedeelte onderzoeken we verschillende manieren om het exacte syntheseprobleem te coderen als CNF formules. Deze formules worden aan SAT-oplossers ingevoerd die we vervolgens gebruiken om oplossingen te vinden. Tenslotte kunnen de oplossingen van deze formules gedecodeerd

worden om optimale circuits te vinden. We zullen verschillende coderingen met elkaar contrasteren en vergelijken. We zullen ook laten zien dat de keuze voor de juiste codering van grote invloed kan zijn op de efficiëntie van exacte synthesealgoritmes. Vervolgens laten we zien hoe deze algoritmes kunnen worden verbeterd door de toevoeging van domeinspecifieke informatie. Deze informatie neemt de vorm aan van families van DAG-topologieën welke extra structuur aanbrengen die de SAT-oplosser helpt bij het zoeken naar oplossingen. Bovendien kunnen deze DAG-topologieën gebruikt worden om parallelle exacte synthesealgoritmes te ontwikkelen. In essentie betekent dit dat, zolang we meer processoren tot onze beschikking hebben, we altijd meer computerkracht kunnen toevoegen om het probleem op te lossen. Na het analyseren en verbeteren van de kernalgoritmes komen we bij het tweede gedeelte van dit proefschrift. Hierin laten we zien hoe exacte synthese kan worden toegepast op verschillende problemen die zowel theoretisch en praktisch van belang zijn. Aan de theoretische kant laten we zien hoe exacte synthese gebruikt kan worden om Booleaanse functies te classificeren aan de hand van hun intrinsieke complexiteit. Aan de praktische kant introduceren we een nieuwe datastructuur en representatie: de zogenaamde XOR-Majority Graphs (XMGs). We gebruiken de combinatie van exact synthese en XMGs om een nieuw logica-herschrijvend algoritme te ontwikkelen dat aanzienlijk betere resultaten behaald ten opzichte van bestaande algoritmes. Daarna laten we zien hoe dit algoritme gegeneraliseerd kan worden. De generieke versie van ons algoritme kan worden gebruikt om verschillende soorten circuits te verbeteren, hetgeen een belangrijke stap is in de vooruitgang van dit type logicasynthesealgoritmes.

De bijdragen van dit proefschrift laten zien hoe exacte synthesealgoritmes verbeterd en toegepast kunnen worden in de moderne tijd van parallelle hardware en software. Onze verwachting is dat zij in de komende jaren een essentiële rol zullen spelen in veel EDA-oplossingen, vooral aangezien de ontwerpdoelen van hardwarefabrikanten alsmaar ambitieuzer worden.

*Trefwoorden:* elektronische ontwerpautomatisering, EDA, logicasynthese, exact synthesis, vervulbaarheidsprobleem, SAT, formele methoden.

# **Contents**

| Ac | knov  | wledgements                                | V    |

|----|-------|--------------------------------------------|------|

| Pı | eface | e                                          | vii  |

| Ał | ostra | ct (English)                               | ix   |

| Ał | ostra | ct (Deutsch)                               | xi   |

| Ał | ostra | ct (Nederlands)                            | xiii |

| Li | st of | figures                                    | xvii |

| Li | st of | tables                                     | XX   |

| 1  | Intr  | oduction                                   | 1    |

|    | 1.1   | Boolean Functions                          | 3    |

|    | 1.2   | Logic Synthesis                            | 4    |

|    |       | 1.2.1 Exact Synthesis                      | 10   |

|    | 1.3   | Motivation                                 | 11   |

|    | 1.4   | Thesis Contributions                       | 13   |

|    |       | 1.4.1 Encodings & Quantitative Comparisons | 14   |

|    |       | 1.4.2 DAG Topology Families                | 14   |

|    |       | 1.4.3 Parallel Synthesis                   | 14   |

|    |       | 1.4.4 Applications                         | 15   |

|    | 1.5   | Thesis Outline                             | 15   |

| Ι  | Cor   | re Algorithms                              | 19   |

| 2  | Syn   | thesis & Encoding                          | 21   |

|    | 2.1   | Background                                 | 22   |

|    |       | 2.1.1 Boolean Chains                       | 22   |

|    |       | 2.1.2 SAT-based Exact Synthesis            | 24   |

|    |       |                                            |      |

### **Contents**

|    |      | 2.1.3 A Note on Optimality                             | 26         |

|----|------|--------------------------------------------------------|------------|

|    | 2.2  | CNF Encodings                                          | 26         |

|    |      | 2.2.1 Single Selection Variable (SSV) Encoding         | 27         |

|    |      | 2.2.2 Multiple Selection Variables (MSV) Encoding      | 30         |

|    |      | 2.2.3 Distinct Input Truth Tables (DITT) Encoding      | 31         |

|    | 2.3  | Symmetry Breaking                                      | 34         |

|    | 2.4  | Quantitative Comparisons of CNF Encodings              | 37         |

|    | 2.5  | CEGAR                                                  | 42         |

|    | 2.6  | Synthesis With Don't Cares                             | 45         |

|    | 2.7  | Computational Complexity                               | 46         |

|    | 2.8  | Summary                                                | 50         |

| 3  | DAG  | Topology Families                                      | 51         |

|    | 3.1  | Introduction                                           | 51         |

|    | 3.2  | Fences                                                 | 52         |

|    | 3.3  | Partial DAGs                                           | 53         |

|    | 3.4  | Counting Dags, Fences, and Partial DAGs                | 55         |

|    | 3.5  | Generating Fences                                      | 57         |

|    |      | 3.5.1 Integer Partitioning Method                      | 57         |

|    |      | 3.5.2 Recursive Backtracking Method                    | 58         |

|    | 3.6  | Exact Synthesis Using Fences                           | 60         |

|    | 3.7  | Fence vs. Conventional Encodings                       | 63         |

|    | 3.8  | Synthesis With Partial DAGs                            | 64         |

|    | 3.9  | Topology-Based Parallel Exact Synthesis                | 65         |

|    | 3.10 | Topology-Based vs. Generic Parallelism                 | 66         |

|    | 3.11 | Majority-7 Decomposition                               | 68         |

|    | 3.12 | Summary                                                | 69         |

|    | _    |                                                        |            |

| II | Ap   | plications                                             | 71         |

| 4  |      | ction Classification                                   | <b>7</b> 3 |

|    | 4.1  | Introduction                                           | 73         |

|    | 4.2  | NPN Canonization                                       | 76         |

|    | 4.3  | Classification Method                                  | 78         |

|    |      | 4.3.1 Finding All NPN Classes                          | 78         |

|    |      | 4.3.2 Finding Minimum-Size Chains With Exact Synthesis | 79         |

|    |      | 4.3.3 Synthesis Upper Bounds                           | 82         |

|    | 4.4  | Experimental Results                                   | 82         |

|    | 4.5  | Summary                                                | 84         |

| 5  | Opt    | imizing XOR-Majority Graphs            | 85  |

|----|--------|----------------------------------------|-----|

|    | 5.1    | Introduction                           | 85  |

|    | 5.2    | Preliminaries                          | 86  |

|    |        | 5.2.1 Cut Enumeration                  | 86  |

|    |        | 5.2.2 Logic Rewriting                  | 89  |

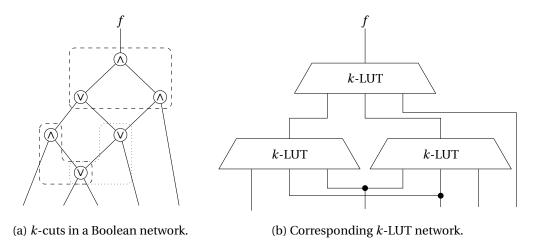

|    |        | 5.2.3 LUT Mapping                      | 94  |

|    | 5.3    | Contributions                          | 95  |

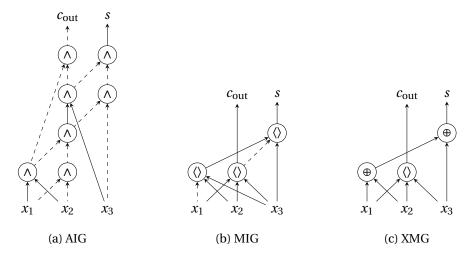

|    | 5.4    | XOR-Majority Graphs                    | 96  |

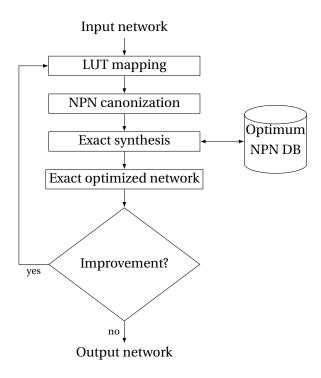

|    | 5.5    | Optimization Method Overview           | 98  |

|    |        | 5.5.1 Comparison to Previous Work      | 99  |

|    | 5.6    | Method Implementation                  | 100 |

|    |        | 5.6.1 Exact Synthesis                  | 100 |

|    |        | 5.6.2 XMG Size Optimization            | 103 |

|    | 5.7    | Experimental Evaluation                | 103 |

|    |        | 5.7.1 XMG Size Optimization            | 104 |

|    |        | 5.7.2 LUT Mapping                      | 105 |

|    |        | 5.7.3 Comparison To Best Known Results | 106 |

|    | 5.8    | Summary                                | 107 |

|    |        | 5.8.1 Future Work                      | 108 |

| 6  | Opt    | imizing Boolean Networks               | 109 |

|    | 6.1    | Introduction                           |     |

|    | 6.2    | Preliminaries                          |     |

|    | 6.3    | Cut Rewriting                          | 111 |

|    |        | 6.3.1 Efficiency Tricks & Don't Cares  |     |

|    | 6.4    | Experiments                            |     |

|    | 6.5    | Summary                                | 116 |

| _  | 0      |                                        | 115 |

| 7  |        | nclusions Thesis Contributions         | 117 |

|    | 7.1    | Thesis Contributions                   |     |

|    |        | Future Work and Open Problems          |     |

|    | 7.3    | Final Remarks                          | 121 |

| A  | per    | cy: an exact synthesis library         | 123 |

|    | A.1    | Code Examples                          | 124 |

|    | A.2    | A Note on Correctness                  | 129 |

| Bi | bliog  | graphy                                 | 131 |

| Cı | ırricı | ulum Vitae                             | 145 |

|    |        |                                        |     |

# List of Figures

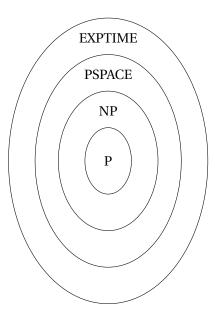

| 1.1 | A conceptual representation of some important complexity classes                                      | 3  |

|-----|-------------------------------------------------------------------------------------------------------|----|

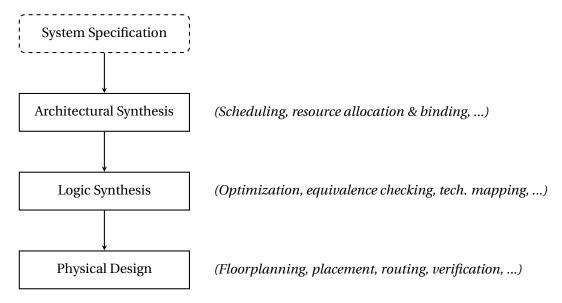

| 1.2 | Example of a simplified EDA flow.                                                                     | 5  |

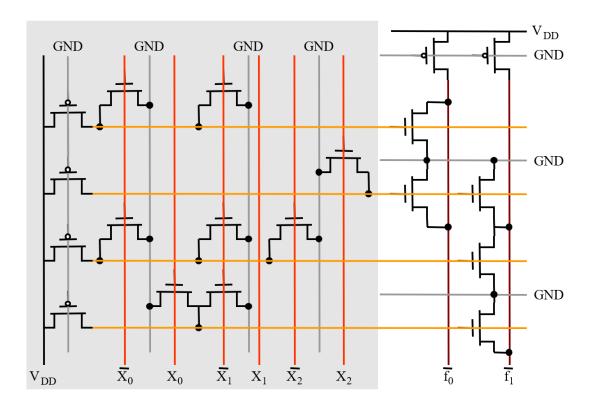

| 1.3 | Schematic illustration of a simple NMOS PLA. Courtesy of Professor Jan M. Rabaey.                     | 7  |

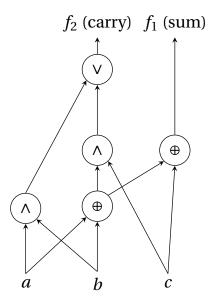

| 1.4 | Illustration of a bound heterogeneous Boolean logic network for a full adder                          | 9  |

| 1.5 | A logic rewriting flow. Optimization of the subnetworks may be achieved in vari-                      |    |

|     | ous ways, such as database retrieval, heuristic decomposition, or exact synthesis.                    | 12 |

| 2.1 | Illustration of an optimum Boolean chain for a full adder                                             | 23 |

| 2.2 | Illustration of a basic size-optimum SAT-based exact synthesis algorithm                              | 25 |

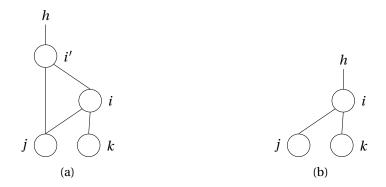

| 2.3 | Examples of circuit topologies that are avoided by applying symmetry break (A).                       | 35 |

| 2.4 | Illustration of the kinds of circuit structures avoided by symmetry break (R)                         | 35 |

| 2.5 | Illustration of symmetries avoided by the (co)-lexicographical symmetry break.                        |    |

|     | Using (C), the topology in (a) would not be valid, whereas the one in (b) would be.                   | 36 |

| 2.6 | Illustration of symmetries avoided by symmetry break (S). In the topology on the                      |    |

|     | left, we have switched variables $x_3$ and $x_4$ . Although both topologies are nearly                |    |

|     | identical minimum-size implementations of $f$ , (a) is invalid under (S), since $x_3$                 |    |

|     | must be used before $x_4$                                                                             | 37 |

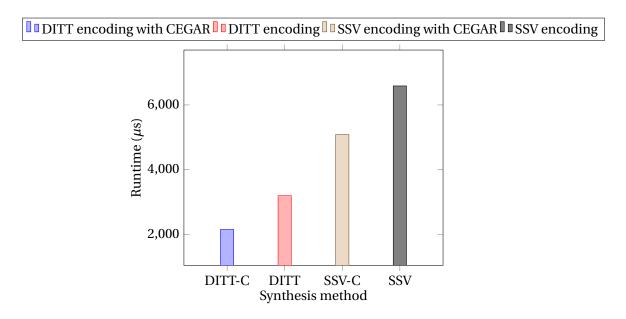

| 2.7 | An illustration of the impacts of CEGAR on synthesis runtime                                          | 45 |

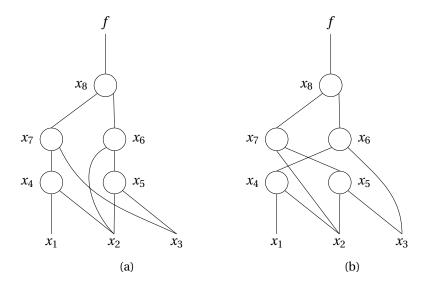

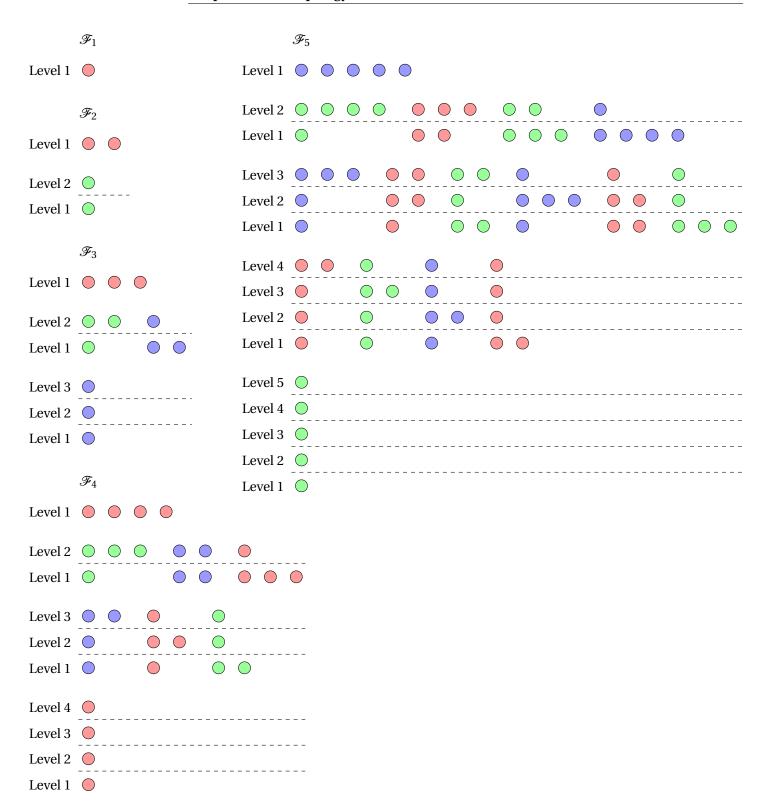

| 3.1 | Illustrations of the first five fence families                                                        | 54 |

| 3.2 | On the left an example of partial DAG specified by the sequence below. Unspec-                        |    |

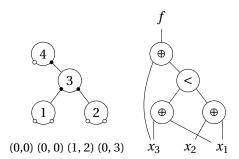

|     | ified fanins are signified by empty circles. On the right a fully specified chain                     |    |

|     | found by the SAT solver for the function $f = \langle x_1 x_2 x_3 \rangle$                            | 55 |

| 3.3 | The fence $F$ in (a) corresponds to a set of possible DAG topologies and can                          |    |

|     | thus be used to constrain the SAT solver's search. For instance, Figure (b) and                       |    |

|     | Figure (c) satisfy the constraints from <i>F</i> . Figure (d) does not. Each node on level            |    |

|     | $\lambda$ must have at least one fanin from level $\lambda-1$ ; this follows by definition of levels. | 62 |

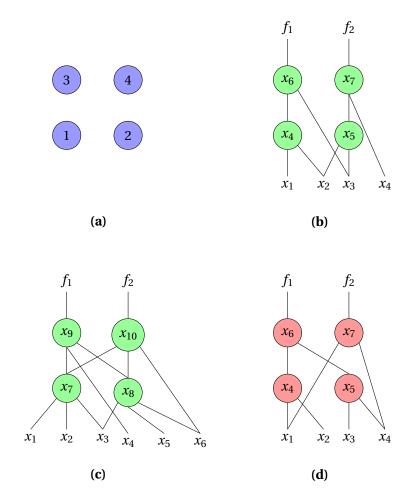

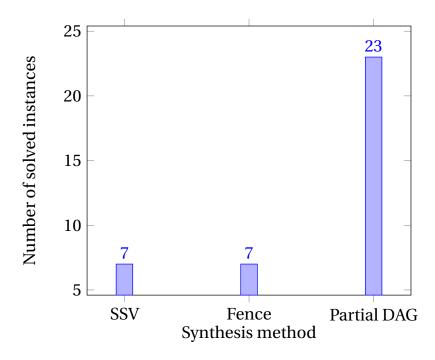

| 3.4 | Shows, for a set of 500 hard benchmarks, the number of successfully synthesized                       |    |

|     |                                                                                                       | 65 |

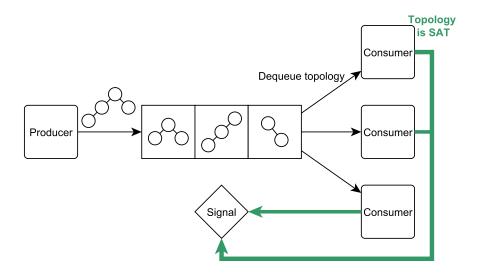

| 3.5 | Shows how topology information may be used to create an embarrassingly                                |    |

|     | parallel exact synthesis pipeline                                                                     | 66 |

### **List of Figures**

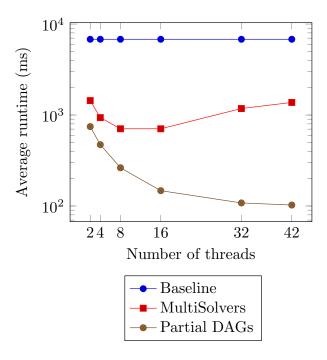

| 3.6        | A comparison between our domain-specific parallelism and a generic parallel SAT backend.                                                                                   | 67  |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.7        | Illustration of the super-linear speedup achievable by topology-based parallel synthesis                                                                                   | 68  |

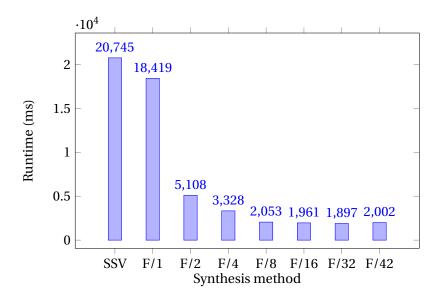

| 3.8        | Comparison of majority-7 decomposition between the best SSV encoding and a fence-based encoding with an increasing number of threads                                       | 69  |

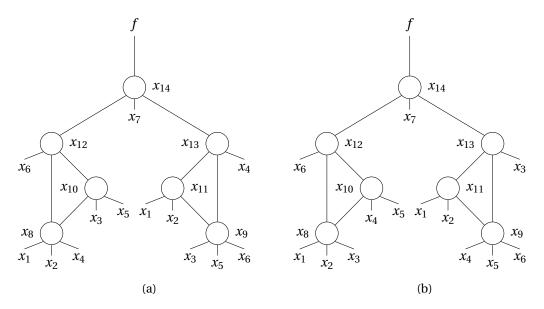

| 4.1        | An example of two different functions that are P-equivalent. The circuit in (a) can be made equivalent to the one in (b) by permuting the inputs                           | 76  |

| 4.2        | An example of two different functions that are NPN-equivalent. The circuit in (a) can be made equivalent to the one in (b) by negating its output and permuting the inputs | 76  |

| 4.3        | We can implement any 4-input Boolean function by using at most three 3-input operators.                                                                                    | 82  |

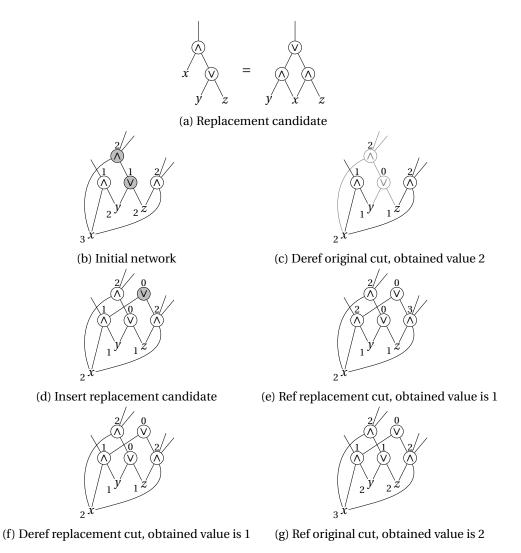

| 5.1        | Estimating the gain of a replacement cut using reference counting                                                                                                          | 91  |

| 5.2<br>5.3 | Any $k$ -feasible cut can be implemented by a single $k$ -LUT. In this example $k=3$ . Size-optimum full adders, given in AIG, MIG, and XMG representations, respec-       | 94  |

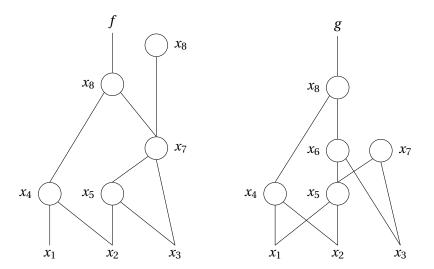

|            | tively. Dashed lines indicate complemented edges. We see that $\sigma(a) \le \sigma(b) \le \sigma(c)$ .                                                                    | 97  |

| 5.4        | An overview of the optimization flow                                                                                                                                       | 98  |

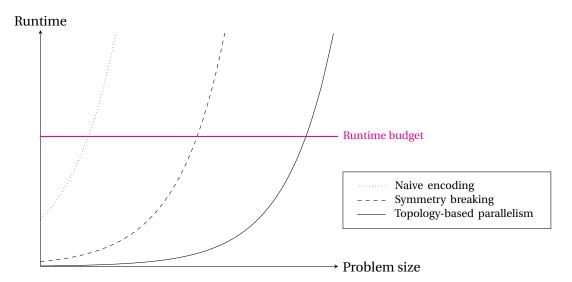

| 7.1        | Even without an exponential speedup, we can make SAT-based exact synthesis more practical through techniques such as symmetry breaks and topology-based parallelism.       | 118 |

# **List of Tables**

| 1.1 | Notation for some commonly used Boolean operators                                                                                                               | 5   |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.1 | Impact of symmetry breaking on the space of 4-input functions for 2-input operator chains. Sorted by average synthesis time. All times reported in $\mu s$      | 40  |

| 2.2 | Impact of encoding and symmetry breaking for 5-input functions with 3-input operator chains                                                                     | 41  |

| 2.3 | Impact of encoding and symmetry breaking for 6-input functions with 4-input operator chains                                                                     | 42  |

| 3.1 | Comparing the numbers of DAGs, partial DAGs, and fences for increasing num-                                                                                     |     |

|     | bers of vertices                                                                                                                                                | 57  |

| 3.2 | Comparing fence- and partial DAG-based synthesis to conventional state-of-the-art encodings. All runtimes in ms                                                 | 64  |

| 4.1 | Combinational complexity of all 4-input functions using 2-input operators [69]                                                                                  | 75  |

| 4.2 | Combinational complexity of all 5-input functions using 2-input operators [69]                                                                                  | 75  |

| 4.3 | Comparing the number of $n$ -input functions and NPN classes. Numbers of NPN classes taken from [127]. We write the numbers for $n = 8$ in scientific notation, |     |

|     | as they would not fit on the page otherwise                                                                                                                     | 78  |

| 4.4 | Combinational complexity of all 4-input functions using 3-input operators                                                                                       | 83  |

| 4.5 | Combinational complexity of all 5-input functions using 3-input operators $$ . $$                                                                               | 84  |

| 5.1 | Comparing XMG and AIG size optimization                                                                                                                         | 105 |

| 5.2 | Comparing 6-LUT Mapping for XMGs and AIGs                                                                                                                       | 106 |

| 5.3 | Comparing Best XMGs To Best Known 6-LUT Mapping Results                                                                                                         | 107 |

| 6.1 | Cut rewriting experimental results for 3-LUT resynthesis                                                                                                        | 115 |

| 6.2 | Cut rewriting experimental results for 4-LUT resynthesis                                                                                                        | 115 |

## 1 Introduction

Electronic systems are ubiquitous, and their presence in the world is only increasing. Moreover, there is a trend towards increasing design complexity across multiple levels of abstraction. For example, on the device level, novel technologies such as quantum-dot cellular automata and spin-wave devices pose different problems than those encountered in conventional CMOS [80, 120]. Designs using such technologies must make efficient use of novel logic primitives, while accounting for complex constraints such as fanout or depth restrictions [141]. On the architectural level, there has been a trend towards system on a chip (SoC) design. SoCs integrate various components such as CPUs, memories, video decoders, and sensors on a single substrate [109]. Communication between SoC components is challenging and has led to the so-called *network on chip* (NoC) design paradigm [16]. With the advent of the Internet of Things (IoT), many devices must be able to sense, signal, or otherwise interact with their environments, often under tight energy constraints [145]. The design of IoT systems is particularly challenging as it involves, besides issues such as device and network architecture, also far-reaching privacy and security concerns [73]. Finally, to remain economically viable, reducing time-to-market is an important design target for many systems. Introducing new products faster than the competition has many advantages: it affects both cost and potential market value, allows companies to set technical standards, and enables them to respond more quickly to customer feedback [149].

Given the complexity of current systems, it is no longer feasible to create full error-free designs in a cost-effective time frame, even by large teams of human designers. Indeed, this has not been feasible for several decades [88, p. 5]. The goal of *electronic design automation* (EDA) is to aid human designers by providing techniques to automate large parts of the design process. Over the years, sophisticated methods for synthesis, test, and verification have been developed. These are applicable to various design stages, such as architecture level synthesis, logic synthesis, and physical design. In this thesis, we analyze and develop logic synthesis techniques based on *Boolean satisfiability* (SAT).

The *Handbook of Satisfiability* identifies two key roles of SAT: (i) reasoning about propositional logic formulas, and (ii) solving combinatorial problems [19, p. v]. Propositional logic is the study of propositions that may be *true* or *false*, as well as the logical connectives that are used to compose them. SAT refers to the problem of determining whether or not a proposition can ever by true (i.e. satisfied). We can use SAT to elegantly describe problems in declarative way. Furthermore, it serves the role of an efficient and generic computational substrate.

We are often faced with the task of deciding if some combinatorial object has a certain property. Such tasks are known as *decision problems*. Now, one might object that the notions of "combinatorial object" and "property" are ill-defined here. However, this is not without reason: their rigorous definition requires quite some work. This becomes perhaps easier to understand when one imagines the wide range of possibilities. For example, we may want to know if a graph can be colored with a certain number of colors, or if we can pack a knapsack while not exceeding a certain weight. To avoid being bogged down in technical details, we allow ourselves to be less than rigorous here. We do not require the reader to be deeply familiar with the theory of computation, but refer the interested reader to Sipser's *Introduction to the Theory of Computation* if any technical questions do arise [126].

Given a combinatorial object, and a property, in many cases there exists a natural translation to a propositional formula, such that the formula is satisfiable if and only if the object has the property. Technically, such translations called reductions from one decision problem to another [126]. There is a deep technical reason for why such reductions from combinatorial problems to SAT often exist. In 1971, Cook showed that SAT has a property which is now commonly known as NP-completeness [38]. A a consequence of this, all decision problems in the class NP can be reduced to SAT, with only polynomial runtime overhead. In other words, we can use SAT as a general purpose compute engine to solve a large class of decision problems. When we say large, note that NP contains all problems that can be solved in polynomial time on a non-deterministic Turing machine. Equivalently, these are problems whose solutions can be checked in polynomial time. Thus, NP includes problems ranging from primality testing to graph coloring, and from job scheduling to equivalence checking. Indeed, many problems that we are faced with on a daily practice are contained in NP. Figure 1.1 shows representation of some important complexity classes and the relations between them. Famously, it is currently unknown if P = NP. However, due to the time hierarchy theorem we know that  $P \subseteq EXPTIME$ .

In recent years, there has been a lot of progress in the development of so-called SAT solvers. These are programs which specialize in solving SAT problems efficiently. Due to the NP-complete nature of SAT, fast solvers allow us to solve many problems in NP efficiently. Hence, as these solvers have become more powerful, interest in them has grown accordingly. In the context of *Electronic Design Automation* (EDA), the main application of SAT has traditionally been in hardware verification and other formal tasks.

Figure 1.1 – A conceptual representation of some important complexity classes.

In this thesis, we examine the reduction of multi-level logic synthesis to SAT. Indeed, it turns out that there exist a number of natural ways to encode the the synthesis problem as SAT formulae. <sup>1</sup> In fact, logic synthesis can often be viewed as an optimization problem, which is different from a decision problem. However, as we will see, logic synthesis and optimization can be reduced to solving sequences of SAT problems. The research question that this thesis attempts to answer can be summed up as: "*Can SAT be used as an efficient engine for the synthesis of multi-level logic networks, and if so, how?*". We present various SAT encodings of the synthesis problems as well as different techniques for solving it efficiently.

### 1.1 Boolean Functions

The main object of study in this thesis is the Boolean function. As noted by Ryan O'Donnell in his book *Analysis of Boolean Functions*, Boolean functions are perhaps the most basic objects in computer science [103]. However, their applications range from combinatorics, random graph theory, and statistical physics, to Gaussian geometry, and social choice theory. For these reasons, we take some time to introduce some terminology here.

A completely specified Boolean function f is a mapping between two Boolean spaces. We denote this by  $f: \mathbb{B}^n \to \mathbb{B}^m$ . Such functions are commonly known as multiple-output Boolean functions, with n inputs and m outputs. In the context of logic synthesis,  $\mathbb{B}$  is usually defined to be  $\{0,1\}$ . Generally,  $\mathbb{B}$  could contain any two distinct objects which obey Huntington's

<sup>&</sup>lt;sup>1</sup>Note that this may be viewed as comparing the efficiency of different reductions.

postulates for Boolean algebras [88, p. 67]. Because the n-dimensional space  $\{0,1\}^n$  can be visualized as the unit cube in n dimensions, it is commonly referred to as the n-dimensional hypercube. Points in the n-dimensional Boolean space correspond to the vertices of the cube. Such points may be represented by n-dimensional vectors, which are commonly known as minterms. Note that a Boolean function is a map between minterms. There are  $2^n$  minterms, and hence  $2^{m2^n}$  complete Boolean functions from  $\mathbb{B}^n$  to  $\mathbb{B}^m$ . It is sometimes convenient to use a vector notation to represent minterms. We write  $(x_1, x_2, ..., x_n)$  to an n-dimensional minterm vector.

In logic synthesis it is often the case that, under certain conditions, we do not care what the output of a function is. We call these *don't care* conditions. Such conditions may occur when the value of a sub-circuit cannot be observed at the global circuit outputs, or when certain input patterns are never activated. To support synthesis of such functions, we can extend the definition of Boolean function as a mapping from a Boolean space to an augmented Boolean space which also contains a special don't care element, often represented by \*. Using this extended definition we denote the mapping by  $f:\{0,1\}^n \to \{0,1,*\}^m$ . In other words, to signify that we don't care about a certain minterm, we map it to the \* element.

The don't care conditions of a function can be viewed as a set of minterms, or equivalently, as a function. Following the convention of [88], we do not distinguish between either view. Suppose function f = abx + a'cx has a don't care set that is specified by the function DC = ab'x + a'x'. We can then use this information to simplify and obtain f = ax + a'x. We call the minterms covered by DC the *don't care set*. Conversely, all minterms not covered by DC are part of the *care set*.

*Notation*. Throughout this thesis, we will use a number of Boolean operators quite frequently. For completeness, we define their notation here in Table 1.1. All of these operators are associative, so we typically do not write brackets. Following Knuth, we use angular bracket notation for the majority operator. We use two different variable naming schemas, depending on which is more convenient in a given context. Variables are denoted by either x's and indexed by numbers (such as  $x_1$ ,  $x_2$ ), or by lowercase letters of the alphabet, starting from a (i.e a, b, c).

### 1.2 Logic Synthesis

Logic synthesis can be summed up as the search for representations of Boolean functions. Typically, this search takes into account certain desirable properties of the representation, such as its size, depth, or estimated energy consumption. EDA algorithms can be partitioned into the three broad categories of architectural synthesis, logic synthesis, and physical design [88, 144]. Thus, logic synthesis is one of the most important steps in most EDA flows, and synthesizing efficient logic representations can significantly affect the final result. This parti-

| Operator                  | Symbol                   | Example Usage                                    |

|---------------------------|--------------------------|--------------------------------------------------|

| 2-input AND               | ٨                        | $x_1 \wedge x_2$                                 |

| 2-input OR                | V                        | $x_3 \vee x_4$                                   |

| 2-input EXOR              | $\oplus$                 | $x_5 \oplus x_6$                                 |

| 2-input Less-than         | <                        | $x_7 < x_6 \Leftrightarrow \bar{x}_7 \wedge x_6$ |

| Arbitrary binary operator | 0                        | $x_1 \circ x_2$                                  |

| 3-input MAJORITY          | $\langle \cdots \rangle$ | $\langle abc \rangle$                            |

| 5-input MAJORITY          | $\langle \cdots \rangle$ | $\langle abcde \rangle$                          |

| <i>n</i> -input MAJORITY  | $\langle \cdots \rangle$ | $\langle x_1 x_2 \cdots x_n \rangle$             |

Table 1.1 – Notation for some commonly used Boolean operators.

Figure 1.2 – Example of a simplified EDA flow.

tioning of EDA algorithms is an approximation: besides synthesis algorithms, these categories also contain algorithms for tasks such as verification and test. In this thesis we consider only *combinational* logic synthesis, which is the synthesis of circuits without memory elements. Figure 1.2 shows an example of a simplified EDA flow. Typically, hardware designs are specified in some *hardware description language* (HDL). This HDL description then gets compiled into increasingly concrete and low-level representations until finally a physical description is realized, which can then be manufactured.

The number of levels in a logic representation refers to the maximum depth of operators allowed within the representation. This notion of depth can be defined for any algebraic expressions, whether these expressions are Boolean or not. Consider the following two algebraic

expressions:

$$f = a \cdot b + f \cdot g \qquad \qquad g = a(b + c(d + e \cdot f)) \tag{1.1}$$

Expression f applies an addition operator to two product operators. Hence, it has an operator depth of two and is considered a two-level expression. Similarly, expression g is a four-level expression.

Synthesis of logic representations with many levels is known as *multi-level logic synthesis*. The limiting case of multi-level synthesis is a representation consisting of only two logic levels (note that one-level synthesis is trivial). Such representations often have a more simple and regular structure, which lends itself to be exploited by efficient and specialized algorithms. Due to their specialized nature, we commonly distinguish them from the general case as *two-level logic synthesis* algorithms. This thesis is primarily concerned with the use of SAT in multi-level logic synthesis, but for completeness, and to introduce the required terminology, in this section we briefly present both classes.

In addition to the classification into two-level and multi-level logic synthesis, we typically distinguish between exact and heuristic logic synthesis algorithms. Exact algorithms can be used to find optimum logic representations, whereas heuristic algorithms are used to find solutions that are some approximation of the optimum. The use of the term *exact* is due to the historical development of this area in logic synthesis. It can be viewed as referring to the ability to exactly satisfy certain cost criteria in a given logic representation. This will be made more concrete below. Some readers may find the phrase optimal algorithm more familiar or suitable. Optimization in the two-level domain is often referred to as *minimization*.

The typical abstraction in the two-level domain is the *expression form*. There are multiple such forms, corresponding to various types of two-level logic representations. A common one is the *sum of products* (SOP) form. Many readers will have come across this representation before. SOPs can be written as a normal algebraic expressions, although the rules for manipulating them are different, as they must satisfy the axioms of Boolean algebra. Any Boolean function can be expressed as the sum of products of literals, where a literal is a variable or its negation. In SOPs, addition corresponds to the logical disjunction operator  $\vee$  and products correspond to the conjunction operator  $\wedge$ . Thus, we would write the function  $f(x_1, x_2, x_3) = x_1 \wedge x_2 \vee \bar{x}_2 \wedge x_3$  as  $x_1 \cdot x_1 + \bar{x}_2 \cdot x_3$ , or even more succinctly as  $x_1 x_2 + \bar{x}_2 x_3$ . Expression f in Equation 1.1 is another example of an SOP expression. Other popular two-level representations exist. For example, the *product of sums* (POS) representation is the conceptual dual of the SOP representation. The *exclusive sum of products* (ESOP) representation replaces the disjunctions in the SOP representation by exclusive-OR operators. ESOPS can represent important classes of Boolean functions more compactly than SOPs [117].

Figure 1.3 – Schematic illustration of a simple NMOS PLA. Courtesy of Professor Jan M. Rabaey.

Historically, two-level logic minimization was born out of a need to optimize *programmable-logic arrays* (PLAs). A PLA is an electronic component which consists of an array of transistors that are aligned in rows. Each row in a PLA can be viewed as a product term, and each column in the array as an input or output variable. See Figure 1.3. Thus, by minimizing the number of product terms and literals in an SOP expression, we reduce the number of rows and transistors needed in the PLA representation of a function. Over the years, many exact and heuristic two-level minimization algorithms have been developed for SOP, POS, and ESOP representations. While the first of these algorithms dates back to the 1950s, some are still used in practice today. Notable examples are the heuristic SOP minimizer ESPRESSO, and the ESOP minimizer EXORCISM. An overview of these methods is outside of the scope of this thesis, but we refer the interested reader to [108, 85, 24, 106, 118, 136, 137, 91]. As a reference, many of these techniques are also described in [88].

Circuits are often designed as a composition of logic gates. Connecting these gates over multiple levels provides a flexibility that is not achievable by two-level logic representations, allowing for circuits designs with less area and delay. This is in large part due to the sharing of logic that can only be achieved by connections across multiple levels [26]. Logic synthesis

in this paradigm is commonly referred to as multi-level logic synthesis. Although generally beneficial, a drawback of multi-level synthesis is its increased complexity as compared to two-level synthesis.

Whereas in two-level logic the main abstraction is the expression form, in multi-level logic it is the notion of a *logic network*. Multiple models of logic networks exist, just as there are different expression forms. Recent years have seen a rise in the popularity of homogeneous logic networks such as and-inverter graphs (AIGs) and majority-inverter graphs (MIGs) [23, 7]. Such networks consist of a single type of gate. This gate type may be functionally complete; i.e. it may be composed to compute arbitrary Boolean functions. For example, NAND networks are built from a single such operator. AIGs and MIGs, on the other hand, are built from AND and MAJORITY operators, respectively. Since these operators can only implement monotone functions, we typically allow for the use of complemented edges in order to implement inversion. The simplicity of homogeneous networks allows for the creation of efficient data structures and optimization algorithms. This becomes particularly useful as the size and complexity of practical circuits continue to scale. So-called heterogeneous logic networks, on the other hand, allow different gate types to be used throughout the network [26, 88]. Common gate types correspond to the (N)AND/(N)OR/INV operators that are well-known from Boolean algebra. In the class of homogeneous logic networks, we can make a further distinction distinguish between bound and unbound networks. Bound networks allow only a fixed set of Boolean operators to be used as gate types. Unbound logic networks allow gates to implement arbitrary Boolean functions. In that case, local gate functions are often represented by some other common logic representation such as SOPs. Finally, there is a notable class of canonical multi-level representations. Canonicity refers to the fact that any two of such representations are equal if and only if the underlying functions they represent are the same. The main example is the binary decision diagram (BDD). Originally proposed by Lee and Akers, Bryant extended their work by showing how BDDs could be reduced and manipulated into canonical form, as well as how they could be implemented efficiently. His work resulted in the popularization of BDD-based logic synthesis and verification algorithms [79, 3, 27].

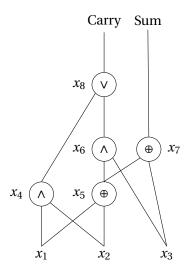

It is common to view multi-level logic networks as *directed acyclic graphs* (DAGs). In this view nodes (vertices) in the DAG correspond to gates in a circuit. Arcs between nodes represent wires between gates. The primary inputs and outputs of the circuit are represented by nodes that have no fanin and no fanout, respectively. Figure 1.4 shows an example. The operators allowed in this example are the set of all 2-input Boolean operators. Note that the vertices are labeled with the Boolean operators corresponding to the gate functions.

As in two-level logic, there exist both exact and heuristic optimization methods for multi-level logic. Exact methods have not been widely used in practice due to their prohibitively high computational complexity [88, p. 343]. In practice, a wide range of heuristic methods

Figure 1.4 – Illustration of a bound heterogeneous Boolean logic network for a full adder.

is applied instead. We briefly mention some of them here. Algebraic methods dispense with the Boolean abstraction and minimize Boolean expressions as though they are ordinary algebraic expressions. This assumption allows these method to be simple and fast. However, they are suboptimal, as they cannot take into account the additional flexibilities allowed by Boolean algebra. As a counterpoint, Boolean methods have been developed, which take into account don't care conditions that are, for example, induced by the structure of the logic network. Boolean methods exploit the properties of Boolean logic more fully than algebraic optimization do. As such, they can be used to reach more optimal solutions, at the expense of some runtime overhead. There is also a wide range of heuristic decomposition methods. These may be applied in throughout a logic network to restructure local sections For detailed descriptions of these methods and more, please refer to [25, 26, 123, 88, 23, 7, 8].

Notwithstanding the classification into two- and multi-level logic, other classes of logic representation do exist and have been studied. For example, there is a notable literature on EXOR based logic minimization using sum of pseudoproduct (SPP) expressions [82, 18]. SPPs are three-level logic expressions in which the two-level concept of cubes is generalized to pseudocubes, which are products of EXOR factors. A k-SPP is an SPP that has EXORs with k-bounded fanin [31]. Three-level forms such as SPPs and k-SPPs have the advantage that they can represent functions more compactly than two-level forms such as (E)SOPs. Exact and heuristic algorithms to minimize such expressions have been developed. We refer the interested reader to [82, 31, 18].

### 1.2.1 Exact Synthesis

Exact synthesis is a term used by the logic synthesis community for any method that can be applied to yield *exact* results for logic synthesis problems. In this context, the term exact synthesis is not used in opposition to approximate synthesis, which is a paradigm concerned with the synthesis of systems that produce approximately correct results [87]. Rather, exact synthesis refers to synthesizing logic representations that *exactly meets a specification*. For example, given a Boolean function  $f: \mathbb{B}^n \to \mathbb{B}^m$  and an number  $r \in \mathbb{N}$  we may ask

$\mathcal{Q}_1$ : "Does there exist a logic network N such that N implements f with exactly r gates?"

or

$\mathcal{Q}_2$ : "Does there exist an SOP expression *E* with exactly *r* cubes that represents f?"

An exact synthesis algorithm can be used to answer such questions. Typically, we are interested in constructive algorithms. In other words, if a question  $\mathcal{Q}_x$  can be answered in the affirmative, we would like to know what is the actual logic representation that meets the specification. In the above examples, we would like our algorithm to produce a logic network N or an SOP expression E.

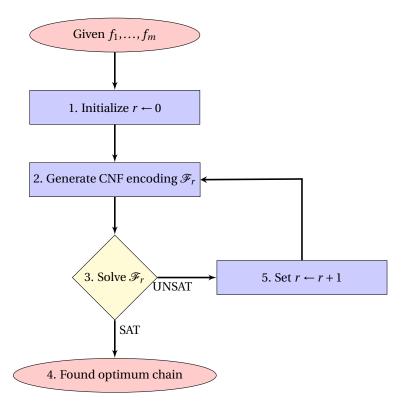

The notion of exactness is closely related to that of *optimality*, although it is strictly speaking different. Given an algorithm for the exact synthesis of some representation form, we can often adapt it to synthesize optimum representations. Suppose we have a constructive algorithm for  $\mathcal{Q}_1$ . We could then use it to synthesize size-optimum logic networks as follows. Initialize r to zero and query the algorithm. Increment r until we find the first value r' for which the algorithm reports success. This r' must then be the size of the smallest, i.e. size-optimum, logic network for f. Due to the close correspondence between exact- and optimum synthesis, in logic synthesis literature the terms are often used interchangeably. In practice, the term exact synthesis is widely used to refer to the synthesis of optimum representations.

Exact synthesis algorithms exist for both two- and multi-level logic representations. The Quine-McCluskey algorithm and Petrick's method are well-known algorithms for the minimization of SOPs [108, 85]. Similar methods have been developed for so-called ESOPs as well [117]. In multi-level logic synthesis we encounter various exact minimization algorithms. For instance, Davidson created an algorithm to find the exact minimum NAND decomposition of arbitrary functions [41]. In [77], Lawler generalizes the notion of prime implicant to multi-level logic and develops an exact multi-level optimization algorithm based on that abstraction. In 1962, Roth

and Karp proposed a general-purpose decomposition technique [113], generalizing the earlier work by Ashenhurst [11]. They also showed how this decomposition method may be used as the basis for an search algorithm that find optimum circuits. More recently, enumeration-based techniques have been developed independently by Knuth and Amarù [69, 10]. In practice, heuristic methods are often preferred for performance reasons [44]. The heuristic counterparts to two-level exact synthesis are the ESPRESSO and EXORCISM algorithms [26, 136].

### 1.3 Motivation

SAT-based exact synthesis has various practical as well as theoretical applications. Practical applications range from logic optimization, technology mapping, and synthesis for emerging technologies to less obvious ones such as cryptography [96, 53, 131, 132, 133, 139]. All of these can be considered as motivations for this work. In this section, we describe some of the motivations for exact synthesis in general, as well as SAT-based synthesis in particular, in more detail.

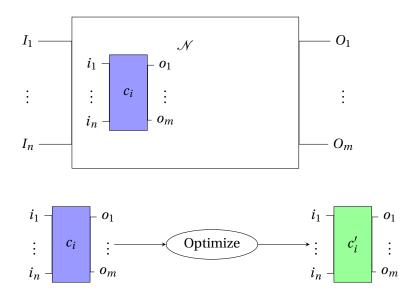

A major class of multi-level logic optimization algorithms are known as logic rewriting algorithms. We provide a brief description here, and a more detailed one in Section 5.2. In these algorithms, a logic network is restructured by replacing small subnetworks by their optimized counterparts. Typically, the network is partitioned into subnetworks through a process of cut enumeration [37, 81, 98]. A cut of a node n can be defined as a set of nodes c such that any path from the network inputs through n must contain a node in c. Thus, a cut defines a, possibly reconvergent, *logic cone* rooted at n. Cuts implementation may be implemented very efficiently [98], and is therefore a commonly used technique for dissecting out a subnetworks. In rewriting algorithms, optimization of subnetworks is commonly achieved by precomputing a database of highly optimized (or even optimum) networks for some small set of functions, or classes of functions. For example, it is easy to compute and store the 222 NPN classes for all 65,536 single-output 4-input functions [50, 15]. With such a database one can construct a fast optimization algorithm which iterates over the logic network, visiting subnetworks in topological order, iterating over their cuts, and matching them with their optimized versions in the database [93]. Figure 1.5 shows what such a synthesis flow might look like. Global optimization of the logic network  $\mathcal N$  is achieved by local optimizations of its subnetworks. Note that, in principle, the global optimization flow is independent how local optimization is achieved. Although subnetworks could be retrieved from a precomputed database, they may just as well be computed at runtime by an arbitrary optimization algorithm.

A drawback of conventional logic rewriting algorithms is that only a relatively small number of functions can be stored in a database for retrieval. This means that we are limited to rewriting only small subnetworks, such as subnetworks with up to 4 inputs. This problem is exacerbated when we want to want to rewrite subnetworks with multiple outputs (i.e. windows), or when

Figure 1.5 – A logic rewriting flow. Optimization of the subnetworks may be achieved in various ways, such as database retrieval, heuristic decomposition, or exact synthesis.

we want to take don't care conditions into account. An efficient exact synthesis algorithm allows us to rewrite larger parts of the network, thus achieving a more global optimization of the overall logic network [53].

Another major driver of exact synthesis is the emergence of novel device technologies, including post-CMOS technologies. Many devices based on emerging nanotechnologies have different behavior than those encountered in CMOS. For instance, they may inherently support different logic primitives than the conventional (N)AND/(N)OR/INV paradigm, such as the majority operator. Examples of are nanoelectromechanical (NEM) relays, spin-wave devices, and quantum-dot cellular automata [78, 120, 80]. Synthesis methods which take full advantage of these primitives can achieve significantly better results [72, 51].

Besides supporting exotic logic primitives, novel technologies may be subject to complex constraints. For example, some emerging technologies do not support inversion in an efficient way, have restrictions on datapath depth, or limited fanout capabilities [141]. In a scenario where solutions must obey such constraints, heuristic algorithms may be too weak. They may find a solution that satisfies the constraints, but they may also fail. Moreover, the failure of a heuristic algorithm to find a solution is no proof of the non-existence of such a solution. The solution may simply be outside the reach of a particular heuristic. In such scenarios, SAT-based exact synthesis compares favorably to both heuristic algorithms as well as other exact synthesis algorithms. First, it can easily be adapted to support exotic logic primitives or complex constraints. This can typically be done by simply adding additional constraints to the SAT formulation or by slight alterations to existing clauses. Second, a SAT formulation can be

used to prove whether or not a solution to a specification exists at all.

Exact synthesis also has theoretical applications. For instance, it allows us to derive upper and lower bounds on the combinational complexity of Boolean functions. Kulikov shows how exact synthesis can be linked to such bounds in [76]. Using exact synthesis, Knuth has shown that all 5-variable Boolean functions can be represented using 2-input gate-level networks with at most 12 gates [69, p. 105].

In recent years, significant strides have been made in SAT solving algorithms [19]. These developments, coupled with increases in compute power, have led to a resurgence of algorithms backed by SAT solvers [53, 131, 132]. Despite this progress, the adoption of SAT-based exact synthesis has been limited, due to its unpredictable, and potentially long, runtime. There have been attempts to mitigate runtime with techniques such as the development of alternative CNF encodings, the addition of symmetry breaking clauses, and the use of counterexampleguided abstraction refinement (CEGAR) [69, 32]. However, these techniques are often applied in an ad-hoc matter. Moreover, it is not clear how the various encodings and constraints interact with different SAT solvers. To date no comprehensive quantitative comparison of the various methods exists. This presents difficulties in the design of new systems, as there is no data to use as a basis for any design choices. Another hurdle is that, like many EDA algorithms, SAT is difficult to parallelize. Some efforts have been made in parallelizing SAT solvers using techniques such as *cube-and-conquer*, clause sharing, and *portfolio* SAT solvers which apply different SAT solvers in a parallel or distributed manner [57, 62]. This has proven difficult, partially due to theoretical limitations of the resolution procedure [68]. Moreover, solvers based on these methods are typically domain agnostic, and do not take advantage of specific domain structure. Part of the motivation of this thesis is to catalogue and analyze these issues, while also proposing ways to mitigate them.

Thus, we see that there is a broad range of applications for exact synthesis. This, combined with the recent progress made by state-of-the-art SAT solvers, as well as the advantages offered by SAT-based synthesis, forms the motivation for the work in this thesis. In Section 1.4, we provide an overview of the contributions made in this work.

#### 1.4 Thesis Contributions

The contributions made in this thesis can be divided into two main categories:

- 1. Contributions to the core algorithms for multi-level exact logic synthesis. This includes different encodings and solving strategies.

- 2. Practical and theoretical applications of exact synthesis. This includes contributions to global logic restructuring algorithms as well as the use of exact synthesis in function

classification.

Here, we summarize these contributions, starting with the core algorithms.

### 1.4.1 Encodings & Quantitative Comparisons

Although SAT-based exact synthesis is a versatile technique, its runtime behavior may be unpredictable and slow, due to NP-complete nature of SAT. There have been attempts to mitigate runtime through methods such as alternative CNF encodings, symmetry breaking clauses, and the use of *counterexample-guided abstraction refinement* (CEGAR) [69, 32]. However, these techniques are often applied in an ad-hoc matter. Moreover, it is not clear how the various encodings and constraints interact with different SAT solvers. To date no comprehensive quantitative comparison of the various methods exists. Finally, there does not exist a comprehensive review of the various encodings.

The first contribution of this thesis is to present detailed descriptions of the various encodings. Thus, one may use this thesis as a reference for SAT-based exact synthesis algorithms. Moreover, we present a series of experiments which demonstrate, for the first time, quantitative differences between CNF encodings. The descriptions and quantitative results can be used as a basis for the design and implementation of SAT-based exact synthesis systems. The experiments are implemented with the open source *percy* tool, which is available to the public at https://github.com/whaaswijk/percy.

#### 1.4.2 DAG Topology Families

We propose a new type of constraint based on families of DAG topologies. Such families restrict the search space considerably and let us partition the synthesis problem in a natural way. Our approach shows significant reductions in runtime as compared to state-of-the-art implementations, by up to 63%. Moreover, our implementation has significantly fewer timeouts compared to baseline and reference implementations, and reduces this number by up to 61%. In fact, our topology based implementation dominates the others with respect to the number of solved instances: given a runtime bound, it solves at least as many instances as any other implementation. Thus, we show how domain specific knowledge can be used to aid the SAT engine.

#### 1.4.3 Parallel Synthesis

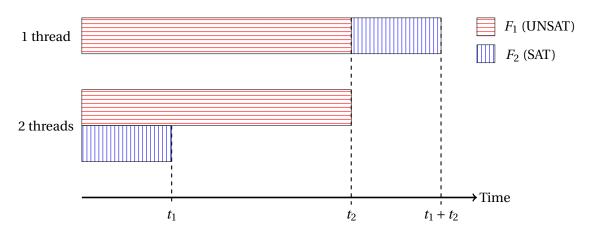

A common drawback of SAT is that the algorithms used by state-of-the-art solvers are hard to parallelize. Of course, this drawback is not limited to SAT. Indeed, it is a common drawback of

logic synthesis algorithms. In this thesis, we show how DAG topologies can be used to inject parallelism into the synthesis problem. We show how topology information can be used to transform the SAT-based exact synthesis problem into an embarrassingly parallel one. This allows us to design parallel algorithms that are up to 68x faster than the state-of-the-art.

#### 1.4.4 Applications

**Practical.** Some logic rewriting algorithms use exact synthesis to replace small subnetworks by their optimum representations. However, conventional approaches have two major drawbacks. First, their scalability is limited, as Boolean functions are enumerated to precompute their optimum representations. Second, the strategies used to replace subnetworks are not satisfactory. We show how the use of exact synthesis for logic rewriting can be improved. To this end, we propose a novel method that includes various improvements over conventional approaches: (i) we improve the subnetwork selection strategy, (ii) we show how enumeration can be avoided, allowing our method to scale to larger subnetworks, and (iii) we introduce XOR Majority Graphs (XMGs) as compact logic representations that make exact synthesis more efficient. We show a 46% geometric mean reduction (taken over size, depth, and switching activity), a 7% size reduction, and  $depth \cdot size$  reductions of 9%, compared to the academic state-of-the-art. Finally, we outperform 3 over 9 of the best known size results for the EPFL benchmark suite, reducing size by up to 12% and depth up to 47%.

*Theoretical.* One theoretical application of exact synthesis is Boolean function classification. Indeed, it was the method used by Knuth to classify functions in terms of their combinational complexity and minimum depth [69], although he uses enumeration-based exact synthesis as opposed to SAT. We show how a parallel implementation of our SAT-based exact parallelized, which we use to obtain a speedup of approximately 48x. By combining our method with NPN canonization, we find for the first time the minimum-sized logic networks for all 4- and 5-input functions in terms of 3-input Boolean operators.

#### 1.5 Thesis Outline

The remainder of this thesis is organized into five chapters and an appendix. The chapter contents correspond to the main areas in which our contributions fall, as described above.

**Chapter 2 -** In this chapter we start by describing, in detail, the workings of SAT-based exact synthesis. We provide some background and give pointers to existing literature. We then describe different SAT encodings for exact synthesis, and provide quantitative comparisons between them. Finally, we analyze the computational complexity of SAT-based exact synthesis, and how it relates to the minimum circuit size problem (MCSP).

**Chapter 3** - Here, we make the observation that information about the DAG structure of a network can be used to speed up the search for an optimum logic representation. In this chapter, we further describe how such DAG topology information can be used by SAT-based exact synthesis algorithms, and that significant runtime improvements can be obtained by doing so. Additionally, we show how topology information can be used to partition the SAT search space. This leads us to proposing an embarrassingly parallel exact synthesis method, based on families of DAG topologies. We show how our domain-specific parallel method outperforms both single-threaded performance, as well as a state-of-the-art parallel SAT solver.

**Chapter 4** - Here begins the second part of this work, in which we look at applications of SAT-based exact synthesis. In this particular chapter, we examine the task of classifying Boolean functions in terms of their intrinsic difficulty. This is of theoretical interest, as helps us understand the distribution of Boolean functions and optimum Boolean chains. It can also help us to find better bounds on circuit sizes. Finally, the techniques we have used to establish these results, such as efficient NPN canonization, can be applied in more practical settings as well, as we show in Chapter 5.

**Chapter 5** - One of the most important practical applications of exact synthesis is as a core engine in logic rewriting. In this chapter, we introduce a novel data structure known as XOR-Majority Graphs (XMGs). This compact logic representation is well suited for fast exact synthesis, and for representing XOR/MAJ-heavy logic, such as that occurring in arithmetic units. Combining this new representation, and our exact synthesis algorithms, we introduce a new type of logic rewriting algorithm which does not rely on any sort of precomputation. We show how it can be used to find improvements over state-of-the-art rewriting algorithms.

**Chapter 6** - This chapter is an extension and generalization of the work in Chapter 5. We present a generic logic rewriting algorithm for arbitrary k-feasible Boolean networks. As it executes, our algorithm constructs a conflict graph. This graph indicates which subnetworks cannot be rewritten simultaneously. We use it to take both a local and a global view of the optimizations that are achievable by rewriting the network. We try to maximize the possible gain by solving, approximately, the maximum weighted vertex independent set problem on the conflict graph. Finally, we show how our new algorithm finds improvements over state-of-the-art algorithms.

**Chapter 7** - In this final chapter, we conclude by summarizing our findings and discussing the contributions of this work. We also describe some open problems, and finish by painting a future outlook.

**Appendix A -** This appendix describes the motivation behind, and design of, a state-of-the-art exact synthesis library called *percy*. One of the main design goals of *percy* is to allow one to

quickly prototype and experiment with various SAT-based exact synthesis methods. To that end, it implements all synthesis methods described in this thesis. The appendix describes the library design and components in more detail. It also contains several concrete code examples. Although simple, these scripts demonstrate how the *percy* API can be used in practice, and how it interacts with some of the other EPFL logic synthesis libraries.

# Core Algorithms Part I

# 2 Synthesis & Encoding