# Logic Synthesis Foundations for Efficient Secure Computation: From Fully Homomorphic Encryption to Garbled Circuits

présenté le 31 Octobre 2025 à la Faculté des Sciences et Techniques de l'Ingénieur (STI) Laboratoire des Systèmes Intégrés (LSI) Programme Doctoral en Génie Électrique École Polytechnique Fédérale de Lausanne

pour l'obtention du grade de Docteur ès Sciences par

acceptée sur proposition du jury:

Prof. Mario Paolone, président du jury

Prof. Giovanni De Micheli, directeur de thèse Prof. David Atienza, codirecteur de thèse

Prof. Paolo lenne, rapporteur

Prof. Makoto Ikeda, rapporteur

Tion. Makoto ikeda, Tapporteur

Prof. Ingrid Verbauwhede, rapporteur

Lausanne, EPFL, 2025

| Never put off until runtime what you can do at compile time. — John Hennessy |  |

|------------------------------------------------------------------------------|--|

| To all the glorious entanglements that found their way to me.                |  |

| To all the giorious entanglements that found their way to me.                |  |

|                                                                              |  |

|                                                                              |  |

|                                                                              |  |

## Acknowledgements

First and foremost, I would like to express my deepest gratitude to my PhD advisor, Professor Giovanni De Micheli, and my co-advisor, Professor David Atienza. Nanni, in every sense, is a remarkably wise and generous mentor. Over the past four years, there have been countless moments when I was enlightened by his insight, both within research and far beyond. Despite my early-stage immaturity as a researcher, Nanni entrusted me with the freedom to pursue the problems that fascinated me the most. This freedom, paired with his constant and unconditional support, created an ideal environment for my intellectual growth. I have felt this support ever since receiving his very first reply during my master's studies, and it has never ceased. I could never thank him enough for that. To David, I owe my sincere appreciation as well. Although our interactions were less frequent, they were always impactful. I was consistently inspired by his boundless energy and enthusiasm, even during an incredibly demanding schedule. His support, too, has been timely and wholehearted. I am confident that, when I have the opportunity to mentor the next generation of researchers, my philosophy will carry the influence of both Nanni and David.

I extend my gratitude to the members of my dissertation jury: Professor Mario Paolone, who served as president, and Professors Paolo Ienne, Makoto Ikeda, and Ingrid Verbauwhede, who generously acted as reviewers. I sincerely appreciate their time and effort in reviewing my dissertation and participating in the intense but unforgettable oral defense. I still vividly remember how each expert's questions reflected their unique research perspectives and personalities, making the discussion both challenging and intellectually rewarding. I remain amazed by the new ideas that emerged during that exchange and am deeply thankful for the opportunity to engage with them.

I would also like to thank my master's advisor, Professor Masahiro Fujita. Through his example, Fujita-sensei has continually reminded me to stay honest with myself in conducting research, remaining open-minded while having the courage to pursue questions that truly intrigue me. I am immensely grateful to the LSIers — my colleagues at the Integrated Systems Laboratory. To those who overlapped with my four years at LSI: Dr. Mathias Soeken, Dr. Rassul Bairamkulov, Professor Chang Meng, Dr. Rehab Massoud, Dr. Bruno Schmidt, Dr. Fereshte Mozafari, Dr. Siang-Yun (Sonia) Lee, Dr. Alessandro Tempia Calvino, Dr. Dewmini Sudara Marakkalage, Andrea Costamagna, Junrui Chen, Hanyu Wang, and Julien de Castelnau, it was a great privilege to share this time with you in such an extraordinary research group.

Our interactions extended far beyond research: through them, I gradually learned that excellence, humility, and kindness can coexist. Immersed in this supportive and encouraging environment, I slowly gained the strength to acknowledge my limitations, embrace failure, and find the courage to begin again. My heartfelt thanks also go to our wonderful secretary, Ms. Chantal Demont. Chantal's tireless efforts, whether handling countless administrative tasks or organizing team-building events, ensured that our lab remained lively and focused. Her behind-the-scenes work made our research lives significantly smoother, and I am deeply appreciative of her dedication. Lastly, I would like to acknowledge the former LSI members whom I had the pleasure of meeting in various corners of the world: Professor Pierre-Emmanuel Gaillardon, Dr. Luca Amarù, Professor Zhufei Chu, Professor Cunxi Yu, Dr. Xifan Tang, Dr. Heinz Riener, Dr. Winston Haaswijik, Dr. Eleonora Testa, and Dr. Giulia Meuli. Thank you for your kindness, encouragement, and insightful guidance — you have helped me more than you know.

I deeply believe that meaningful breakthroughs — especially in interdisciplinary research areas such as design automation for cryptography — are rarely achieved in isolation. I would therefore like to express my sincere gratitude to my collaborators. My first project on graphlevel optimization for leveled homomorphic encryption acceleration began to take shape thanks to fruitful discussions with Dr. Christian Mouchet, whose insights helped lay its foundation. Later, in collaboration with Dr. Sergiu Carpov and Dr. Gabrielle De Micheli, I found not only exceptional technical partners, but also generous and reliable colleagues who patiently corrected and enriched my understanding of modern FHE constructions. I would also like to thank the Computer Security Group at CWI, Amsterdam, led by Professor Marten van Dijk and Dr. Chenglu Jin. During my research internship, I was warmly welcomed into their group — a gesture I remain deeply grateful for.

I dedicate the next paragraph to all my mentors and friends. I have chosen not to name anyone specifically here, because I know I could never list all those who have profoundly shaped me. Your influence on my life and thinking has often come in subtle, hybrid ways. Many professors, researchers, and PhD students I encountered at academic conferences inspired me not only through their work but also through the life philosophies they embodied. At the same time, many of my closest friends work in entirely different areas, some not even in academia, but I find that my passion for certain research topics or philosophical ideas often echoes the spirit of our conversations. Everything is connected, and I feel truly fortunate to have been surrounded by people and moments that shaped who I am.

To my family: thank you for being the unwavering support that has anchored me through the highs and lows. You have absorbed my stress, anxiety, and doubts with patience and love. I am especially grateful to my grandparents and parents for always having my back — mentally, emotionally, and even financially — gently offering their guidance while respecting my choices. I feel deeply blessed to have such a family. I also want to express my love and gratitude to my wife, Yiru. After being together for seven years, we got married this year, which is a milestone that, to me, surpasses the PhD in significance and meaning. This journey has not been easy: the inherent uncertainty of research, combined with the complexity of life's choices, often threw us into overwhelming situations. But in navigating them together, we became each

other's constants — our "fixed parameters" in the grand decision-making problem of how to live a meaningful life. For that, I am endlessly thankful.

This world is changing rapidly, often provoking uncertainty and unease. The rise of large language models, for instance, is reshaping how we interact with knowledge and conduct research. And the world's darkness remains ever-present: the war between Russia and Ukraine broke out just before I began my PhD and still continues today, with many more conflicts arising in other corners of the world. Yet the more I write this acknowledgment, the more clearly I see how blessed I have been throughout this journey. This is the message I hope to leave here: you have all helped me resist being overwhelmed by negativity and reminded me to keep looking forward. With these words, I finally come to terms with the fact that this PhD chapter is drawing to a close — how luxurious it has been! But your influence will not end here; it will remain with me as a lifelong gift, equipping me for whatever comes next.

EPFL, November 16, 2025

Mingfei Yu

### **Abstract**

As digital data become central to domains, ranging from personalized medicine and financial services to scientific research and national security, preserving its confidentiality during computation has emerged as a foundational challenge. Recent breaches illustrate the severe consequences of compromised information: privacy violations, identity theft, and loss of public trust. Traditional encryption protects data at rest and in transit, but leaves a critical gap during *computation*, when sensitive inputs are typically exposed. Secure computation techniques, notably *fully homomorphic encryption* (FHE) and *garbled circuits* (GC), close this gap by enabling meaningful computation over encrypted or distributed data without revealing the underlying inputs.

Despite remarkable progress, these techniques still suffer from high computational and communication overheads, limiting their practical deployment. This thesis targets a specific, but broadly applicable, scenario: the secure evaluation of Boolean functions using FHE and GC. While secure computing techniques are not inherently restricted to Boolean logic, focusing on Boolean circuits allows us to leverage decades of progress in *logic synthesis*, a mature subfield of *electronic design automation*. By casting secure computation as a domain-specific logic synthesis problem — one governed by cryptographic cost models rather than silicon constraints in the conventional context — we develop novel circuit optimization techniques that bridge classical logic design and modern cryptography.

We make contributions across five technical directions: (i) For leveled FHE schemes, we formalize the trade-off between *multiplicative depth* (MD) and *multiplicative complexity* (MC), and introduce synthesis frameworks that jointly reduce both, enabling tighter cryptographic parameters and faster homomorphic evaluation. (ii) For fast-bootstrapping FHE schemes, represented by the *torus FHE* (TFHE) scheme, under a fixed-plaintext-space function-evaluation strategy, we develop symmetry- and negacyclicity-aware mapping strategies, combined with a *multi-value programmable bootstrapping* (MV-PBS)—aware *lookup-table* (LUT) network synthesizer, to minimize PBS count. (iii) For TFHE-based, multi-plaintext-space function evaluation, we propose the first synthesis framework that strategically transitions between binary and large plaintext spaces, using XORs for linear logic and concentrating non-linear operations into compact LUTs. (iv) For GC, we introduce the *XOR—OneHot—inverter graph* (X1G), a new intermediate representation that improves ciphertext efficiency and unlocks dedicated optimization passes. (v) Finally, we introduce *joint multiplicative complexity* (JMC), a garbling-cost-aware cost model that accounts for shared ownership in GC-based secure multi-party

computation, and propose the first ownership-aware optimizer that reduces jointly evaluated non-linear gates.

Collectively, these results demonstrate two broad lessons: (1) *representation matters* — the choice of intermediate form directly impacts achievable savings and the scope of optimizations; and (2) *cost models must match cryptographic reality* — accurate modeling of performance bottlenecks is essential to obtain meaningful efficiency gains. Beyond these technical findings, the thesis argues for stronger standardization and cross-layer interfaces between cryptographic libraries, compilers, and hardware, to ensure that optimizations at one layer remain aligned with advances at others. By bridging logic synthesis with modern secure computation techniques, this work takes a step toward making cryptographic protocols not only theoretically powerful, but also practically usable at scale.

Key words: logic synthesis, cryptography-aware compiler design, secure computation, fully homomorphic encryption, garbled circuits

### Résumé

À mesure que les données numériques deviennent essentielles dans des domaines allant de la médecine personnalisée et des services financiers à la recherche scientifique et à la sécurité nationale, la préservation de leur confidentialité durant le calcul s'impose comme un défi fondamental. Les incidents récents illustrent les conséquences graves d'une compromission de l'information : atteintes à la vie privée, vols d'identité et perte de confiance du public. Le chiffrement traditionnel protège les données au repos et en transit, mais laisse une faille critique durant la *phase de calcul*, lorsque les données sensibles sont généralement exposées. Les techniques de calcul sécurisé, notamment le *chiffrement entièrement homomorphe* (FHE) et les *circuits brouillés* (GC), comblent cette lacune en permettant d'effectuer des calculs utiles sur des données chiffrées ou distribuées sans révéler les entrées sous-jacentes.

Malgré des progrès remarquables, ces techniques souffrent encore de surcoûts computationnels et communicationnels élevés, limitant leur déploiement pratique. Cette thèse cible un scénario spécifique, mais largement applicable, l'évaluation sécurisée de fonctions booléennes à l'aide de FHE et de GC. Bien que les techniques de calcul sécurisé ne soient pas intrinsèquement limitées à la logique booléenne, se concentrer sur des circuits booléens permet de tirer parti de décennies de progrès en *synthèse logique*, un sous-domaine mature de la *conception assistée par ordinateur*. En reformulant le calcul sécurisé comme un problème de synthèse logique spécifique au domaine — régi par des modèles de coûts cryptographiques plutôt que par des contraintes liées au silicium dans le contexte conventionnel — nous développons de nouvelles techniques d'optimisation de circuits reliant la conception logique classique et la cryptographie moderne.

Nous apportons des contributions selon cinq directions techniques : (i) pour les schémas FHE à niveaux, nous formalisons le compromis entre *profondeur multiplicative* (MD) et *complexité multiplicative* (MC), et introduisons des cadres de synthèse réduisant conjointement les deux, permettant des paramètres cryptographiques plus serrés et une évaluation homomorphe plus rapide; (ii) pour les schémas FHE à démarrage rapide, représentés par le schéma *Torus FHE* (TFHE), dans une stratégie d'évaluation à espace de clair fixé, nous développons des stratégies de mappage sensibles aux symétries et à la négacyclicité, combinées à un synthétiseur de réseaux de *tables de correspondance* (LUT) compatible avec le *programmable bootstrapping multi-valeurs* (MV-PBS), afin de minimiser le nombre de PBS; (iii) pour l'évaluation de

fonctions basée sur TFHE avec plusieurs espaces de clair, nous proposons le premier cadre de synthèse permettant des transitions stratégiques entre l'espace binaire et les espaces de clair de grande dimension, en utilisant les XOR pour la logique linéaire et en concentrant les opérations non linéaires dans des LUT compactes; (iv) pour les GC, nous introduisons le *graphe XOR-OneHot-inverter* (X1G), une nouvelle représentation intermédiaire améliorant l'efficacité des chiffrés et permettant des passes d'optimisation dédiées; (v) enfin, nous introduisons la notion de *complexité multiplicative conjointe* (JMC), un modèle de coût conscient du coût de brouillage tenant compte du partage de propriété dans le calcul multipartite basé sur les GC, et proposons le premier optimiseur sensible à cette notion, réduisant les portes non linéaires évaluées conjointement.

Pris collectivement, ces résultats démontrent deux enseignements généraux : (1) la représentation importe — le choix de la forme intermédiaire influence directement les gains réalisables et l'étendue des optimisations; et (2) les modèles de coûts doivent correspondre à la réalité cryptographique — une modélisation précise des goulets d'étranglement est essentielle pour obtenir des gains d'efficacité significatifs. Au-delà de ces conclusions techniques, la thèse plaide pour une standardisation renforcée et pour des interfaces inter-couches plus robustes entre bibliothèques cryptographiques, compilateurs et matériel, afin de garantir que les optimisations à un niveau restent alignées avec les avancées aux autres niveaux. En reliant la synthèse logique aux techniques modernes de calcul sécurisé, ce travail contribue à rendre les protocoles cryptographiques non seulement puissants sur le plan théorique, mais également véritablement utilisables à grande échelle.

Mots clefs : synthèse logique, conception de compilateurs pour la cryptographie, calcul sécurisé, chiffrement entièrement homomorphe, circuits brouillés.

# **Contents**

| Ac | cknov | wledge  | ments                                                                       | j   |

|----|-------|---------|-----------------------------------------------------------------------------|-----|

| Ał | ostra | ct (Eng | dish/Français)                                                              | v   |

| Li | st of | Figure  | s                                                                           | XV  |

| Li | st of | Tables  |                                                                             | xvi |

| Li | st of | Acrony  | /ms                                                                         | xix |

| 1  | Intr  | oducti  | ion                                                                         | 1   |

|    | 1.1   | Secur   | e Computation Techniques                                                    | 1   |

|    |       | 1.1.1   | Secure Outsourced Computation vs. Secure Multi-Party Computation .          | 2   |

|    |       | 1.1.2   | Performance Limitations of Modern Secure Computation Techniques .           | 3   |

|    |       | 1.1.3   | Fully Homomorphic Encryption                                                | 4   |

|    |       | 1.1.4   | Garbled Circuits                                                            | 6   |

|    | 1.2   | Resea   | rch Efforts for Accelerating Secure Computation: The Case of Fully Homo-    |     |

|    |       | morp    | hic Encryption                                                              | 7   |

|    |       | 1.2.1   | Application-Level Optimization                                              | 8   |

|    |       | 1.2.2   | Cryptographic Construction-Level Optimization                               | g   |

|    |       | 1.2.3   | Compiler-Level Optimization                                                 | 10  |

|    |       | 1.2.4   | Hardware-Level Optimization                                                 | 12  |

|    | 1.3   | Resea   | arch Scope                                                                  | 14  |

|    |       | 1.3.1   | Role of Logic Circuit Optimization                                          |     |

|    |       | 1.3.2   | Contributions of This Thesis                                                | 16  |

|    | 1.4   | Thesi   | s Organization                                                              | 16  |

|    |       | 1.4.1   | Part I: Efficient Fully Homomorphic Encryption from the Ground Up $$ . $$ . | 17  |

|    |       | 1.4.2   | Part II: Toward Practical Garbled Circuits                                  | 19  |

| 2  | Pre   | limina  | ries                                                                        | 23  |

|    | 2.1   | Logic   | Synthesis Preliminaries                                                     | 23  |

|    |       | 2.1.1   | Logic Representation                                                        | 24  |

|    |       | 2.1.2   | Logic Optimization                                                          | 27  |

|    | 2.2   | Crypt   | ographic Preliminaries                                                      | 30  |

|    |       | 2.2.1   | Fully Homomorphic Encryption                                                | 30  |

|   |      | 2.2.2   | Modern FHE Schemes                              | 31 |

|---|------|---------|-------------------------------------------------|----|

|   |      | 2.2.3   | Garbled Circuits                                | 33 |

|   |      | 2.2.4   | Advanced Garbling Techniques                    | 35 |

|   | 2.3  | Bench   | nmark Suites                                    | 36 |

|   |      | 2.3.1   | EPFL Combinational Benchmark Suite              | 37 |

|   |      | 2.3.2   | Cryptographic Benchmark Suite                   | 38 |

|   |      | 2.3.3   | MPCircuit Benchmark Suite                       | 39 |

|   |      | 2.3.4   | LOBSTER Benchmark Suite                         | 40 |

| Ι | Effi | cient l | Fully Homomorphic Encryption from the Ground Up | 43 |

| 3 | Mul  | _       | tive Depth vs. Complexity in Leveled FHE        | 45 |

|   | 3.1  |         | ration                                          | 45 |

|   | 3.2  |         | ninaries                                        | 47 |

|   |      | 3.2.1   | FHE Schemes: Leveled vs. Fast Bootstrapping     | 47 |

|   |      | 3.2.2   | Multiplicative Depth in Logic Networks          | 48 |

|   |      | 3.2.3   | Circuit Optimization in Leveled FHE Schemes     | 48 |

|   |      | 3.2.4   | MD Reduction                                    | 49 |

|   | 3.3  | FHE-0   | Cost-Optimum Synthesis for Boolean Functions    | 50 |

|   |      | 3.3.1   | Overview of the Methodology                     | 51 |

|   |      | 3.3.2   | SAT Encoding                                    | 53 |

|   |      | 3.3.3   | Identification of AND Fence Candidates          | 54 |

|   |      | 3.3.4   | Exact Synthesis Paradigm for Boolean Functions  | 56 |

|   | 3.4  | Exact   | Synthesis for Sub-circuits                      | 57 |

|   |      | 3.4.1   | Effects of Non-zero Input MD                    | 57 |

|   |      | 3.4.2   | Integrating Scheduling into SAT Encoding        | 59 |

|   |      | 3.4.3   | Strategic Selection of Scheduling Solutions     | 59 |

|   |      | 3.4.4   | Exact Synthesis Paradigm for Sub-circuits       | 60 |

|   |      | 3.4.5   | Classifying Exact-Synthesis Queries             | 61 |

|   | 3.5  | MC-a    | ware MD Optimization                            | 64 |

|   |      | 3.5.1   | Algorithm Overview                              | 65 |

|   |      | 3.5.2   | Leveled FHE Circuit Optimization Flow           | 66 |

|   | 3.6  | Exper   | imental Evaluation                              | 67 |

|   |      | 3.6.1   | Experimental Setup                              | 68 |

|   |      | 3.6.2   | Evaluating MC-aware MD Minimization             | 68 |

|   |      | 3.6.3   | Evaluating the Full Optimization Flow           | 69 |

|   | 3.7  | Discu   | ssion                                           | 70 |

|   |      | 3.7.1   | The Importance of Joint MC–MD Optimization      | 71 |

|   |      | 3.7.2   | Extension to Arithmetic FHE Circuits            | 71 |

|   |      | 3.7.3   | Limitations and Directions for Future Work      | 72 |

#### **Contents**

| 4 | Tecl           | hnolog | y Mapping for TFHE                                            | 73              |

|---|----------------|--------|---------------------------------------------------------------|-----------------|

|   | 4.1            | Motiv  | ation                                                         | 73              |

|   | 4.2            | Prelin | ninaries                                                      | 75              |

|   |                | 4.2.1  | Fully Homomorphic Encryption                                  | 75              |

|   |                | 4.2.2  | Torus FHE                                                     | 76              |

|   |                | 4.2.3  | Homomorphic Logic Gate Evaluation via PBS                     | 77              |

|   |                | 4.2.4  | Related Works                                                 | 79              |

|   | 4.3            | TFHE   | Circuit Synthesis via Technology Mapping                      | 81              |

|   |                | 4.3.1  | Homomorphic Gate Set                                          | 81              |

|   |                | 4.3.2  | Area-Oriented Technology Mapping                              | 84              |

|   | 4.4            | MV-P   | BS-aware Mapping                                              | 86              |

|   |                | 4.4.1  | Technology Mapping with Label Monitoring                      | 86              |

|   |                | 4.4.2  | Inverter Reduction                                            | 88              |

|   | 4.5            | Exper  | imental Evaluations                                           | 91              |

|   |                | 4.5.1  | Profiling Synthesized Circuits                                | 91              |

|   |                | 4.5.2  | Estimating Evaluation Cost Reduction                          | 93              |

|   | 4.6            | Discu  | ssion                                                         | 94              |

|   |                | 4.6.1  | Strategic Use of Incomplete Gate Sets                         | 95              |

|   |                | 4.6.2  | Exploring a Unique Logic Synthesis Problem                    | 96              |

| _ | E              |        | CAUSA COM MONOCOMO ANA ÉS O TENTE                             | 00              |

| 5 | <b>Enc</b> 5.1 | _      | Strategy Management for TFHE                                  | <b>99</b><br>99 |

|   |                |        | ation                                                         |                 |

|   | 5.2            |        | TELLE Gravit Symthesis. Fundamentals and Drien Work           |                 |

|   |                | 5.2.1  |                                                               |                 |

|   | <b>5</b> 2     | 5.2.2  | O I                                                           |                 |

|   | 5.3            |        | . 6 6                                                         |                 |

|   |                | 5.3.1  | Encoding Strategy Behavior in XAG-Based Evaluation            |                 |

|   | <b>5</b> 4     | 5.3.2  | Encoding Strategy Behavior in ESOP-Based Evaluation           |                 |

|   | 5.4            |        | -Guided TFHE Circuit Synthesis via Cost-Aware Cut Replacement |                 |

|   |                | 5.4.1  | High-Level Flow                                               |                 |

|   |                | 5.4.2  | Cut-Aware ESOP Cost Modeling                                  |                 |

|   |                | 5.4.3  | Cost-Aware Cut Selection                                      |                 |

|   |                | 5.4.4  | Practical Considerations and Implementation Notes             |                 |

|   | 5.5            | -      | imental Results                                               |                 |

|   |                | 5.5.1  | Overview and Methodology                                      |                 |

|   |                | 5.5.2  | Performance Breakdown                                         |                 |

|   | _              | 5.5.3  | Analysis of PBS Types                                         |                 |

|   | 5.6            |        | ssion                                                         | 117             |

|   |                | 5.6.1  | What this chapter contributes                                 |                 |

|   |                | 5.6.2  | Limitations                                                   |                 |

|   |                | 5.6.3  | Future directions                                             | 118             |

|   | 6.1<br>6.2<br>6.3<br>6.4<br>6.5 | Motivation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 125<br>126<br>126<br>127<br>129<br>130<br>131<br>132<br>133<br>134<br>135<br>136 |

|---|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

|   | 6.2<br>6.3<br>6.4<br>6.5        | Preliminaries 6.2.1 Garbling Gadget                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 125<br>126<br>126<br>127<br>129<br>130<br>131<br>132<br>133<br>134<br>135<br>136 |

|   | 6.3<br>6.4<br>6.5               | 6.2.1 Garbling Gadget                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 125<br>126<br>127<br>129<br>130<br>131<br>132<br>133<br>134<br>135<br>136        |

|   | 6.4<br>6.5                      | A Ciphertext-Efficient Logic Representation  6.3.1 MC Compactness  6.3.2 Properties of ONEHOT and Immediate Consequences  Mapping XAGs to X1Gs via Algebraic Rewriting  6.4.1 An Algebraic–Rewriting–Based Mapping  6.4.2 Limitations and a Motivating Example  Agilely Synthesizing Optimal X1G Implementations for Small-Scale Functions  6.5.1 AND Fence  6.5.2 Abstract XAG  6.5.3 Exact Synthesis of Ciphertext–Optimal X1Gs  6.5.4 Database Generation (Up-To-Six-Variable Functions)  A Logic Optimization Flow for X1Gs  6.6.1 Database-Driven Logic Rewriting  6.6.2 Don't-Care–Based OneHot Reduction | 126<br>127<br>129<br>129<br>130<br>131<br>132<br>133<br>134<br>135<br>136        |

|   | 6.4<br>6.5                      | 6.3.1 MC Compactness                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 126<br>127<br>129<br>130<br>131<br>132<br>133<br>134<br>135<br>136               |

| ( | 6.5<br>6.6                      | 6.3.2 Properties of ONEHOT and Immediate Consequences  Mapping XAGs to X1Gs via Algebraic Rewriting 6.4.1 An Algebraic–Rewriting–Based Mapping 6.4.2 Limitations and a Motivating Example  Agilely Synthesizing Optimal X1G Implementations for Small-Scale Functions 6.5.1 AND Fence 6.5.2 Abstract XAG 6.5.3 Exact Synthesis of Ciphertext–Optimal X1Gs 6.5.4 Database Generation (Up-To-Six-Variable Functions)  A Logic Optimization Flow for X1Gs 6.6.1 Database-Driven Logic Rewriting 6.6.2 Don't-Care–Based OneHot Reduction                                                                            | 127<br>129<br>130<br>131<br>132<br>133<br>134<br>135<br>136                      |

| ( | 6.5<br>6.6                      | Mapping XAGs to X1Gs via Algebraic Rewriting  6.4.1 An Algebraic–Rewriting–Based Mapping  6.4.2 Limitations and a Motivating Example  Agilely Synthesizing Optimal X1G Implementations for Small-Scale Functions  6.5.1 AND Fence  6.5.2 Abstract XAG  6.5.3 Exact Synthesis of Ciphertext–Optimal X1Gs  6.5.4 Database Generation (Up-To-Six-Variable Functions)  A Logic Optimization Flow for X1Gs  6.6.1 Database-Driven Logic Rewriting  6.6.2 Don't-Care–Based OneHot Reduction                                                                                                                           | 129<br>129<br>130<br>131<br>132<br>133<br>134<br>135<br>136                      |

|   | 6.5<br>6.6                      | 6.4.1 An Algebraic–Rewriting–Based Mapping 6.4.2 Limitations and a Motivating Example Agilely Synthesizing Optimal X1G Implementations for Small-Scale Functions 6.5.1 AND Fence 6.5.2 Abstract XAG 6.5.3 Exact Synthesis of Ciphertext–Optimal X1Gs 6.5.4 Database Generation (Up-To-Six-Variable Functions) A Logic Optimization Flow for X1Gs 6.6.1 Database-Driven Logic Rewriting 6.6.2 Don't-Care–Based OneHot Reduction                                                                                                                                                                                  | 129<br>130<br>131<br>132<br>132<br>133<br>134<br>135<br>136                      |

| , | 6.6                             | 6.4.2 Limitations and a Motivating Example  Agilely Synthesizing Optimal X1G Implementations for Small-Scale Functions .  6.5.1 AND Fence                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 130<br>131<br>132<br>132<br>133<br>134<br>135<br>136<br>137                      |

| , | 6.6                             | Agilely Synthesizing Optimal X1G Implementations for Small-Scale Functions .  6.5.1 AND Fence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 131<br>132<br>132<br>133<br>134<br>135<br>136<br>137                             |

| , | 6.6                             | <ul> <li>6.5.1 AND Fence</li> <li>6.5.2 Abstract XAG</li> <li>6.5.3 Exact Synthesis of Ciphertext–Optimal X1Gs</li> <li>6.5.4 Database Generation (Up-To-Six-Variable Functions)</li> <li>A Logic Optimization Flow for X1Gs</li> <li>6.6.1 Database-Driven Logic Rewriting</li> <li>6.6.2 Don't-Care–Based OneHot Reduction</li> </ul>                                                                                                                                                                                                                                                                         | 132<br>132<br>133<br>134<br>135<br>136                                           |

| ( |                                 | 6.5.2 Abstract XAG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 132<br>133<br>134<br>135<br>136<br>137                                           |

| ( |                                 | 6.5.3 Exact Synthesis of Ciphertext–Optimal X1Gs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 133<br>134<br>135<br>136<br>137                                                  |

| ( |                                 | 6.5.4 Database Generation (Up-To-Six-Variable Functions)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 134<br>135<br>136<br>137                                                         |

| ( |                                 | A Logic Optimization Flow for X1Gs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 135<br>136<br>137                                                                |

| ( |                                 | 6.6.1 Database-Driven Logic Rewriting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 136<br>137                                                                       |

|   |                                 | 6.6.2 Don't-Care–Based OneHot Reduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 137                                                                              |

|   |                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                  |

|   |                                 | 6.6.3 Constant-Driven Algebraic Post-Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 137                                                                              |

|   |                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                  |

|   | 6.7                             | Experimental Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 138                                                                              |

| • |                                 | 6.7.1 Evaluation of the Exact-Synthesis Formulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 138                                                                              |

|   |                                 | 6.7.2 Evaluation of the X1G Optimization Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 139                                                                              |

|   | 6.8                             | Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 141                                                                              |

|   |                                 | 6.8.1 Summary of Contributions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 141                                                                              |

|   |                                 | 6.8.2 Optimization Effort vs. Runtime                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                  |

|   |                                 | 6.8.3 Where X1G Helps and Where It Does Not                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 142                                                                              |

|   |                                 | 6.8.4 Future Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 142                                                                              |

|   |                                 | 6.8.5 A Question Pointing Forward                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 142                                                                              |

| 7 | Red                             | efining Cost in Garbled Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 145                                                                              |

| • | 7.1                             | Motivation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 145                                                                              |

| , | 7.2                             | Preliminaries                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 146                                                                              |

|   |                                 | 7.2.1 Boolean Decomposition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 147                                                                              |

|   |                                 | 7.2.2 Related work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 148                                                                              |

| , | 7.3                             | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 149                                                                              |

|   |                                 | 7.3.1 Node ownership and refined cost model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 149                                                                              |

|   |                                 | 7.3.2 Logic optimization framework                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 152                                                                              |

|   | 7.4                             | Methodology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 153                                                                              |

|   |                                 | 7.4.1 Joint-Compute–Oriented Decomposition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 153                                                                              |

|   |                                 | 7.4.2 Low-MC MUX Construction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 157                                                                              |

| , | 7.5                             | Experimental Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                  |

#### **Contents**

|   |     |                                   | Application-Dependent Benefits                     |                          |

|---|-----|-----------------------------------|----------------------------------------------------|--------------------------|

|   |     | 7.6.2                             | Role of Ownership-Aware Analysis                   |                          |

|   |     |                                   | A New Dimension of Secure Computation Optimization |                          |

|   |     | 7.6.4                             | Parallels with Information Flow Tracking           | 162                      |

| 8 | Con | clusio                            | ns and Outlook                                     | 165                      |

|   | 8.1 | Sumn                              | nary of Technical Contributions                    | 165                      |

|   | 82  | т                                 | na Tanana di Anna a Dunia da                       |                          |

|   | 0.2 | Lesso                             | ns Learned Across Projects                         | 167                      |

|   | 0.2 | 8.2.1                             | Representation Matters                             |                          |

|   | 0.2 | 8.2.1                             |                                                    | 167                      |

|   | 8.3 | 8.2.1<br>8.2.2                    | Representation Matters                             | 167<br>168               |

|   |     | 8.2.1<br>8.2.2                    | Representation Matters                             | 167<br>168<br>168        |

|   |     | 8.2.1<br>8.2.2<br>Cross-<br>8.3.1 | Representation Matters                             | 167<br>168<br>168<br>169 |

# **List of Figures**

| 1.1 | multi-party computation                                                               | 2   |

|-----|---------------------------------------------------------------------------------------|-----|

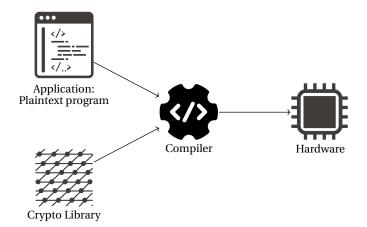

| 1.2 | Ongoing full-stack efforts to make FHE-based secure computation practical             | 7   |

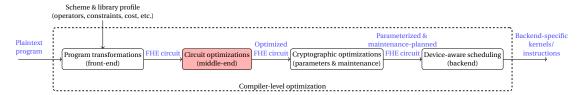

| 1.3 | An end-to-end FHE compilation pipeline.                                               | 15  |

|     |                                                                                       |     |

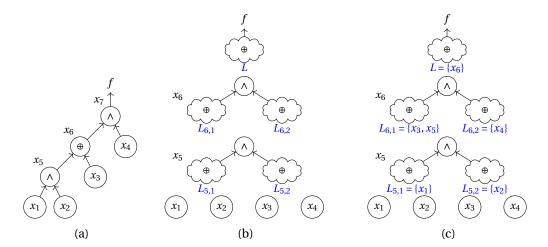

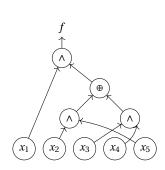

| 2.1 | An XAG implementation of a one-bit full adder                                         | 25  |

| 2.2 | From a plain AND gate to its four-row garbled truth table                             | 34  |

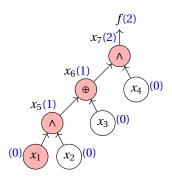

| 3.1 | An XAG for the four-variable function with truth table #7800                          | 48  |

| 3.2 | Deriving an abstract XAG from an XAG in two steps                                     | 52  |

| 3.3 | Two XAGs implementing the same cut under the given input MD                           | 58  |

| 4.1 | Naïve LUT encoding for a two-input AND gate in $\mathbb{Z}_8$ with $N = 16$           | 78  |

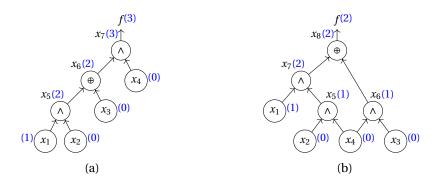

| 4.2 | Compression for three-input symmetric gates                                           | 82  |

| 4.3 | Compression for three-input negacyclic gates under the naïve encoding with the        |     |

|     | disjoint input assigned as MSB                                                        | 83  |

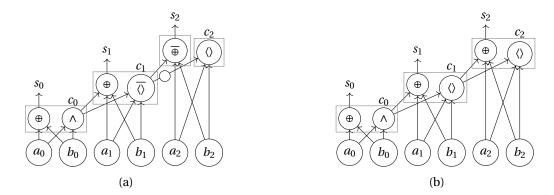

| 4.4 | Least significant three bits of a mapped 128-bit adder                                | 90  |

| 4.5 | Homomorphic Boolean circuit synthesis flows evaluated in this work                    | 91  |

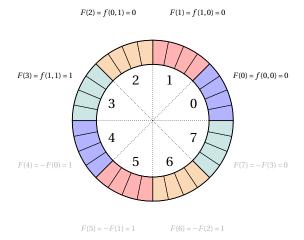

| 5.1 | Encoding a two-input AND LUT on the polynomial ring                                   | 102 |

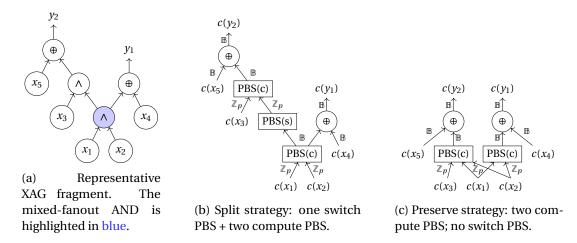

| 5.2 | Handling encoding transitions for an AND gate with mixed fanout                       | 106 |

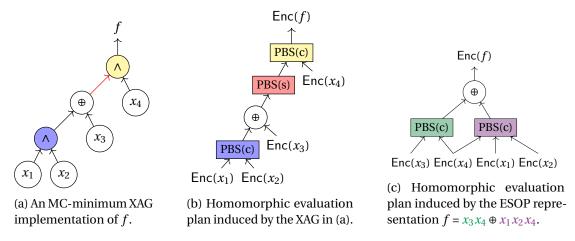

| 5.3 | Efficient homomorphic evaluation unlocked by the ESOP representation. $ \dots $       | 109 |

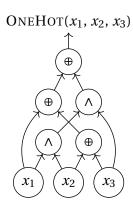

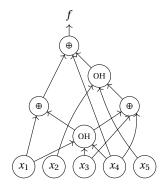

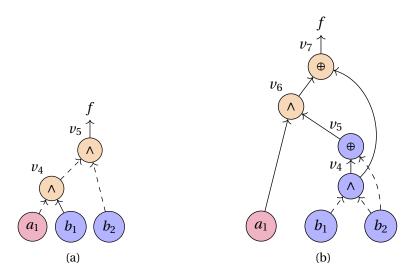

| 6.1 | Structural-MC-optimal XAG for ONEHOT                                                  | 128 |

| 6.2 | A wise choice of logic representation can lead to lower-cost garbled circuits         | 129 |

| 6.3 | Ciphertext-optimal implementations for #2888 <i>a</i> 000                             | 131 |

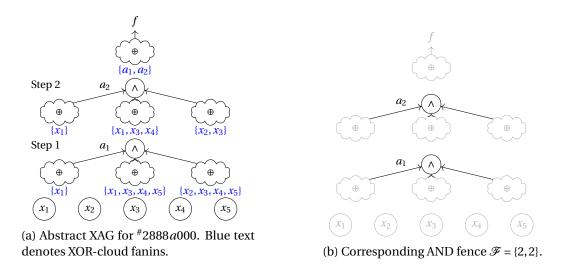

| 6.4 | Abstract XAG of the ciphertext-optimal implementations for #2888 <i>a</i> 000 and its |     |

|     | AND fence                                                                             | 133 |

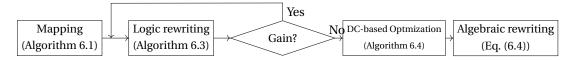

| 6.5 | Proposed flow for X1G optimization                                                    | 135 |

| 7.1 | Two MC-optimal XAGs for Boolean function $f$ , whose truth table is $^{\#}0b$ , under |     |

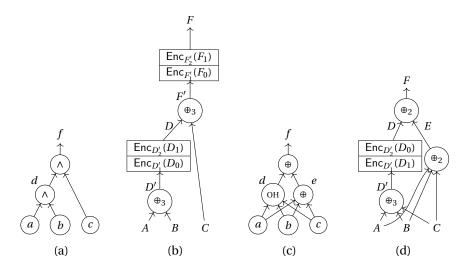

|     | the specified PI ownership.                                                           | 151 |

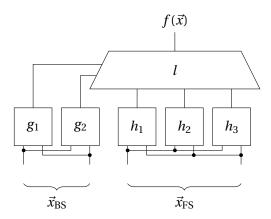

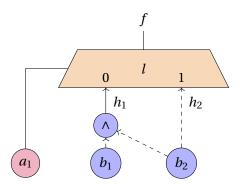

| 7.2 | Rephrased Ashenhurst-Curtis decomposition                                             | 154 |

| 7.3 | Deriving FS functions for the given variable partition                                | 155 |

| 7.4 | Partial circuit after deriving and synthesizing the FS and BS functions               | 157 |

# **List of Tables**

| 1.1 | Overview of the five technical chapters                                         | 22  |

|-----|---------------------------------------------------------------------------------|-----|

| 2.1 | Profile of the EPFL benchmark suite after MC-minimal XAG conversion             | 38  |

| 2.2 | Profile of the cryptographic benchmark suite after MC-minimal XAG conversion.   | 39  |

| 2.3 | Profile of the MPCircuit benchmark suite after MC-minimal XAG conversion        | 40  |

| 2.4 | Profile of the LOBSTER benchmark suite                                          | 41  |

| 3.1 | Nonlinear functions realizable by one abstract-XAG step as a function of avail- | 0.0 |

|     | able fan-in candidates                                                          | 60  |

| 3.2 | MC-aware MD minimization vs. prior art                                          | 69  |

| 3.3 | Effect of the flow's objective: leveled FHE cost vs. MD                         | 70  |

| 4.1 | Evaluating the three homomorphic circuit synthesis flows                        | 93  |

| 4.2 | Estimated evaluation cost of synthesized TFHE circuits                          | 95  |

| 5.1 | Comparison of TFHE circuit evaluation costs concerning the LOBSTER bench-       |     |

|     | mark suite                                                                      | 115 |

| 5.2 | Breakdown of PBS usage                                                          | 116 |

| 6.1 | Profile of the three-input symmetric candidates.                                | 127 |

| 6.2 | Synthesizing optimal X1Gs for the 48 representatives of five-variable spectral- |     |

|     | equivalence classes.                                                            | 138 |

| 6.3 | Results on EPFL benchmark suite                                                 | 140 |

| 6.4 | Results on Cryptographic & MPCircuit benchmark suites                           | 143 |

| 7.1 | Results on arithmetic and comparative benchmarks                                | 160 |

| 7.2 | Results on cryptographic and processor kernels                                  | 161 |

## **List of Acronyms**

**2PC** Two-Party Computation

ACD Ashenhurst–Curtis Decomposition

AES Advanced Encryption Standard

AIG And-Inverter Graph

**ASIC** Application-Specific Integrated Circuit

**BDD** Binary Decision Diagram

**BS** Bound Set

**CDC** Controllability Don't Care

**CMOS** Complementary Metal-Oxide-Semiconductor

CNN Convolutional Neural Network

CRT Chinese Remainder Theorem

**DAG** Directed Acyclic Graph

**DC** Don't Care

**DNN** Deep Neural Network

EDA Electronic Design Automation

ESOP Exclusive-or Sum of Product

**FFT** Fast Fourier Transform

**FHE** Fully Homomorphic Encryption

FL Federated Learning

FMC Functional Multiplicative Complexity

FPGA Field Programmable Gate Array

**FS** Free Set

**GC** Garbled Circuit

**GCD** Greatest Common Divisor

GLIFT Gate-Level Information Flow TrackingHDL Hardware Description Language

ILP Integer Linear Programming

IR Intermediate Representation

ISA Instruction Set Architecture

JMC Joint Multiplicative Complexity

**K-NN** K-Nearest-Neighbor

LSB Least Significant Bit LUT Look-Up Table

**LWE** Learning with Errors

MC Multiplicative Complexity

MD Multiplicative Depth

MFFC Maximum Fanout-Free ConeMIG Majority-Inverter GraphML Machine Learning

MLaaS Machine-Learning-as-a-Service

MSB Most Significant Bit

MV-PBS Multi-Value Programmable Bootstrapping

**NoC** Network on Chip

NTT Number Theoretic TransformODC Observability Don't CareOT Oblivious Transfer

**PBS** Programmable Bootstrapping

PI Primary InputPO Primary Output

PPA Performance, Power, and Area

RAM Random-Access Memory

RLWE Ring Learning with Errors

RNN Recurrent Neural Network

RNS Residue Number System

SAT Boolean Satisfiability

SIMD Single Instruction Multiple Data

SMC Structural Multiplicative Complexity

SMPC Secure Multi-Party Computation

SMT Satisfiability Modulo Theories

SOC Secure Outsourced Computation

**SS** Shared Set

SSV Single–Selection Variable

TLWE Torus Learning with Errors

**TFHE** Torus Fully Homomorphic Encryption

X1G Xor-OneHot-inverter Graph XAG Xor-And-inverter Graph

### 1 Introduction

Securing data privacy is a foundational requirement for contemporary computing and communication systems. Recent high-profile incidents illustrate the costs of inadequate protection, including the *2017 Equifax breach* that exposed the personal information of approximately 143 million individuals [96], and the *2023 MOVEit breach*, where an exploitation of the vulnerability within the *MOVEit Transfer* software resulted in hundreds of organizational breaches affecting tens of millions of people [161]. The genetic data exposure at *23andMe data leak* [97] further underscored risks unique to highly sensitive domains. These events collectively demonstrate both the scale and diversity of privacy harms that arise from compromised data.

Traditional encryption (e.g., the *advanced encryption standard* (AES) [141]) is highly effective for protecting *data at rest* and *data in transit*. However, during active processing, plaintext typically must be exposed to compute on it, creating a "data in use" gap that conventional mechanisms do not directly address. As a result, while data continue to drive innovation across domains, the inherently private nature of much of this data often prevents collaborative computation even when mutual benefit is clear.

The gap created a pressing need for *secure computation*, also known as *privacy-preserving computation*.

#### 1.1 Secure Computation Techniques

Secure computation refers to a class of techniques that enable the execution of computations on sensitive data while keeping the data itself confidential. Broadly, two paradigms organize the field:

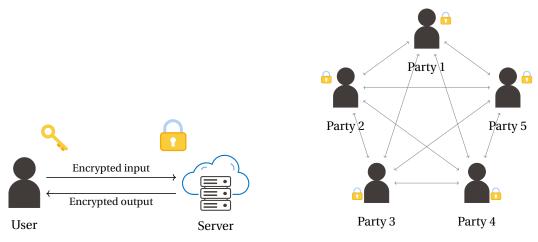

- *Secure outsourced computation* (SOC). A data owner delegates computation to an untrusted evaluator (e.g., a cloud service [74]) without revealing plaintext data. Figure 1.1 a depicts a typical SOC scenario.

- Secure multi-party computation (SMPC). Multiple parties, each holding private inputs,

(a) Secure outsourced computation.

(b) Secure multi-party computation.

Figure 1.1: Secure computation paradigms. (a) *secure outsourced computation* (SOC): a single client encrypts its data locally and outsources computation to an untrusted server that evaluates directly on protected data (e.g., via fully homomorphic encryption) without access to decryption keys; only encrypted results are returned. (b) *secure multi-party computation* (SMPC): multiple parties jointly compute a function over their private inputs using garbled circuits or related primitives; messages exchanged between parties remain cryptographically protected, and only the prescribed outputs are revealed. The lock icon indicates computation over protected data. The key icon denotes possession of the decryption capability. Arrows depict data flow.

jointly evaluate a function so that nothing is learned beyond the prescribed outputs. Figure 1.1 b illustrates a collaborative setting, where five participants exchange encrypted messages to compute a shared result without revealing their private inputs.

#### 1.1.1 Secure Outsourced Computation vs. Secure Multi-Party Computation

To illustrate the distinction between SOC and SMPC, we highlight two representative *machine learning* (ML) scenarios:

**SOC** for *ML-as-a-Service* (MLaaS): When a single data owner (namely, a client) wishes to offload intensive ML inference or training to an untrusted compute provider, SOC protects confidentiality by executing directly on encrypted inputs. Encryption schemes that support computation over ciphertexts allow the provider to evaluate the model without access to plaintext; the server returns only encrypted outputs, which only the client can decrypt. Early systems established feasibility for private inference [85]; subsequent work reduced latency and improved accuracy, including *hybrid* protocols that assign layers or operators to the most efficient secure primitive — mixing ciphertext-based computation with garbled circuits or secret-sharing, which are SMPC techniques, where advantageous — to lower end-to-end

cost [103, 132, 101].

**SMPC** for *federated learning* (FL): In cross-organizational or cross-device training, many parties collaboratively train a model without sharing raw data. A widely deployed primitive is *secure aggregation* [29], which lets a server learn only the sum of clients' updates while hiding each individual contribution. This protects local data while enabling scalable training across large client populations. Production systems demonstrate practicality at scale and motivate protocol/implementation research on communication efficiency, robustness to client dropouts, and adversarial robustness [30].

Although we contrasted two categories (i.e., SOC vs. SMPC), techniques from one can be adapted to the other. For instance, *multi-party homomorphic encryption* realizes SMPC-style tasks using SOC-native tools by enabling joint evaluation over ciphertexts with threshold decryption, thus reducing online interactivity [136, 135].

#### 1.1.2 Performance Limitations of Modern Secure Computation Techniques

The two broad styles of modern secure computation tend to hit very different bottlenecks in practice.

**SOC techniques: computation and memory are the limiters.** In SOC tasks, a single untrusted server (or a small set of servers) evaluates the function on encrypted inputs returned to the client at the end. With *fully homomorphic encryption* (FHE) [155], this evaluation is performed directly on ciphertexts. The required arithmetic (e.g., large-degree polynomial operations and periodic "refresh" steps to control encryption noise) remains orders of magnitude slower than ordinary arithmetic on plaintexts. Ciphertexts and keys are also much larger than their plaintext counterparts, so moving them through the memory hierarchy can become the dominant cost. Overall, FHE workloads tend to be *compute- and memory-bound*, not network-bound.

**SMPC techniques: communication is the limiter.** Protocols in which several parties jointly compute on their private inputs typically require the parties to exchange information repeatedly as the computation proceeds. Even when the number of exchanges ("rounds") is kept small, the *volume* of data that must be transmitted can be large. A prominent example is the *garbled circuit* protocol (GC) [190]: it compresses interaction into a few rounds, but each non-linear gate of the circuit is represented by encrypted table entries that must be sent over the network. In both cases — many small exchanges (which is the case of the *secret sharing* protocol [159]) or a few very large transfers — end-to-end performance is dominated by network latency and bandwidth rather than local computation.

The boundary is blurry, but the bottlenecks persist. As briefly mentioned before, techniques are often adapted across settings. For example, FHE can be used in multi-party protocols (e.g., threshold [9] and multi-party variants [136]), and, conversely, the GC protocol can be tuned to facilitate outsourcing computation privately [45, 84]. However, the dominant cost usually follows the primitive being used: FHE-based SMPC protocols remain limited by heavy encrypted computation and memory traffic, whereas SOC protocols built from GC or other SMPC-native techniques remain limited by data movement over the network.

**Scope of this thesis.** Given these performance bottlenecks, improving secure computation is both urgent and consequential. The community is attacking the problem across the stack. Before surveying this landscape, we briefly introduce the two workhorses we focus on in this thesis: *fully homomorphic encryption* (FHE), which enables computation over ciphertexts but is dominated by heavy encrypted arithmetic and memory traffic, and the *garbled circuits* protocol (GC), which evaluate Boolean circuits via encrypted lookup tables and are chiefly limited by data transfer. From this point forward, we reason directly in terms of FHE and GC (rather than the broader SOC/SMPC labels) and tailor our contributions to their characteristic performance profiles. Formal definitions and technical details for both will be introduced in Chapter 2.

#### 1.1.3 Fully Homomorphic Encryption

**Origins.** The idea of computing on encrypted data traces back to *privacy homomorphisms* [155] and early *partially* homomorphic schemes (e.g., systems that support either only additions or only multiplications on ciphertexts).

**Early general constructions.** A full solution arrived with Craig Gentry [82]: a construction over *ideal lattices*<sup>1</sup> that supports both operations and thus arbitrary circuits. Hiding a message by adding a small random *error* to a linear relation with a secret key, the security rests on the presumed hardness of certain lattice problems. Homomorphic operations transform ciphertexts and their error (a.k.a. noise):

- additions add the noises (and are therefore gentle),

- multiplications grow noise much faster (due to cross terms and rescaling).

Thus, without intervention, the noise eventually exceeds the decryption radius, breaking correctness. Correspondingly, Gentry also introduced *bootstrapping*: homomorphically evaluating (a low-depth version of) the decryption circuit to *refresh* a ciphertext's noise so further computation remains possible.

<sup>&</sup>lt;sup>1</sup>Very informally, a lattice is a discrete additive subgroup of  $\mathbb{R}^n$ ; an ideal lattice is a lattice whose basis vectors arise from a ring ideal.

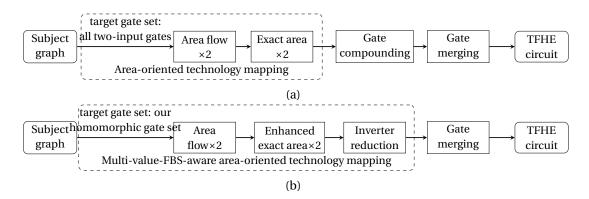

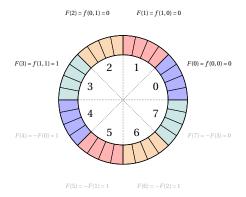

Shortly after, integer-based designs by Marten van Dijk et al. [73] showed FHE can be built without polynomial rings — the plaintext is a bit, ciphertexts are noisy integers, and homomorphic operations are just addition and multiplication of integers. Security relies on the *approximate greatest common divisor* (approximate-GCD) problem: given many integers of the form  $x_i = p \cdot q_i + r_i$ , where the secret p is fixed and the "errors"  $r_i$  are small, it should be hard to recover p. Despite being conceptually simple, it is far too slow for practical workloads — to achieve even modest security, p must be enormous, resulting in prohibitively large ciphertexts and, therefore, correspondingly slow homomorphic operations.