# Robustness Analysis of Controllable-Polarity Silicon Nanowire Devices and Circuits

### THÈSE Nº 6924 (2016)

PRÉSENTÉE LE 8 AVRIL 2016

À LA FACULTÉ INFORMATIQUE ET COMMUNICATIONS LABORATOIRE DES SYSTÈMES INTÉGRÉS (IC/STI) PROGRAMME DOCTORAL EN INFORMATIQUE ET COMMUNICATIONS

### ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES

#### PAR

### Hassan GHASEMZADEH MOHAMMADI

acceptée sur proposition du jury:

Prof. B. Falsafi, président du jury Prof. G. De Micheli, directeur de thèse Prof. M. Sonza Reorda, rapporteur Prof. M. Nicolaidis, rapporteur Prof. D. Atienza Alonso, rapporteur

To Maryam for her endless love, and to the memory of my father, Ahmad

# Acknowledgements

This thesis was a unique adventure during my study at EPFL. This work could not be done without the help and support of many people. Collaborating, discussing, and working with such great colleagues were invaluable experience during the last 4 years.

I would particularly like to thank my supervisor Prof. Giovanni De Micheli for all of his supports, guides and time for constructive discussions. He was a constant source of support and encouragement during the challenges of my research.

Working with a knowledgeable person like Prof. Pierre-Emmanuel Gaillardon is always a remarkable experience. I would like to thank him for his tremendous guides and supports. I would also appreciate my examiners, Prof. Babak Falsafi, Prof. David Atienza Alonso, Prof. Matteo Sonza Reorda, and Prof. Michael Nicolaidis, who provided encouraging and beneficial feedbacks.

My colleagues at EPFL have a significant role in my project. I wish to thank Dr. Majid Yazdani and Dr. Sara S. Ghoreishizadeh. It has been a great pleasure working with them.

My greatest thanks go to all the members of *Integrated System Laboratory* (LSI) for the wonderful moments I spent with them. Moreover, I specially thank Christina Govoni for all tremendous help and administrative support during my PhD and also my dear friends in LSI. My stay at Lausanne would not have been pleasing without the great time spent with Somayyeh, Mahdi, Amin, Nima, Sahar, Ardalan, Samira, Afsaneh, Mohammad-Javad, Glareh, Peyman and all of my lovely friends. I wish the best for you in your life.

I would like to thank my family, my mother, brother and sister, for their unconditional support, and encouragement, without which I would not have come this far. Maryam, with her endless love and support, has always been the greatest inspiration in my life. Without her companionship and love, I would not have been able to reach this end.

Hassan Ghasemzadeh Mohammadi Lausanne, January 2016

# **Abstract**

Substantial downscaling of the feature size in current CMOS technology has confronted digital designers with serious challenges including short channel effect and high amount of leakage power. To address these problems, emerging nano-devices, e.g., *Silicon NanoWire FET* (SiNWFET), is being introduced by the research community. These devices keep on pursuing Moore's Law by improving channel electrostatic controllability, thereby reducing the *Off*-state leakage current. In addition to the improvements in conventional device performances, recent developments introduced devices with enhanced capabilities such as *Controllable-Polarity* (CP) SiNWFETs. In particular, these transistors support in-field reconfiguration which makes them very interesting for compact logic cell and arithmetic circuits.

At advanced technology nodes, fabrication-induced variations are expected to significantly affect the yield of complex circuits. Indeed, the amount of physical controls, during the fabrication process of nanometer devices, cannot be precisely determined because of technology fluctuations. Consequently, the physical and structural parameters of fabricated circuits can be significantly different from their nominal values. Moreover, giving an *a-priori* conclusion on the variability of advanced technologies for emerging nanoscale devices, with novel geometries and different fabrication process, is a difficult task and novel estimation methodologies are required. This is a necessity to guarantee the performance and the reliability of future integrated circuits.

Statistical analysis of process variation requires a great amount of numerical data for nanoscale devices. This introduces a serious challenge for variability analysis of emerging technologies due to the lack of fast simulation models. One the one hand, the development of accurate compact models entails numerous tests and costly measurements on fabricated devices. On the other hand, *Technology Computer Aided Design* (TCAD) simulations, that can provide precise information about devices behavior, are too slow to timely generate large enough data set. In this research, a fast methodology for generating data set for variability analysis is introduced. This methodology combines the TCAD simulations with a learning algorithm to alleviate the time complexity of data set generation for emerging nano-devices.

Another formidable challenge for variability analysis of the large circuits is growing number of process variation sources in deeply nanoscale technologies. Utilizing parameterized models is becoming a necessity for chip design and verification. However, the high dimensionality of parameter space imposes a serious problem. Unfortunately, the available dimensionality reduction techniques cannot be employed for three main reasons of lack of accuracy, distribution dependency of the data points, and finally incompatibility with device and circuit

#### Acknowledgements

simulators. We propose a novel technique of parameter selection for modeling process and performance variation. The proposed technique efficiently takes into account the nonlinearity among process and performance parameters which is necessary for high precision variation analysis.

Appropriate testing, to capture manufacturing defects, plays an important role on the quality of integrated circuits. Compared to conventional CMOS, emerging nano-devices such as CP-SiNWFETs have different fabrication process steps. Therefore, the type of defects for these technologies is different from CMOS devices. In this case, current fault models must be extended for defect detection of emerging technologies. In this research, we investigated the inefficiency of the current CMOS fault models for detecting the fabrication defects of CP-SiNWFET technology. Considering the fabrication steps, we extracted the possible fabrication defects, and then proposed a fault model for this technology. We also provided a couple of test methods for detecting the manufacturing defects in various types of CP-SiNWFET logic gates. Finally, we used the obtained fault model to build fault tolerant arithmetic circuits with a bunch of superior properties compared to their competitors.

Key words: Controllable-Polarity Silicon Nanowire, 3-D TCAD Simulation, Process Variation, Statistical Analysis, Circuit Modeling, Fault Models, Arithmetic Circuits.

# Résumé

L'importante réduction de la taille aus la technologie CMOS actuelle a confronté les concepteurs numériques à de sérieux défis tels que l'effet de canal court, ainsi qu'une des transistors à importante puissance de fuite. Pour résoudre ces problèmes, de nouveaux nanodispositifs, p.ex., Nanofils de Silicium (SiNWFET), ont été présentés par la communauté de recherche. Ces dispositifs continuent de suivre la loi de Moore tout en améliorant la contrôlabilité électrostatique du canal, réduisant ainsi le courant de fuite à l'état ouvert. En plus des améliorations de performances des dispositifs classiques, une évolution récente a introduit des dispositifs qui sont dotés de fonctionnalités améliorées comme les SiNWFETs polarité contrôlable (CP). En particulier, ces transistors supportent une reconfiguration dynamique ce qui les rendent très intéressants pour la réalisation de cellules logique compactes, ainsi que pour les circuits arithmétiques.

A des nœuds technologiques avancés, les variations induites par la fabrication devraient affecter de manière significative le rendement des circuits complexes. En effet, la quantité des contrôles physiques, durant le processus de fabrication des dispositifs nanométriques ne peut être déterminée avec précision en raison des fluctuations de la technologie. Par conséquent, les paramètres physiques et structurelles des circuits fabriqués peuvent être sensiblement différents de leurs valeurs nominales. En outre, donner une conclusion a-priori sur la variabilité des technologies de pointes utilisant de nouvelles géométries et des processus de fabrication différents, est une tâche difficile et de nouvelles méthodes d'estimation sont nécessaires. C'est une nécessité pour garantir les performances et la fiabilité des futurs circuits intégrés.

L'analyse statistique des variations de fabrication pour les dispositifs nanométriques nécessite une grande quantité de données à traiter. Ceci introduit un sérieux défi pour l'analyse de la variabilité des technologies émergentes en raison de l'absence de modèles de simulation rapide. D'une part, le développement de modèles compacts et précis implique de nombreux tests et des characterisation coûteuses sur les dispositifs fabriqués. D'autre part, les simulations de type TCAD, qui pourraient fournir des informations précises sur le comportement des dispositifs sont trop lentes pour produire un ensemble de données suffisamment large. Dans ces travaux de recherche, une méthode rapide de création de l'ensemble des données pour l'analyse de la variabilité est introduite. Cette méthode combine les simulations TCAD avec un algorithme d'apprentissage pour atténuer la complexité associée a la création de l'ensemble des données adaptées aux nano-dispositifs émergents.

Un autre défi de taille pour l'analyse de la variabilité des grands circuits est le nombre croissant

#### Acknowledgements

des sources de variation de fabrication dans les technologies nanométriques. Utiliser des modèles paramétrés devient une nécessité pour la conception de puces et de vérification. Toutefois, la grande dimensionnalité de l'espace des paramètres pose un sérieux problème. Malheureusement, les techniques de réduction de l'espace de paramèters disponibles ne peuvent être employées pour trois principales raisons : le manque d'exactitude, la dépendance de distribution des points de données, et enfin l'incompatibilité avec les simulateurs de dispositifs et de circuits. Nous proposons une nouvelle technique de sélection de paramètres pour la modélisation du la variabilité. La technique proposée prend efficacement en compte la nonlinéarité entre et les paramètres de performances qui est nécessaire pour l'analyse de variation de haute précision.

Des tests appropriés pour capturer les défauts de fabrication jouent un rôle important sur la qualité de circuits intégrés. Par rapport aux systèmes CMOS classiques, les nano-dispositifs émergents tels que CP-SiNWFETs ont différentes étapes de fabrication. Par conséquent, le type de défaut pour ces technologies est différent des dispositifs CMOS. Dans ce cas, des modèles de faute adaptés doivent être employés pour la détection des défauts dans les technologies émergentes. Dans cette recherche, nous avons identifié l'inefficacité des modèles de faute CMOS actuels pour la détection des défauts de fabrication de la technologie CP-SiNWFET. En considérant les étapes de fabrication, nous avons extrait les défauts de fabrication possibles, et nous avons ensuite proposé un modèle de faute pour cette technologie. Nous avons également fourni deux méthodes d'essai pour détecter les défauts de fabrication dans divers types de portes logiques à base de CP-SiNWFET. Enfin, nous avons utilisé le modèle de faute obtenu pour construire des circuits arithmétique insensibles aux défaillances avec beaucoup de propriétés supérieures par rapport à leurs concurrents.

Mots cléfs : Transistors à Polarité Contrôlable à base de Nanofils de Silicium , Simulation 3-D TCAD, Variabilité, Analyse Statistique, Modélisation du Circuit, Modèles de Faute, Circuits arithmétiques.

# Contents

| Ac | cknov | vledge  | ments                                                                          | V   |

|----|-------|---------|--------------------------------------------------------------------------------|-----|

| Ał | ostra | ct (Eng | glish/Français)                                                                | vii |

| Li | st of | figures |                                                                                | xv  |

| Li | st of | tables  |                                                                                | xix |

| 1  | Intr  | oducti  | on                                                                             | 1   |

|    | 1.1   | Evolu   | tion of Transistor Technologies                                                | 2   |

|    |       | 1.1.1   | CMOS Advanced Devices                                                          | 3   |

|    |       | 1.1.2   | Emerging Devices                                                               | 5   |

|    | 1.2   | Challe  | enges of Emerging Technologies                                                 | 6   |

|    |       | 1.2.1   | Process Variation                                                              | 6   |

|    |       | 1.2.2   | Manufacturing Defects                                                          | 11  |

|    | 1.3   | Deali   | ng with Process Variation and Fabrication Defects                              | 12  |

|    | 1.4   | Thesi   | s Contribution                                                                 | 14  |

|    | 1.5   | Thesi   | s Organization                                                                 | 14  |

| 2  | Con   | trollal | ble-Polarity Silicon Nanowire FET: Background and Robustness Analysis          | 17  |

|    | 2.1   | Intro   | duction                                                                        | 17  |

|    | 2.2   | Fabri   | cation Process                                                                 | 19  |

|    | 2.3   | Electr  | rical Simulation                                                               | 20  |

|    | 2.4   | 0       | Gate Realization in CP-SiNWFET Technology                                      | 23  |

|    | 2.5   | Variat  | tion Sources                                                                   | 24  |

|    | 2.6   | Devic   | es Robustness                                                                  | 27  |

|    |       | 2.6.1   | Experimental Setup and Simulation Results                                      | 27  |

|    |       | 2.6.2   | $\mathcal{I}_{ON}$ of DG-SiNWFET and Doped SiNWFET in Presence of Variation on |     |

|    |       |         | Length of Nanowires                                                            | 28  |

|    |       | 2.6.3   | $I_{Off}$ of DG-SiNWFET and Doped SiNWFET in Presence of Variation on          |     |

|    |       |         | Length of Nanowires                                                            | 30  |

|    |       | 2.6.4   | $V_{Th}$ of DG-SiNWFET and Doped SiNWFET in Presence of Variation on           | -   |

|    |       |         | Length of Nanowires                                                            | 31  |

#### **Contents**

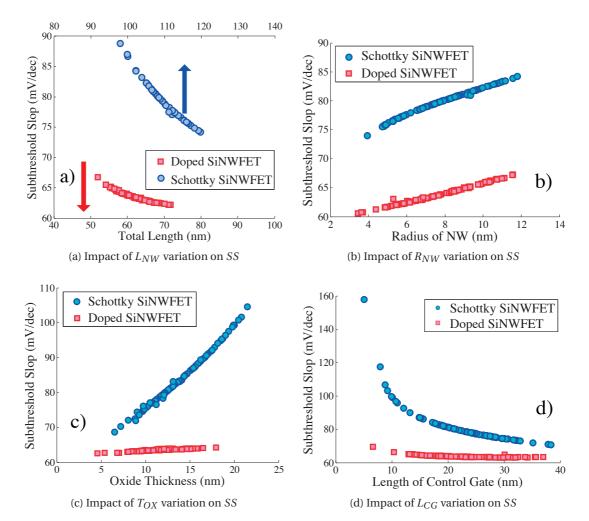

|   |      | 2.6.5  | Subthreshold Slope of DG-SiNWFET and Doped SiNWFET in Presence of     |    |

|---|------|--------|-----------------------------------------------------------------------|----|

|   |      |        | Variation on Length of Nanowires                                      | 32 |

|   | 2.7  | Sumn   | nary                                                                  | 33 |

| 3 | A Fa | st Met | hodology for Variation Analysis of Emerging Nano-Devices              | 35 |

|   | 3.1  | Introd | luction                                                               | 35 |

|   | 3.2  | Backg  | ground and Motivation                                                 | 36 |

|   |      | 3.2.1  | Problem: Difficulty of Generating Statistical Information             | 36 |

|   |      | 3.2.2  | Previous Work                                                         | 36 |

|   | 3.3  | Learn  | ing-based Methodology for Fast Process Variation Analysis of Emerging |    |

|   |      | Devic  | es                                                                    | 37 |

|   |      | 3.3.1  | PV Analysis Using Neural Networks                                     | 37 |

|   |      | 3.3.2  | Neural Network Structure                                              | 39 |

|   |      | 3.3.3  | Training of the Neural Network                                        | 40 |

|   | 3.4  | Resul  | t and Discussion                                                      | 41 |

|   |      | 3.4.1  | Setup of Experiments                                                  | 41 |

|   |      | 3.4.2  | Experimental Results                                                  | 44 |

|   | 3.5  | Sumn   | nary                                                                  | 46 |

| 4 | Para | ametei | Selection for Nonlinear Modeling of Process Variation                 | 49 |

|   | 4.1  | _      | ground and Motivation                                                 | 50 |

|   |      | 4.1.1  | Principal Component Analysis (PCA)                                    | 51 |

|   |      | 4.1.2  | Independent Component Analysis (ICA)                                  | 52 |

|   |      | 4.1.3  | Canonical Correlation Analysis (CCA)                                  | 53 |

|   |      | 4.1.4  | Sparse Linear Regression via $\ell_1$ -Norm Regularization            | 54 |

|   |      | 4.1.5  | Parameter Reduction for PV Analysis                                   | 55 |

|   | 4.2  |        | ing-based Parameter Reduction for Fast Variation Analysis of Emerging |    |

|   |      |        | es                                                                    | 56 |

|   |      |        | Parameter Reduction towards Low Dimensional Device and Circuit Models | 56 |

|   |      | 4.2.2  | Nonlinear Regression via Feed Forward Neural Network                  | 58 |

|   |      | 4.2.3  | Learning Algorithm for Nonlinear Optimization                         | 58 |

|   |      | 4.2.4  | Validation via 10-fold Cross-Validation                               | 59 |

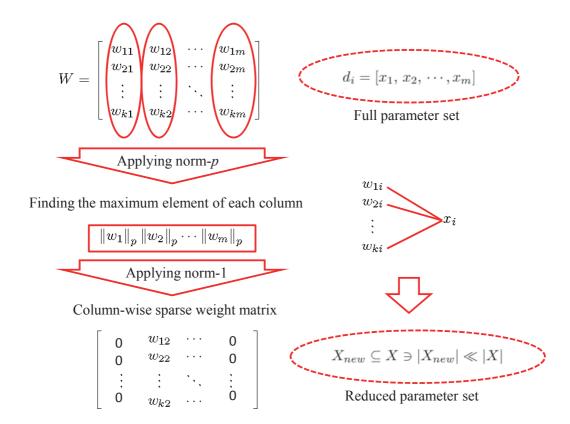

|   |      | 4.2.5  | Column-Wise Sparse Parameter Selection                                | 59 |

|   |      | 4.2.6  | Nonlinear Column-Wise Sparse Parameter Selection                      | 60 |

|   | 4.3  | Exper  | imental Results                                                       | 61 |

|   |      | 4.3.1  | PV analysis for FinFET Technology                                     | 61 |

|   |      | 4.3.2  | PV analysis for Double-Gate Silicon Nanowire Technology               | 65 |

|   | 4.4  | Sumn   | nary                                                                  | 69 |

| 5 | Def  |        | alysis and Fault Modeling for Controllable-Polarity Silicon Nanowires | 71 |

|   | 5.1  |        | luction                                                               | 71 |

|   | 5.2  | _      | ground and Motivation                                                 | 72 |

|   | 5.3  | Manu   | facturing Defects of TIG-SiNWFETs: from Device to Logic Cells         | 72 |

|    |       | 5.4.1 Gate Oxide Short in CP-SiNWFETs                                         | 74         |

|----|-------|-------------------------------------------------------------------------------|------------|

|    |       | 5.4.2 Open CGs and PGs on the SP and DP logic gates                           | 79         |

|    |       | 5.4.3 Bridging Defects Characterization in the SP and DP Logic Gates          | 82         |

|    |       | 5.4.4 Channel Break in the SP and DP Logic Gates                              | 82         |

|    | 5.5   | Summary                                                                       | 84         |

| 6  | Des   | ign of a Fault Tolerant Ripple-Carry Adder with Controllable-Polarity Transis | <b>3</b> - |

|    | tors  |                                                                               | 87         |

|    | 6.1   | Introduction                                                                  | 87         |

|    | 6.2   | Background and Motivation                                                     | 88         |

|    | 6.3   | Evaluating Controllable-Polarity Circuit Robustness                           | 89         |

|    |       | 6.3.1 Fault Model for Functionality Evaluation                                | 89         |

|    |       | 6.3.2 XOR/MAJ Gates Robustness                                                | 90         |

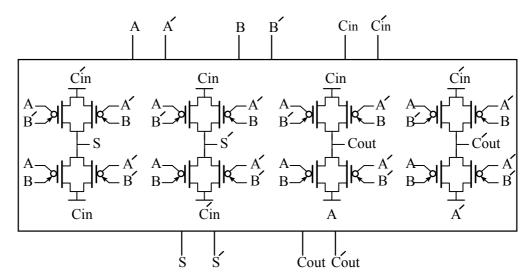

|    | 6.4   | Fault-tolerant Ripple-carry Adder Architecture                                | 94         |

|    | 6.5   | Quantitative Analysis                                                         | 96         |

|    | 6.6   | Summary                                                                       | 97         |

| 7  | Con   | clusion                                                                       | 99         |

|    | 7.1   | Thesis Conclusion                                                             | 99         |

|    | 7.2   | Further Directions                                                            | 101        |

| Bi | bliog | raphy                                                                         | 111        |

|    |       |                                                                               |            |

# **List of Figures**

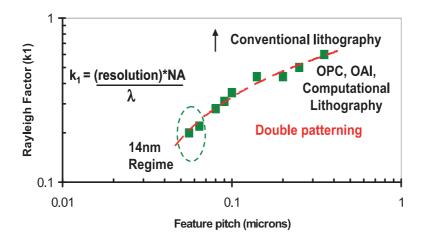

| 1.1        | The complexity of lithography for 14nm scaling and beyond                             | 2  |

|------------|---------------------------------------------------------------------------------------|----|

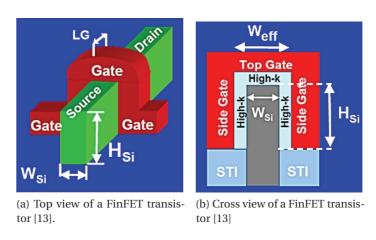

| 1.2        | 3-D structure of a FinFET Transistor                                                  | 3  |

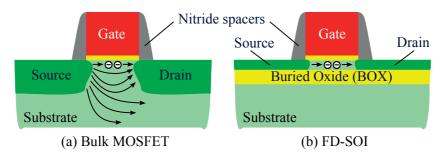

| 1.3        | Comparison of the of the carrier transportation in the channel: (a) bulk MOSFET,      |    |

|            | and (b) FD-SOI                                                                        | 4  |

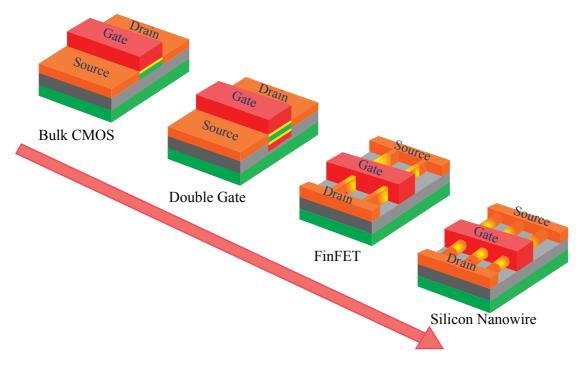

| 1.4        | The increase of geometrical complexities for future nano-devices                      | 4  |

| 1.5        | Three-dimensional structure of a typical $MoS_2$ transistor and the channel struc-    |    |

|            | ture                                                                                  | 6  |

| 1.6        | The impact of parameter variation on the performance of a device and circuit.         | 7  |

| 1.7        | Mask patterning restriction as a source of variation                                  | 7  |

| 1.8        | Mask patterning restriction causes rounding effect on the transistor gate and         |    |

|            | vastly increases the leakage current in 65 nm technology.                             | 8  |

| 1.9        | The exponential increase of the number of transistor per IO pin for microproces-      |    |

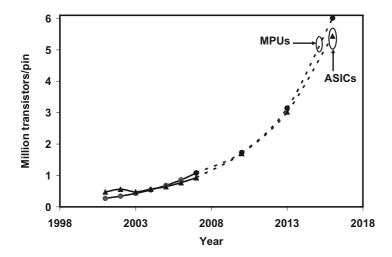

|            | sors and ASICs as a challenge of test for future technologies.                        | 12 |

| 1.10       | Challenges of emerging technologies for future integrated circuits                    | 13 |

| 2 1        | The 2D etweeture of TIC CINIMEET along with the corresponding geometrical             |    |

| 2.1        | The 3D structure of TIG-SiNWFET along with the corresponding geometrical parameters.  | 18 |

| <b>1</b> 1 |                                                                                       |    |

| 2.2        | •                                                                                     | 19 |

| 2.3        | •                                                                                     | 21 |

| 2.4        |                                                                                       | 21 |

| 2.5        | •                                                                                     | 22 |

| 2.6        | · · ·                                                                                 | 22 |

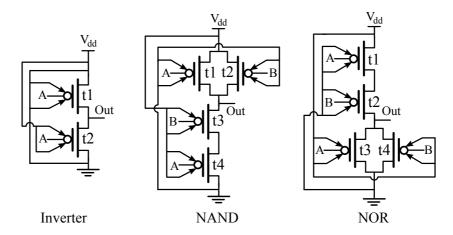

| 2.7        | Logic gate realization in TIG-SiNWFET. Inverter, NAND, and NOR gates are the          | വ  |

| 2.0        |                                                                                       | 23 |

| 2.8        | Logic gate realization in TIG-SiNWFET. 2-input XOR, 3-input XOR and Majority          | 22 |

| 2.0        |                                                                                       | 23 |

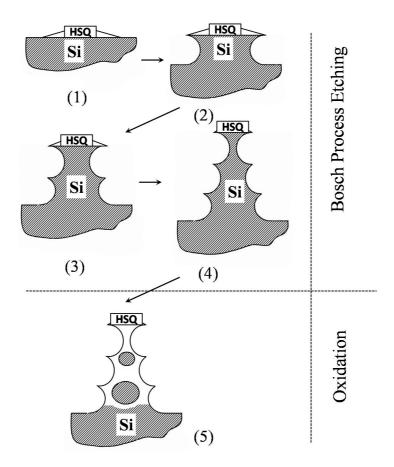

| 2.9        | Variation on $R_{NW}$ due to the dry etching with Bosch process. In top of the stack, | 25 |

| 2 10       |                                                                                       | 25 |

| 2.10       | An SEM figure of the fabricated DG-SiNWFET which clearly shows the variations         | 20 |

| 0 11       | 0 1 70                                                                                | 26 |

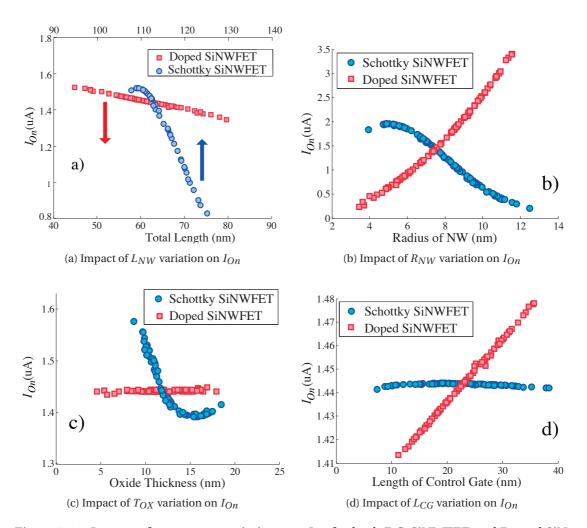

|            | Impact of parameter variations on $I_{On}$ for both DG-SiNWFET and Doped SiNWFET.     | 29 |

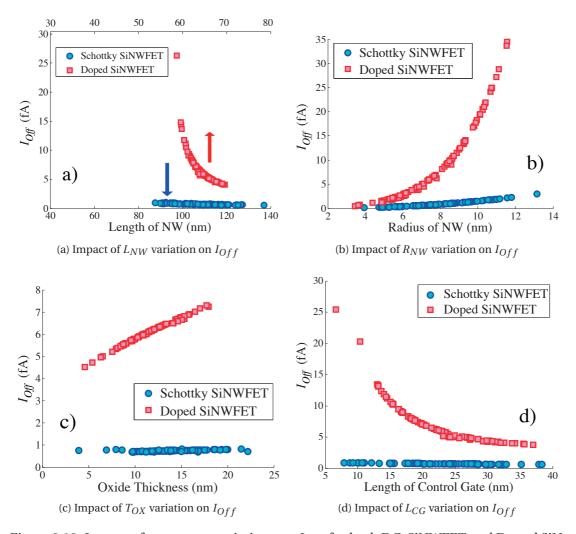

| 2.12       | Impact of parameter variations on $I_{Off}$ for both DG-SiNWFET and Doped SiN-        | 20 |

|            | WFET                                                                                  | 30 |

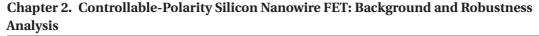

| 2.13 | Impact of parameter variations on $V_{Th}$ for both DG-SiNWFET and Doped SiNWFET                                                                                                                                                                                                                                     | 32 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.14 | Impact of parameter variations on $SS$ for both DG-SiNWFET and Doped SiNWFET.                                                                                                                                                                                                                                        | 33 |

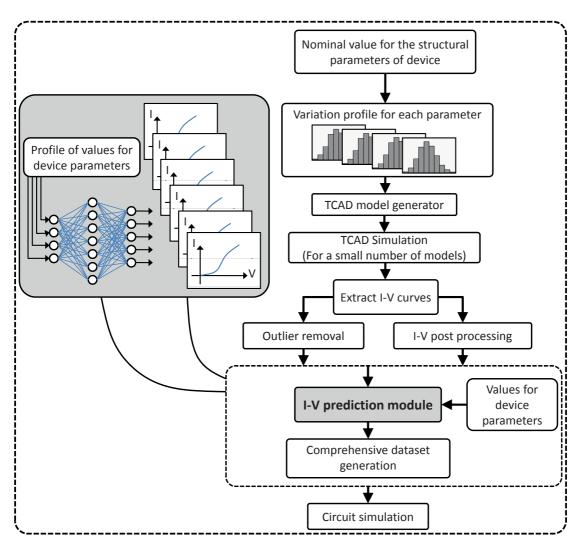

| 3.1  | Flowchart of the proposed methodology                                                                                                                                                                                                                                                                                | 38 |

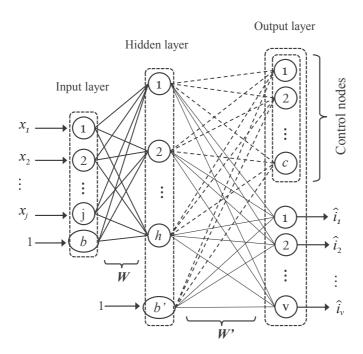

| 3.2  | Graphical representation of the FFNN for I-V curve regression                                                                                                                                                                                                                                                        | 40 |

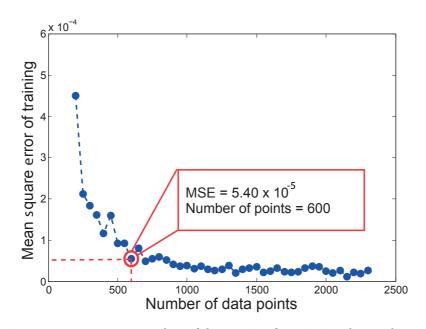

| 3.3  | Necessary number of data points for training the predictor                                                                                                                                                                                                                                                           | 42 |

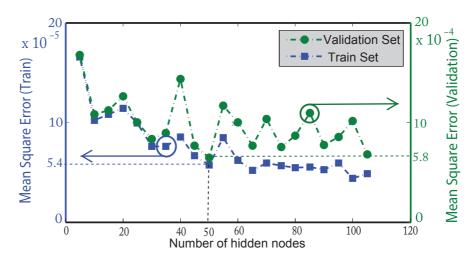

| 3.4  | Mean square error of training and test sets for networks with various number of hidden nodes                                                                                                                                                                                                                         | 43 |

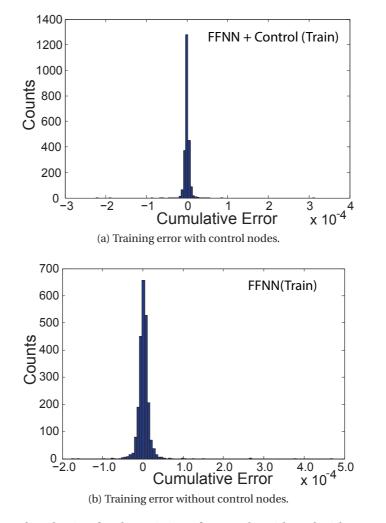

| 3.5  | Error distribution for the training of networks with and without control nodes.                                                                                                                                                                                                                                      | 43 |

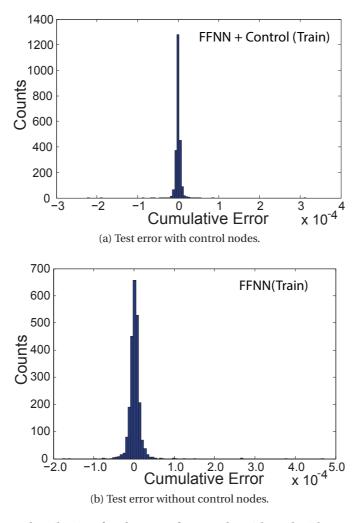

| 3.6  | Error distribution for the test of networks with and without control nodes                                                                                                                                                                                                                                           | 44 |

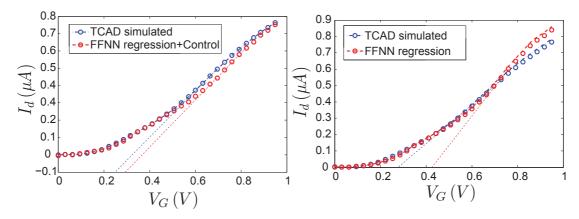

| 3.7  | Two sample I-V regression through different FFNNs. Adding control nodes to                                                                                                                                                                                                                                           | 45 |

| 2.0  | FFNNs results in more precise prediction.                                                                                                                                                                                                                                                                            |    |

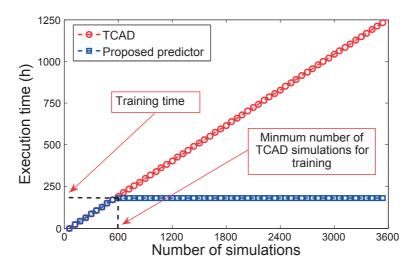

| 3.8  | Runtime comparison of the TCAD simulation with proposed methodology                                                                                                                                                                                                                                                  | 46 |

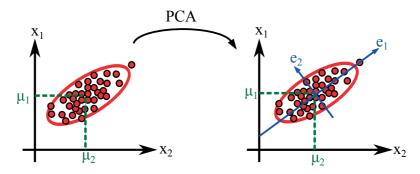

| 4.1  | The visual representation of the PCA. PCA finds the eigenvectors of the covariance matrix $\Sigma$ . The obtained orthogonal vectors represent the directions in which the variations of input parameters are maximized                                                                                              | 52 |

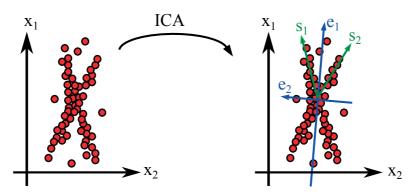

| 4.2  | The visual representation of the ICA. ICA computes the independent components like $s_1$ and $s_2$ which can be used for parameter selection of non-Gaussian                                                                                                                                                         |    |

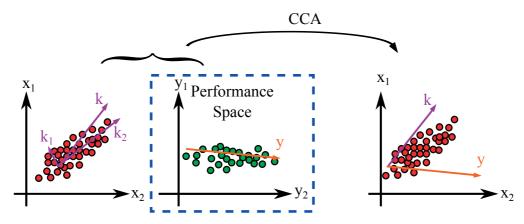

| 4.3  | distributions. Here, the obtained components are not necessarily orthogonal  The visual representation of the CCA. CCA considers the variation of output parameters in the performance space and tries to find the components that have larger impacts on the output variation. Indeed, CCA performs an output aware | 53 |

| 4.4  | parameter reduction using linear correlations                                                                                                                                                                                                                                                                        | 54 |

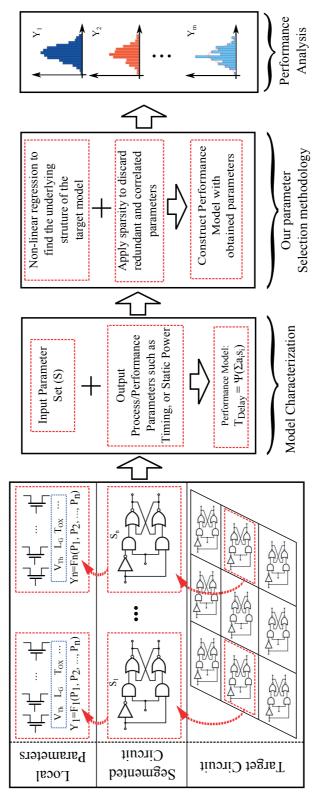

| 4.4  | General flow of the parameter reduction towards a fast and efficient process variation analysis                                                                                                                                                                                                                      | 57 |

| 4.5  | The role of norm-p regularization in weight matrix for feature selection                                                                                                                                                                                                                                             | 60 |

| 4.6  | Longest path in ITC'99 b03 benchmark                                                                                                                                                                                                                                                                                 | 62 |

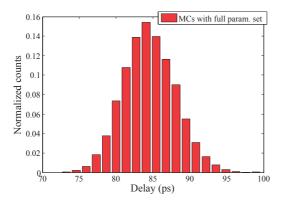

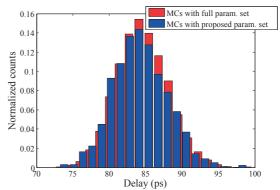

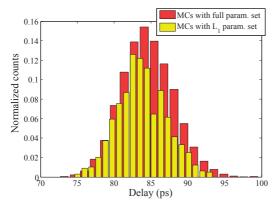

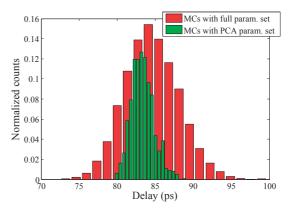

|      | Distribution of longest path delay for benchmark b03 before and after parameter selection: (a) full parameter set, (b) proposed method parameter set, (c) $\ell_1$ -norm                                                                                                                                             |    |

|      | regularization parameter set, and (d) PCA parameter set                                                                                                                                                                                                                                                              | 65 |

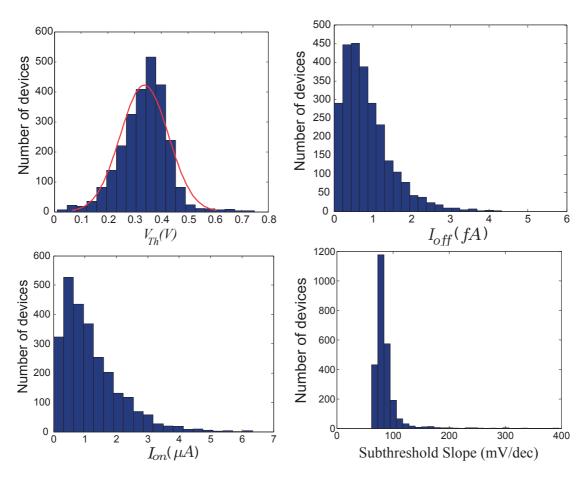

| 4.8  | Distribution of $V_{Th}$ , $I_{off}$ , $I_{on}$ , and SS for DG-SiNWFET ( $\sigma$ =30% for structural                                                                                                                                                                                                               |    |

| 1.0  | parameters). Only the variation of $V_{Th}$ follows a Gaussian distribution                                                                                                                                                                                                                                          | 66 |

| 4.9  | ISCAS89 benchmark circuit s27 using DG-SiNWFET technology                                                                                                                                                                                                                                                            | 67 |

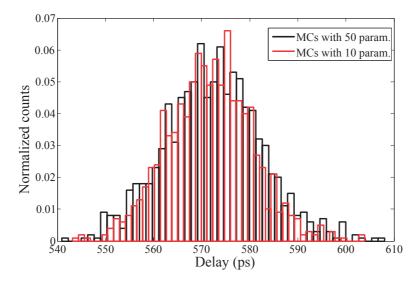

| 4.10 | Delay distribution comparison of the full and the reduced parameter models                                                                                                                                                                                                                                           | 68 |

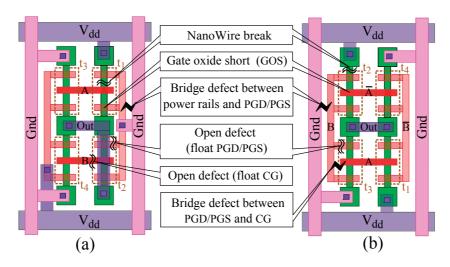

| 5.1  | Layouts of the NOR (a) and 2-input XOR (b), based on the SoT method, with several possible defects.                                                                                                                                                                                                                  | 74 |

| 5.2  | Behavior of defective <i>n</i> -type TIG-SiNWFETs in the presence of GOS: (a) GOS                                                                                                                                                                                                                                    |    |

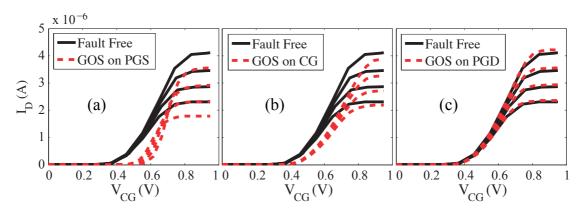

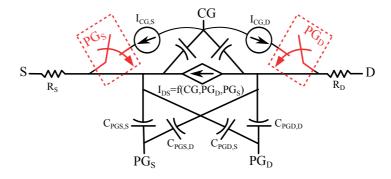

|      | under $PG_S$ , (b) GOS under $CG$ , and (c) GOS under $PG_D$                                                                                                                                                                                                                                                         | 75 |

| 5.3  | Nonlinear piecewise model of GOS under <i>CG</i> for n-type TIG-SiNWFETs. The        |    |

|------|--------------------------------------------------------------------------------------|----|

|      | switches are necessary to realize the impact of the polarity gates on the leakage    |    |

|      | of defective device in DP logics                                                     | 75 |

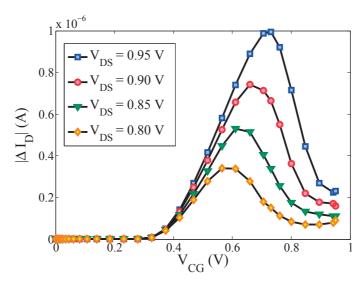

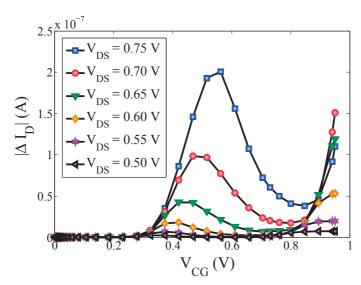

| 5.4  | Difference of $I_D$ with and without GOS under CG versus $V_{CG}$                    | 77 |

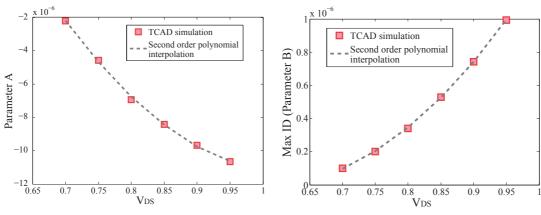

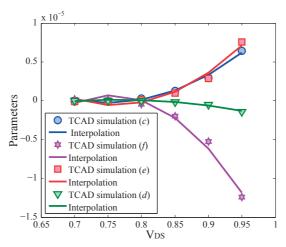

| 5.5  | Parameters of the GOS model estimator as a function of $V_{DS}$ . All the parameters |    |

|      | can be interpolated with second order polynomials                                    | 78 |

| 5.6  | GOS occurrence in CG of the pull-down transistor of an Inverter                      | 79 |

| 5.7  | GOS occurrence in CG of a pull-down transistor (t3) of an XOR                        | 79 |

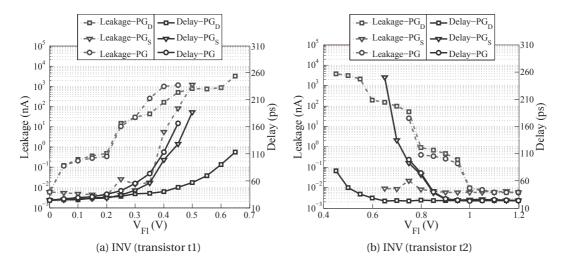

| 5.8  | Leakage-delay variation with different biases on $PG_S$ and $PG_D$ of an Inverter    |    |

|      | gate in TIG-SiNWFET technology.                                                      | 80 |

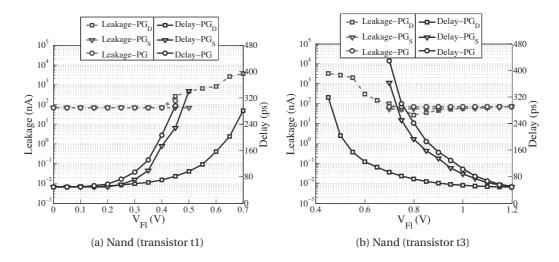

| 5.9  | Leakage-delay variation with different biases on $PG_S$ and $PG_D$ of a Nand gate in |    |

|      | TIG-SiNWFET technology                                                               | 81 |

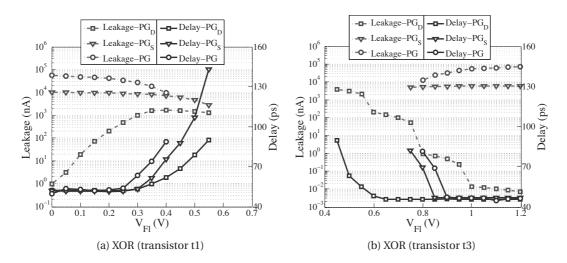

| 5.10 | Leakage-delay variation with different biases on $PG_S$ and $PG_D$ of a XOR gate in  |    |

|      | TIG-SiNWFET technology                                                               | 82 |

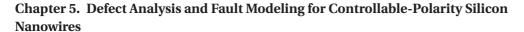

| 5.11 | Nanowire break defect detection using a pair of two-pattern test                     | 84 |

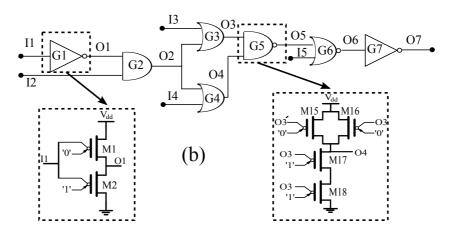

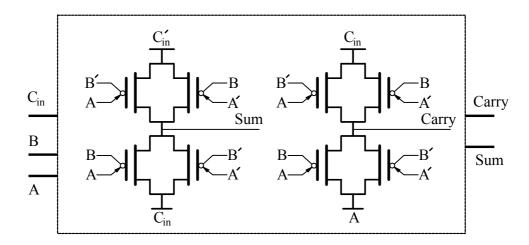

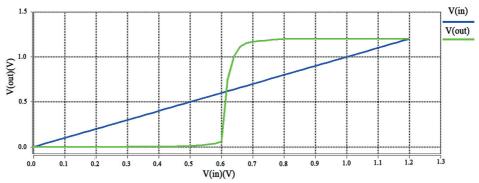

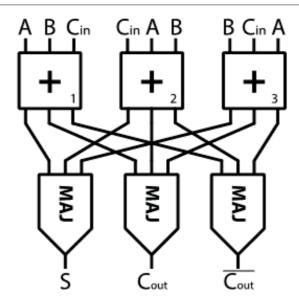

| 6.1  | Realization of 1-bit Full adder in CP-SiNWFET technology.                            | 89 |

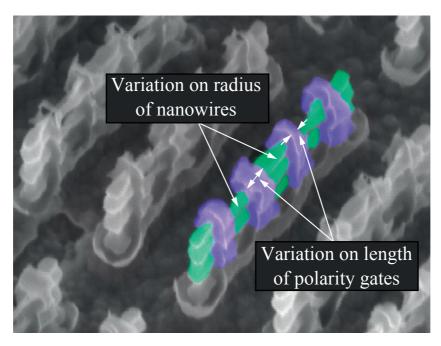

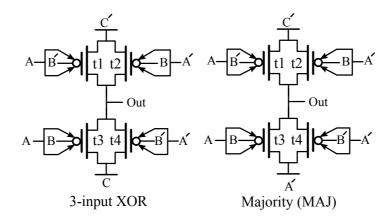

| 6.2  | 3-input XOR and Majority (MAJ) logic gates in CP-SiNWFET technology                  | 90 |

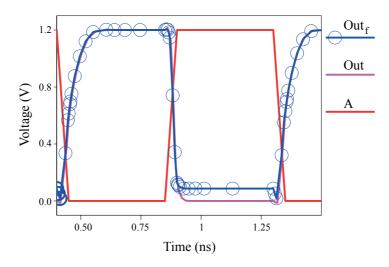

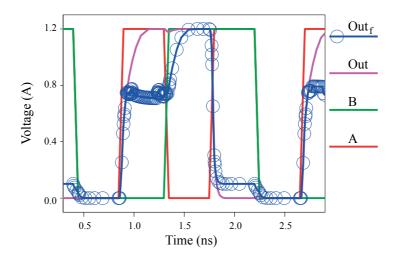

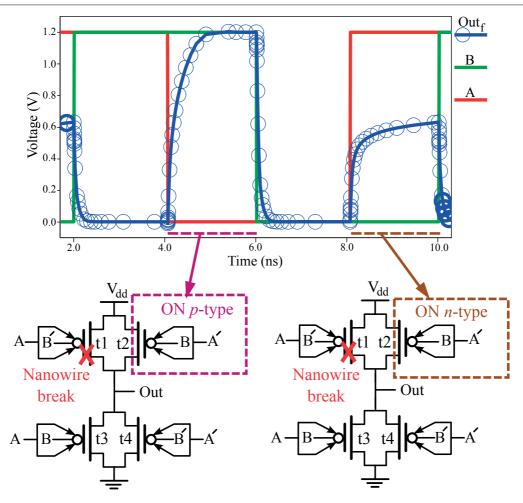

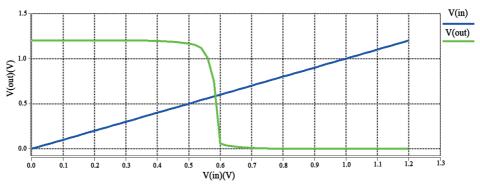

| 6.3  | Transfer characteristic of a CP-SiNWFET 2-input XOR gate                             | 91 |

| 6.4  | 1-bit adder with generation of inverted sum and carry                                | 95 |

| 6.5  | (TMR)-based 1-bit adder architecture                                                 | 96 |

# **List of Tables**

| 2.1 | TIG-SiNWFET structural and physical parameters                                   | 20 |

|-----|----------------------------------------------------------------------------------|----|

| 2.2 | Fabrication induced variations in controllable-polarity SiNWFET                  | 26 |

| 2.3 | The characteristics of DG-SiNWFET and doped-SiNWFET devices in presence of       |    |

|     | process variation on the structural parameters                                   | 27 |

| 3.1 | DG-SiNWFET geometrical parameters                                                | 41 |

| 3.2 | DG-SiNWFET PV analysis using TCAD and proposed methodology                       | 45 |

| 3.3 | Execution time comparison between TCAD-based and proposed learning-based         |    |

|     | I-V curve estimators                                                             | 46 |

| 4.1 | Comparison of mean and variance of various ITC'99 and ISCAS benchmarks on        |    |

|     | the delay variation of longest path before and after applying proposed parameter |    |

|     | reduction                                                                        | 63 |

| 5.1 | TIG-SiNWFET fabrication process steps and related defect model                   | 73 |

| 6.1 | Output voltage values of the 3-input XOR gate in DG-SiNWFET technology           | 93 |

| 6.2 | Output voltage values of the 3-input MAJ gate in DG-SiNWFET technology           | 93 |

| 6.3 | Fault-tolerant 1-bit adder characteristics                                       | 96 |

# 1 Introduction

Integrated Circuit (IC) industry has experienced a tremendous growth during the last few decades. The demand for consumer electronic products has increased the market size of semiconductor industry. Companies require keeping the cost of products low while trying to add more functionality on a single chip. Over the past decades, this aim has been successful. Indeed, the number of transistors per chip has increased exponentially, as well captured by Moore's law. The downscaling trend has enabled semiconductor industries to both put more transistors on a constant chip area and boost the chip performance [1]. The capability of employing more transistors allows us to perform designs that satisfy specific goals like low power, high performance, and high memory capacity. As a result, the development of portable multi-function products such as tablets and smart phones has become feasible.

As the shrinkage passed below 90nm over a decade ago, the scaling trend faced several challenges such as *Short Channel Effect* (SCE) [2], lithography wavelength limitation [3], random dopant fluctuations [4]. SCE caused higher Off-state leakage currents of the devices, and therefore prevented the higher integration of transistors on a single die. Various techniques such as thinning gate oxide, using shallow source/drain junctions, and employing thin-film SOI MOSFET proposed to alleviate this difficulty [2]. The light wavelength used for the projection of device dimensions on a die was also a serious challenge since it is much longer than the actual dimensions of the device. Therefore, the projected device image was distorted, which complicated the control of variability on the critical dimensions. Researchers proposed various techniques to improve the lithography resolution, e.g., *Optical Proximity Correction* (OPC) [5]. OPC enhances the impact of light distortion by shifting edges or adding further polygons to the mask pattern. The challenge was successfully addressed through *Double Patterning Lithography* (DPL) [6]. In DPL the dense lithography patterns are separated into two sets, for which the exposure and the depth of focus is remarkably improved for each set.

As the technology downscaling pushed towards the 22nm node and beyond, the industry moved away from the planar structures which had successfully used very well for several decades [7]. The 14nm lithography is expected to heavily depend on DPL, *Triple Patterning Lithography* (TPL) [8], and even *Quadruple Patterning Lithography* (QPL) [9], as shown

Figure 1.1: The complexity of lithography for 14nm scaling and beyond [7].

in Figure 1.1, due to the fact that the feature size is scaled faster than the wavelength of the lithography light. The cumulative impacts of emerging device structures, performance requirements, manufacturability, and DPL, will impose significant challenges for the implementation of efficient design solutions. Although some variability sources such as *Random Dopant Fluctuation* (RDF) is expected to be improved by exploiting novel devices [10], new sources of variability such as height variation in FinFET arises due to the complex geometry and process of future devices [7]. Additionally, variability that originates from *Line Edge Roughness* (LER) will become more challenging when the dimensions are decreased further. Moreover, heavily exploiting of DPL leads to color-dependent systematic shifts capacitance because of correlated/anti-correlated effects of miss-alignment [7].

As both device technology and lithography compete against scaling restrictions, the future technology generation will continue massive changes in both transistor structure and lithography procedures. In order to sustain the improving performance and efficiency trend according to Moore's law, some new alternative processing device and elements are being extensively researched. These investigations are in progress for advanced and evolutionary devices, which allows further scaling. The ever increasing complexity of structure and process for such devices, along with performance, reliability, and yield requirements will result in many new challenges for future circuit generations.

## 1.1 Evolution of Transistor Technologies

In this section, we briefly review a number of advanced and emerging devices, proposed by VLSI community, which try to address the currents issues to continue scaling of transistors.

#### 1.1.1 CMOS Advanced Devices

#### **FD-SOI Technology**

Fully Depleted Silicon On Insulator (FD-SOI) is a promising technology that addresses the SCE problem beyond 65 nm. FD-SOI transistors utilize an ultra thin channel deposited on a thin layer of insulator so-called Buried Oxide (BOX). This technology provides a better electrostatic control over the device channel and considerably reduces the leakage current when compared to the bulk technology (Figure 1.3). Accordingly, it presents a more efficient body-biasing control owing to no floating body. Thanks to the tiny height of the channel, the channel doping is not required. This can reduce the variation of  $V_{Th}$  as well. After all, the SOI technology traditionally has been faced with the heat conduction from device channel to substrate due to the very low thermal conduction of the buried oxide. The generated heat degrades the carrier mobility leading to  $V_{Th}$  shift.

#### **FinFET Technology**

As depicted in Figure 1.2, FinFETs employ vertical channels by which the leakage surface area between Source and Drain is greatly reduced. Using spacer lithography process enables Self-aligned gate deposition by which Thin-body (Fin width) devices is successfully fabricated [11]. The obtained device therefore has lower Source/Drain parasitic capacitance and better immunity to SCE. FinFET maintaining a steep subthreshold slope and represents good matching due to low doping concentration in the channel [12].

Figure 1.2: 3-D structure of a FinFET Transistor.

The quantization of transistor width in FinFET circuit design is completely different than the continuous values of the planar technology. This property can significantly increase the complexity of the design. Therefore, new CAD tools are required to consider device width for custom circuit optimization. Indeed, this is a critical requirement for memory arrays and analog circuits.

Figure 1.3: Comparison of the of the carrier transportation in the channel: (a) bulk MOSFET, and (b) FD-SOI [14].

#### **Multi-Gate Technology**

Improving carrier mobility can be accomplished either by exploiting materials with higher mobility, i.e., GaAs or by modifying the device geometry to improve the electrostatic control over the device channel. Utilizing more than one gate, i.e., Double-Gate (DG) FETs, provides better channel modulation and reduces the SCE effects. Extra gate(s) can be used for  $V_{Th}$  adjustment and leakage current control; however, these significantly increase fabrication complexity and requires introspection in circuit design and verification (Figure 1.4). However, the complexity can be mitigated by going to FinFET structures.

Figure 1.4: The increase of geometrical complexities for future nano-devices [11].

#### 1.1.2 Emerging Devices

#### Silicon Nanowire FETs

As a promising candidate of replacing current CMOS technology, *Silicon Nanowire FET* (SiN-WFET) has received considerable attention. SiNWFET employs a very thin nanowire as the device channel which fully covered by the gate. This *Gate-All-Around* (GAA) structure provides great electrostatic control and high device On/Off current ratio, using the best feasible control of the gate over the channel (Figure 1.4). Accordingly, it is cost effective and CMOS compatible manufacturing process, promote it as high interest to continue scaling below 10 nm [15]. Because of the tiny dimensions of the channel, variability plays an important role on the performance and the functionality of SiNWFETs. Various sources of variation, i.e, LER, can cause carrier scattering, and therefore change the device characteristics such as On-current ( $I_{On}$ ) and  $V_{Th}$ . Therefore, controlling the variability is an important feature to make this technology achievable.

#### **Carbon Nanotube FETs**

Carbon Nanotube FET (CNTFET) possesses superior characteristics for future integrated circuits, in terms of carrier mobility and heat conductivity. Carbon Nanotubes are rolled up cylinders made of graphene. Depending on their physical configurations, CNTs can show semiconductor properties. Thanks to the cylinder structure and strong covalent bound among carbon atoms, CNTs have quasi-ballistic carrier transport, even for large distances [16]. They have high thermal conductivity, along with no boundary scattering [17]. These properties make them interesting for fabricating very fast switches. However, they suffer from several challenges including lifetime degradation, complication of mass production, and reliability issues [18].

#### **Two-Dimensional Transistors**

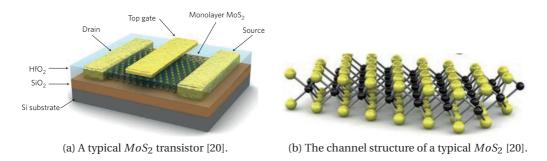

Two-dimensional materials are attractive to be exploited for future nano-devices because fabrication of complex structures is simple [19]. Recently, graphene has been intensively researched owing to its superior mobility. However, graphene does not have a bandgap which is necessary for building semiconductor devices. Engineering a bandgap for graphene considerably reduces its mobility and imposes fabrication complexity. It has been shown that for other single-layer materials like  $MoS_2$ , the fabricated device has either an acceptable bandgap while it has superior mobility [20]. Similar to previous mentioned devices, graphene based FETs suffer from the same fundamental problems, i.e., gate and source-to-drain tunneling, variability, parasitic resistances/capacitances [19]. Figure 1.5 depicts the structure of a typical  $MoS_2$  transistor and its channel structure.

Along with the several promising opportunities of emerging nanoscaled technologies for future ICs, a number of problems such as process variation, manufacturing defects, and reliability

Figure 1.5: Three-dimensional structure of a typical *MoS*<sub>2</sub> transistor and the channel structure.

remains as a serious challenge. In the following section, we briefly review the major technical challenges of the emerging technologies from device fabrication level to system level.

### 1.2 Challenges of Emerging Technologies

Moving towards emerging nonascaled devices for mass production of ICs, manufacturers and designers are confronted with many challenges for design, verification, and test. Manufacturing uncertainties and process variation along with fabrication irregularities and defects adversely affect the circuit's yield and dependability for deeply scaled technologies. To reach high yield products, the issues of manufacturing process have to be considered from the early steps of the design. These issues originate either form physical flaws, i.e., *Gate Oxide Short* (GOS) or variability of the critical parameters, i.e., gate length. With the increasing fabrication uncertainty for future ICs, the use of efficient statistical variability analysis for precise yield estimation is inevitable. Moreover, developing precise defect models through the analysis of manufacturing process is necessary for enhancing product test. In the following, we briefly review the various sources of manufacturing imperfections and variations, which are relevant to our variation and defect analysis.

#### 1.2.1 Process Variation

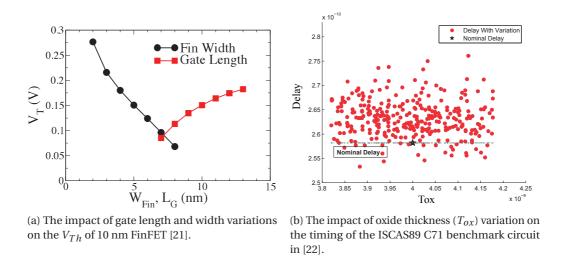

*Process Variation* (PV) is referred to unwanted deviations from the nominal or expected values of physical and structural parameters for fabricated transistors, i.e., gate length,  $V_{Th}$ , gate oxide thickness, and number of dopant atoms. PV therefore changes the performance or even the functionality of the fabricated devices. Figure 1.6a depicts the impact of gate length/width variations on the  $V_{Th}$  of FinFET in 10 nm technology. The  $V_{Th}$  sensitivity on length and width shows a diverse trend. Such device variations then impact circuits' performance or functionality and lead to yield loss, as shown in Figure 1.6a.

Figure 1.6: The impact of parameter variation on the performance of a device and circuit.

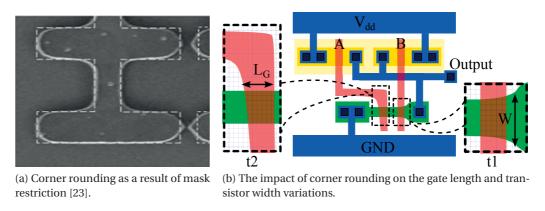

Figure 1.7: Mask patterning restriction as a source of variation.

#### **Variation Sources**

Various sources of variation contribute to change the characteristics of the fabricated devices. These sources either significantly impact the critical dimension of a transistor including Gate Length  $(L_G)$ , and Gate Oxide Thickness  $(T_{Ox})$  or affect the device physical properties like the number of dopants in Source/Drain.

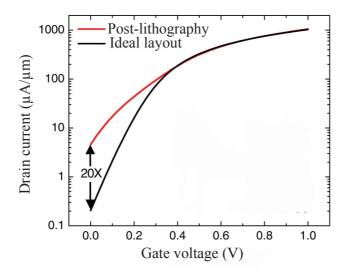

The main source of critical dimension variation consists of mask positioning and alinement, photoresist effect, and chemical/mechanical polishing. Mask pattern restriction is a result of low pass filter behavior of lithography lens, and can make a major difference between the real layout and the printed image on die. This anomaly can be seen as corner rounding and line end shortening (Figure 1.7). Both of these effects, can seriously impact the behavior of the transistor. As illustrated by Figure 1.7b, the corner rounding can change the effective width of the transistor (t1) leading to remarkable increase of transistor transistor leakage

Figure 1.8: Mask patterning restriction causes rounding effect on the transistor gate and vastly increases the leakage current in 65 nm technology [23].

(Figure 1.8) [23]. Beside, the effective  $L_G$  is increased by the corner rounding for transistor (t2). As another source of variation, chemical resist effect can adversely affect edge roughness of the patterns. Chemical photoresist processing is a series of chemical reactions on the wafer surface and it causes random variation on the edge of patterns so-called *Line Edge Roughness* (LER). LER does not scale with the technology and becomes a serious barrier for further scaling beyond 45 nm. Along with the mentioned variability sources, chemical and mechanical polishing, which is used to remove excess parts of the device such as extra parts of polysilicon and oxide, can change the effective width and length of the device.

On the other hand, there exist other sources of variation, such as *Random Dopant Fluctuations* (RDF), which impact the physical properties of the transistors. RDF is generated by the variability on the number and location of dopant atoms in the device channel. This phenomenon becomes crucial for deeply nanoscaled devices since the charge discreteness prevent reaching a uniform doping concentration.

#### **Types of Variations**

Fabrication of the ICs involves usually many steps, in which several sources of variation affect the final product. The variation may be caused by photolithography equipment fluctuation, environmental variations, and material properties. Discovering all the actual variation sources of each IC is almost impossible. In order to be able to analyze the performance and functionality of circuits, designers classify the various types of process variations to make the analysis tractable.

Variations can be generally divided into two categories of *inter-die* and *intra-die* variations.

Inter-die variations refer to common variations within the die and include different levels, i.e., die to die, wafer to wafer, and lot to lot [24]. These variations can be taken into account by assigning a random variable to each die, by which a deviation from nominal value for a device parameter is represented. Fluctuations such as variation of critical dimensions, owing to mask misalignment or unequal exposure time, are considered in this category. Here, the number of necessary variables for inter-die variation modeling of a die is limited by the number of variation parameters of a device. Intra-die variations, on the other way, refer to random and spatial correlated variations within a die. These variations are becoming very challenging at advanced technology node since the overall impact of fluctuations can result in substantial yield loss. In contrast to inter-die variations, the number of required variables for intra-die variation modeling can be equal to the total number of variation parameters in a die. Consequently, high dimensional parameter space of large circuit makes the intra-die variation modeling very challenging.

#### **Variation Modeling**

Measuring performance uncertainties, especially for *inter-die* variations, has been traditionally performed by corner-based analysis. Corner models explore additional extra device models such as *fast* and *slow* and estimate the boundary of performance deviation. The utilization of this model for variability analysis of nanoscale technologies has become very limited. This model simply assumes that the all components of a circuit are correlated and they reach to worst-case at the same time. This can lead to pessimistic performance estimation. Moreover, this model does not take to account the *intra-die* variations, for which it may result in erroneous performance estimation. Although a number of modifications have been proposed to incorporate *intra-die* variations into corner model, a huge number of corners are necessary for precise performance analysis that makes it impractical for large circuits.

In contrast to the corner model, statistical methods are able to deal with *intra-die* variations, on-chip spatial correlations and *inter-die* variations, and therefore they are widely used for circuit performance analysis. *Monte Carlo* (MC) simulation is among the most important methods for statistical circuit analysis. MC numerically computes the distribution of the desired performance parameter through repeated sampling. In each iteration, numerical samples of the process parameters are randomly selected and injected to a device-level or circuit-level simulator. The obtained values are then aggregated to form the probability distribution of the desired performance parameter. One of the good points about MC simulation is that the accuracy of the obtained result is independent of the problem dimension. As a result, we do not need to increase the number of the input samples as the problem dimension increases. The major drawback of this method is that reaching an acceptable precision requires a huge number of sampling point. As the simulation time is a serious bottleneck in performance analysis, the practical application of MC is limited to devices and small-size circuits.

To overcome such computational costs, two other classes of statistical performance analysis are commonly utilized in VLSI community. First, *response surface* performance modeling

#### **Chapter 1. Introduction**

which tries to reduce the problem complexity by estimating the desired performance using a kernel (i.e., polynomial) regressor. Second, multivariate dimension reduction methods that reduce the problem dimensions either by removing correlation among process parameters or finding the most dominant process parameters. Although these methods can obtain the statistical dependencies between device parameter variations and circuit performance, they require an extensive revision to be applicable for future emerging nanotechnologies.

#### Variation Modeling Requirements for Emerging Technologies

To perform an efficient PV analysis for emerging nanotechnologies, the following requirements for statistical methods are necessary to be considered.

- Simulation complexity: Precise circuit simulation in current CMOS technology is performed through compact models. Due to the tiny dimension and complex geometry of the future nano-devices, statistical compact models are inevitable for PV analysis. The development and verification of these models requires both experimental data of the fabricated devices and enormous amount of TCAD simulations. TCAD uses physical equations of the target device, and find its characteristics through numerical solution of the equations. This substantially increases the complexity of model computations so that the TCAD simulation may take a couple of days or even months for a single device. Therefore, methodologies that reduce the computational complexity of variation analysis for emerging future devices are becoming very important.

- Nonlinearity between process and performance parameters: The process and performance parameters have strong nonlinear dependencies. These dependencies and correlations among these parameters are key factors to simplify variability models. The correlations are generally divided into two types: *intra-set* correlations which refer to the correlations among process parameters, and *inter-set* correlations which refer to the correlations between process and performance parameters. Reducing complexity is obtained by removing these correlations. Consequently, the nonlinear dependencies of parameters should be taken to account for optimally reducing the complexities of variability models.

- Statistical distributions: Most statistical variation analyses have strong assumptions on the probability distribution of the process parameters. They assume that the distributions of the all parameters are Gaussian or Non-Gaussian to avoid more computational complexities. Although these assumptions were acceptable for bulk CMOS, they are not valid for emerging nano-devices. This can negatively impact the accuracy of such analyses. Thus, statistical methods that can address a combination of different probability distributions are highly required.

#### 1.2.2 Manufacturing Defects

Faulty fabrication can cause manufacturing defects, and finally lead to circuit failure. These defects result in faulty circuits, where the behavior may differ from the correct one. As a result, circuit testing is necessary to ensure that the functionalities of fabricated circuits are correct. In order to develop high-coverage test, faults should be modeled based on their behavior. The importance of fault modeling is highlighted by the fact that a defect may lead to a different behavior in various technologies. For instance, an open defect in a bulk CMOS transistor results in switching failure, while the same defect on the back gate of a Double-Gate transistor only leads to delay and leakage variation. As emerging nano-devices have different geometrical structures and dissimilar physics of operation rather than bulk CMOS technologies, they need a precise defect and fault modeling for test.

The faults can be classified in two groups. The first group is parametric faults that originate from process parameter variations which reviewed in the previous section. The second group is defective faults that arise from unwanted connections or isolations in different parts of a transistor due to the lack of control during manufacturing. The type of defective faults, in a specific technology, depends on the different steps of fabrication along with the materials used in each step. Both groups are becoming very challenging in deeply-nanoscaled technologies, since the control on the physical and structural parameters of devices is reduced by dimensional downscaling. Using cross section analysis to extract the characteristics of the defects for fabricated circuits is very expensive, and sometimes is almost impossible. Therefore, inductive fault analysis should be used for defect and fault modeling of the nano-devices.

#### The Need for Defect and Fault Modeling in Nano Era

Defect tolerant design for future technologies is faced by several challenges. Changing the process flow and the materials can change the population and distribution of the defects. Moreover, the different design of logic cells and functional components may change the sensitivity of the design for a specific group of faults. Consequently, making progress in reliable circuit design and test necessitates both to develop efficient fault models for emerging technologies and to revise the current test method according to the related fault model models and circuits sensitivities.

• Process and layout dependent defects: The impact of a manufacturing defect can be influenced by the materials, structure of logic gates or circuits layout. The structure of logic gates in various technologies such as FinFET, and *Controllable-Polarity Silicon Nanowire FETs* (CP-SiNWFETs) are significantly different. This information is essential for extracting the effects of physical failures on circuit functionality. Moreover, the specific faults for each technology can be ranked according to its importance or probability of occurrence. We require this information for both increase the yield and keep the overheads of fault-tolerant design as low as possible.

Figure 1.9: The exponential increase of the number of transistor per IO pin for microprocessors and ASICs as a challenge of test for future technologies [25].

• Test complexity: For many years, the aim of IC testing was to verify its functionality by the minimum number of input test vectors to guarantee full fault coverage. Moving towards nano era, test development needs to address several serious challenges. Accessing to transistors on a chip becomes more complicated owing to the exponential growth of the devices rather than the IO pins (Figure 1.9). Second, circuit sensitivity variation in each technology can make a defect into a very aggressive one while it was negligible in the past technologies. Moreover, the new manufacturing PVs that influence the functionalities in each technology should be covered by test algorithms. Consequently, all aspects of the test methodologies, including defect and fault modeling, input test generation, and coverage evaluation should handle these problems.

## 1.3 Dealing with Process Variation and Fabrication Defects

The inadequacies in the traditional methodologies to deal with the manufacturing threats in nanometer technologies, have led to advanced DFM techniques. As stated in [26], design flows for nano-devices require tighter integration between design and manufacturing. Unlike earlier technologies, design and manufacturing cannot remain independent of each other.

In order to address the aforementioned issues, statistical design approach has been investigated as an effective method to ensure certain yield criteria [27]. In this approach, the design space is explored to optimize performance parameters (such as power, reliability) to meet timing and power requirements. However, most of these investigations cannot handle both objectives simultaneously. Unfortunately, most of these method cannot be utilized for emerging technologies owing to the lack of fast simulation models like compact models for emerging nano devices.

To increase the yield and fault tolerance, some methods also point towards adding extra components on the chip, irrespective of fault detection, as a design based tolerance. This is a pessimistic technique adding unnecessary area on chip. Despite the high redundancy overhead, the nanocomputing community has proposed the use of Triple- and N-modular redundancy techniques and shown that they provide high reliability even in the presence of high device failure [28]. Such techniques increase the reliability of designs, but the main assumption made in these redundancy techniques is that the voter block is free from the same failures that the rest of the design is facing. While such assumption seems true for designs based on traditional silicon technologies, this assumption will not hold for designs based on nanotechnology hindering the applicability of Triple- and N-modular redundancy techniques for nano era designs.

Figure 1.10 summarizes the main difficulties and hindrances have been highlighted in the reports of *International Technology Roadmap for Semiconductors* (ITRS). Addressing these challenges plays a key role on the performance and the yield of future circuits. A number of these challenges are addressed in this thesis.

## System Implementation • Improving the reliability of hardware and software • Characterizing new computational model for reliable and power efficient computations • Developing new methods for performance and power management Design and verification of circuits & functional blocks • Implementing reliable functional blocks with unreliable devices • Developing CAD tools for circuit design using emerging nonplanar devices • Statistical variability analysis for yield and performance improvement • Power and performance optimized functional cores for heterogeneous ICs Device manufacturing • Design and fabrication of reliable devices with adequate control on variability of critical parameters, i.e., threshold voltage • Developing novel devices with enhanced functionality for more efficient information processing • Characterizing of new manufacturing defects and failure mechanisms corresponding to nonplanar devices Process complexity and fabrication compatibility towards heterogeneous integration • Developing new CAD tools for simulation and statistical analysis of emerging nanoscaled devices Improving test and verification methods

Figure 1.10: Challenges of emerging technologies for future integrated circuits.

#### 1.4 Thesis Contribution

The contribution of this thesis consists of five major parts:

- Robustness analysis for controllable-polarity silicon nanowires: this part of research includes the detection of important source of variations, and impact of process parameters variation on the performance of the device and logic gates. Here, we investigate the variation of critical parameters of the nanowires, such as gate length, on the characteristics of the device such as *On*-current, channel leakage current, threshold voltage and subthreshold slope.

- Learning-based methodology to reduce the computational complexity for device level PV analysis: Generating data set for variability analysis of novel devices is a difficult task due to the lack of fast and precise compact model. To address this problem, we combine TCAD simulations with a learning algorithm and propose a methodology to speed up the data set generation for variability analysis.

- A statistical method for fast PV analysis of emerging technologies: The increasing number of parameters for variability modeling of integrated circuits imposes a remarkable computational complexity. We propose a parameter selection technique than can effectively select the most important parameters of the target circuit for variability analysis. Therefore, a considerable speed up is obtained.

- Inductive fault analysis: We perform inductive fault analysis on controllable-polarity silicon nanowires to find an appropriate defect model that helps to test development for this technology. We extract the possible defects from device manufacturing process steps and analysis the impact of all extracted defects for the performance and functionality of the device. Based on the results, we propose a guide line for test of the logic circuits in this technology.

- Fault tolerant arithmetic circuit design: we exploit the obtained defective fault model for designing fault tolerant arithmetic circuits. We investigate the behavior of adder components in presence of fault and then we propose a fault tolerant novel structure for carry-ripple adder.

## 1.5 Thesis Organization

The reminder of this thesis is organized as follows. In Chapter 2, an overview of the CP-SiNWFETs as an emerging technology is presented. The promising characteristics of this technology for device and logic circuit development are then outlined. The fabrication process, simulation methodology, and the structure of logic gates are also reviewed. Finally the major sources of variation in this technology are investigated and the results of variation on device and logic cells are then represented.

In Chapter 3, a learning based methodology that can substantially reduce the time complexity and cost of variation analysis for emerging technologies is introduced. The components of the proposed methodology such as a prediction module are then represented. Finally, experimental results are presented that show the proposed methodology effectively accelerates TCAD-based PV simulations close to compact-model-based simulations.

Chapter 4 introduces a feature selection method to reduce the circuit modeling complexity. Next, the mathematical description of this method is explained in detail. The characteristics of this feature selection for VLSI modeling and simulation is then discussed. Finally, the application of this method is demonstrated in digital circuit timing analysis in both FinFET and CP-SiNWFET technologies.

In Chapter 5, the possible manufacturing defects of CP-SiNWFET technology is explored through analyzing the fabrication steps and the layout structure of logic gates. Afterwards, the impacts of obtained defects are investigated on the performance and the functionality of CP-SiNWFET logic gates. Out of the results, the current fault model is extended to a new a hybrid model can be efficiently used to test the logic circuits in this technology. The inefficiency of current CMOS test methods for covering all faults in CP-SiNWFET technology is then shown. Finally, an appropriate test method to capture such faults is proposed as well.

Chapter 6 is dedicated to the intrinsic capability of fault tolerate in CP-SiNWFET technology. Based on this result, a fault tolerant and scalable adder is introduced. Next, the robustness of the proposed circuit is investigated, and finally, the efficiency of proposed circuit is verified with experimental results.

Chapter 7 summarizes the contribution of this thesis and concludes it. In addition, a number of ideas for future work are provided.

Overall, variability and fabrication defects are the two major challenges of the deeply scaled integrated circuits. In this thesis, we investigate these two topics for CP-SiNWFETs as an emerging technology for future logic circuits. The robustness of this technology is carefully analyzed in presence of these difficulties. Then, several techniques to handle these problems are proposed. The outcome of this thesis will help to achieve more dependable circuits in nano era.

#### 2.1 Introduction

Silicon NanoWires (SiNWs) have attracted growing interest as a promising candidate for future ICs owing to their unique physical and electrical properties. SiNWs with *Gate-All-Around* (GAA) structures [29] provide an even better electrostatic control over the channel (and reduce leakage current) as compared to current technologies such as FinFET [30] and FDSOI [31]. Since short-channel effect and leakage power are the most significant challenges of further feature-size scaling, SiNWs are very a promising technology to pursue the scaling trend towards higher performance and functionality. In this chapter, we introduce the SiNWs with *Controllable-Polarity* (CP) characteristics. We review the device characteristics, and then we introduce our framework for device and circuit simulation in this technology. Next, we look at fabrication process of these devices and then we investigate the structure of logic gates in this technology. This is required for variability analysis, defect modeling and fault-tolerant circuit design. Finally, we analysis the robustness of this technology in presence of manufacturing variability.

Beyond 45 nm, many devices exhibit ambipolar characteristic at source and drain contacts such as SiNWs [32], carbon nanotubes [33], and graphene [34]. These devices have ambipolar behavior, i.e., they support the flow of both n-type and p-type carriers. While ambipolarity is usually suppressed by fabrication process to provide unipolar devices [35], it can be used to enhance the logic functionality, i.e., the capability of implementing more complex functions using smaller number of transistors [36].

Ambipolar conduction of the nanoscaled devices can be controlled by adjusting the device polarity online. Such transistors with Controllable-Polarity have been successfully implemented in *Silicon NanoWires* (SiNWs) [37, 38], Carbon Nanotube [39], graphene [40], and FinFET [41]. These devices have been successfully used for the fabrication of controllable-polarity logic gates that provide compact hardware realization with remarkable circuit design flexibility. In

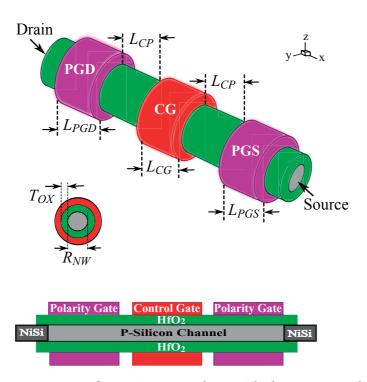

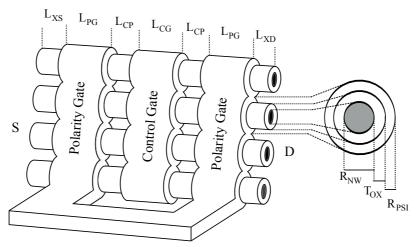

such transistors, one electrode gate, the *Control Gate* (CG), works like conventional MOSFETs, and provides the conduction by controlling potential barriers. At least one another electrode gate, the *Polarity Gate* (PG), is needed to control the n-type or p-type characteristics of the device. Indeed, the type of carriers that flow in the device channel is adjustable through the applied voltage on PG. Among various materials used for CP transistors, SiNWs have a

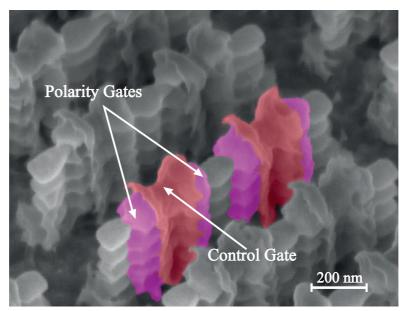

CMOS-compatible fabrication process. Different architectures have been proposed for their implementations [37, 38, 42, 43]. As an example, Figure 2.1 represents a *Three-Independent-Gate* (TIG) SiNWFET with a CG and two PGs (PGs and PGD). Here, the side regions (PGs and PGD) determine the majority carriers through adjusting the Schottky barrier height at the source/drain junctions. Thus, the device can exhibit controllable n-type and p-type characteristics. DG-SiNWFETs [37] exploit a similar structure than TIG-SiNWFETs where the two polarity gates are connected together. Reconfigurable SiNW [42] is another example in which only one polarity gate is utilized for configuration of transistor to desired polarity.

Figure 2.1: The 3D structure of TIG-SiNWFET along with the corresponding geometrical parameters.

(a) The SEM figure of the fabricated DG-SiNWFET [37]. The red and purple colors highlight the control and polarity gates respectively.

(b) The 3D model of a DG-SiNWFET along with the geometrical parameters. Here, the both polarity gate are connected to each other.

Figure 2.2: Vertically stacked DG-SiNWFET as a CP-SiNW.

#### 2.2 Fabrication Process

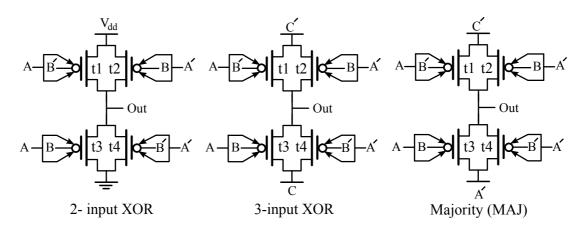

The TIG-SiNWFET devices are fabricated in a top-down approach. Table 2.1 summarizes the fabrications process of the device along with the outcome of each step. The Bosch etching process [44] is utilized to form the nanowire stack. An high- $\kappa$  gate dielectric is then deposited over each patterned nanowire and provides a thin oxide layer ( $\leq 5nm$ ) around the channel.

Oxidation process is followed by a conformal metal deposition to shape the polarity gates around the nanowires. Finally, the control gate structure is self-aligned to polarity gates. Thus, a three-gate device is obtained in which polarity gates are electrically isolated by the controlled deposition of the gate oxide.

#### 2.3 Electrical Simulation

In order to first model the possible defects of this technology, and then to investigate their impact on the performance and the functionality of logic gates, we need to setup a simulation framework that brings together device and circuit simulators. Consequently, a two-step simulation environment, that integrates the Sentaurus TCAD and HSPICE simulators into a single framework, is used to facilitate high-level simulations. First, we build a TCAD model of the TIG-SiNWFET, for which the I-V curves are calibrated with those of our fabricated devices. The typical parameters of the TIG-SiNWFET, shown in the Figure 2.1, are listed in Table 2.1.

Table 2.1: TIG-SiNWFET structural and physical parameters.

| Device Parameter                                   | Value             |

|----------------------------------------------------|-------------------|

| $Length of Control Gate(L_{CG})$                   | 22 <i>nm</i>      |

| $Length  of  Polarity  Gates  (L_{PGS},  L_{PGD})$ | 22 <i>nm</i>      |

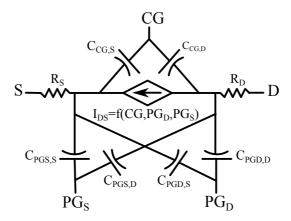

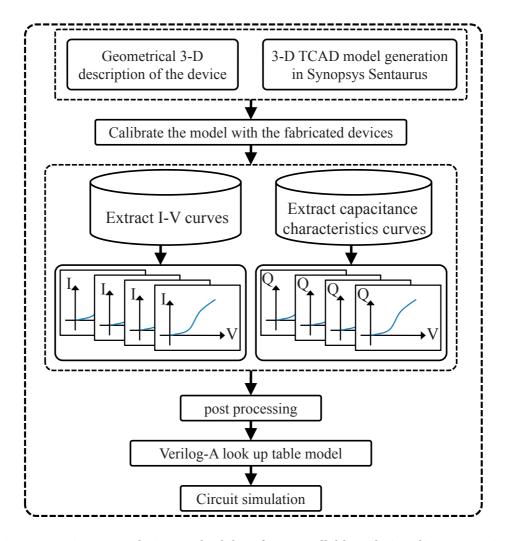

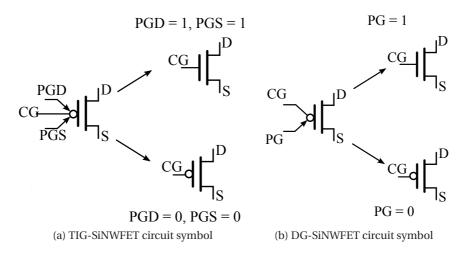

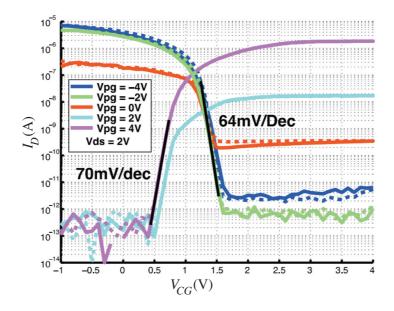

| $Length  of  Spacer  (L_{CP})$                     | 18 <i>nm</i>      |