# ANALYSIS AND SYNTHESIS OF CONCURRENT DIGITAL SYSTEMS USING CONTROL-FLOW EXPRESSIONS

#### A DISSERTATION

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

DOCTOR OF PHILOSOPHY

FOR THE DEGREE OF

Claudionor José Nunes Coelho Junior February, 1996 © Copyright 1996

by

Claudionor José Nunes Coelho Junior

I certify that I have read this thesis and that in my opinion it is fully adequate, in scope and in quality, as a dissertation for the degree of Doctor of Philosophy.

Giovanni De Micheli(Principal Adviser)

I certify that I have read this thesis and that in my opinion it is fully adequate, in scope and in quality, as a dissertation for the degree of Doctor of Philosophy.

David Dill(Associate Adviser)

I certify that I have read this thesis and that in my opinion it is fully adequate, in scope and in quality, as a dissertation for the degree of Doctor of Philosophy.

Bruce Wooley

Approved for the University Committee on Graduate Studies:

#### Abstract

We present in this thesis a modeling style and control synthesis technique for systemlevel specifications that are better described as a set of concurrent descriptions, their synchronizations and complex constraints. For these types of specifications, conventional synthesis tools will not be able to enforce design constraints because these tools are targeted to sequential components with simple design constraints.

In order to generate controllers satisfying the constraints of system-level specifications, we propose a synthesis tool called *Thalia* that considers the degrees of freedom introduced by the concurrent models and by the system's environment.

The synthesis procedure will be subdivided into the following steps: We first model the specification in an algebraic formalism called *control-flow expressions*, that considers most of the language constructs used to model systems reacting to their environment, i.e. sequential, alternative, concurrent, iterative, and exception handling behaviors. Such constructs are found in languages such as C, Verilog HDL, VHDL, Esterel and StateCharts.

Then, we convert this model and a suitable representation for the environment into a finite-state machine, where the system is analyzed, and design constraints such as timing, resource and synchronization are incorporated.

In order to generate the control-units for the design, we present two scheduling procedures. The first procedure, called static scheduling, attempts to find fixed schedules for operations satisfying system-level constraints. The second procedure, called

dynamic scheduling, attempts to synchronize concurrent parts of a circuit description by dynamically selecting schedules according to a global view of the system.

# Dedication

To Carla and Jean-Luc,

#### Acknowledgments

I have many people to thank for this dissertation. First, in order to fulfill one of Prof. Giovanni De Micheli's last requests as an advisor, I shall be brief. So, instead of saying all good things one usually says about advisors, I will just say that I consider myself very fortunate to have him as my advisor and as a friend.

I would like to thank Prof. David Dill for all the help and support as a co-advisor. I am also very thankful to him for allowing me to participate in the verification group meetings and discussions, where I learned a lot. Prof. Bruce Wooley has been generous with his time by reading this dissertation. I would like to thank also Prof. Teresa Meng and Prof. Gordon Kino for serving on my oral defense committee.

I have many thanks to the members of the CAD and verification groups at Stanford. Many good ideas and discussions followed the interaction with them, especially with Luca Benini, Dave Filo, Rajesh Gupta, David Ku, Vincent Mooney, Polly Siegel, Han Yang and Jerry Yang. I would like to thank Toshiyuki Sakamoto, who has been working on the implementation of the *Parnassus* system. I have no words to thank Lilian Betters for making my life at Stanford so much easier by dealing with the university bureaucracy. Charlie Orgish and Thoi Nguyen have been very helpful in keeping the machines working. I have also to thank the people with whom I shared my office in the trailers and at CIS (Dave Ofelt, Jeff Kuskin, John Heinlein, and Wingra Fang) for making a friendly office environment.

Many friends I made at Stanford came from outside the research environment.

Thanks to all of them, specially to the lunch group, Alexandre Santoro and João Comba, for making my lunch hours much more relaxing and enjoyable. Thanks also to the several friends I have met here and who helped me throughout these years: Antônio Todesco, Luis Portela, Ciro Noronha, Tyiomari, Angela Comba, Felipe Guardiano, Alvaro Hernandez, Beto Cimini, Leda Beck, Ingrid and Luiz Franca. Thanks also to Gilberto Mayor, Diógenes Silva, Berthier Ribeiro and Rodolfo Resende for the friendship prior to my Stanford days.

I would like to thank my parents for believing in me and for all the support, guidance and encouragement. Thanks also to the support given by Maria, Florinda and by my in-laws Marcio, Domingos, Sirene and Carlos Vinicio.

Finally, I reserve a special gratitude to my beloved wife, Carla Nacif Coelho, for her support, love, patience and encouragement during our stay at Stanford, and for all the good moments we had here. Thanks to Jean-Luc, for bringing me the joy of being a parent. To them I dedicate this thesis.

This research was sponsored by the scholarship 200212/90.7 provided CNPq/Brazil, by a fellowship from Fujitsu Laboratories of America, and by ARPA, under grant No. DABT 63-95-C-0049.

## Contents

| A            | bstra | nct                                                  | iv  |

|--------------|-------|------------------------------------------------------|-----|

| D            | edica | ation                                                | v   |

| $\mathbf{A}$ | ckno  | m wledgments                                         | vii |

| 1            | Inti  | roduction                                            | 1   |

|              | 1.1   | Overview of System-Level Synthesis                   | ę   |

|              | 1.2   | Synthesis Tools used for System-Level Designs        | Ę   |

|              | 1.3   | Issues in System-Level Synthesis                     | 8   |

|              |       | 1.3.1 Synchronization Synthesis                      | ć   |

|              |       | 1.3.2 Scheduling under Complex Interface Constraints | 14  |

|              | 1.4   | Objectives and Contributions                         | 16  |

|              | 1.5   | Thesis Outline                                       | 18  |

| 2            | Mo    | deling of Concurrent Synchronous Systems             | 20  |

|              | 2.1   | Abstraction Model                                    | 21  |

|              | 2.2   | Algebra of Control-Flow Expressions                  | 25  |

|              | 2.3   | Axioms of Control-Flow Expressions                   | 31  |

|              | 2.4   | Extended Control-Flow Expressions                    | 34  |

|              |       | 2.4.1 Exception Handling                             | 36  |

|   |                            | 2.4.2    | Basic Blocks                                                | 42  |  |  |

|---|----------------------------|----------|-------------------------------------------------------------|-----|--|--|

|   |                            | 2.4.3    | Register Variables                                          | 43  |  |  |

|   |                            | 2.4.4    | Definition of Extended Control-Flow Expressions             | 48  |  |  |

|   | 2.5                        | Comp     | arison of CFEs with Existing Formalisms                     | 50  |  |  |

|   | 2.6                        | Summ     | nary                                                        | 56  |  |  |

| 3 | Modeling the Environment 5 |          |                                                             |     |  |  |

|   | 3.1                        | Quant    | diffication of the Design Space                             | 59  |  |  |

|   | 3.2                        | Const    | raint Specification                                         | 63  |  |  |

|   |                            | 3.2.1    | Dynamically Satisfiable Constraints                         | 66  |  |  |

|   |                            | 3.2.2    | Statically Satisfiable Constraints                          | 71  |  |  |

|   | 3.3                        | Summ     | nary                                                        | 76  |  |  |

| 4 | Ana                        | alysis d | of Concurrent Systems                                       | 78  |  |  |

|   | 4.0                        | Notat    | ion                                                         | 79  |  |  |

|   | 4.1                        | Contr    | ol-Flow Finite State Machines                               | 79  |  |  |

|   |                            | 4.1.1    | Derivatives of Control-Flow Expressions                     | 81  |  |  |

|   |                            | 4.1.2    | Derivatives in Extended Control-Flow Expressions            | 84  |  |  |

|   |                            | 4.1.3    | Control-Flow Expression Suffixes                            | 91  |  |  |

|   |                            | 4.1.4    | Revisiting Exception Handling                               | 94  |  |  |

|   | 4.2                        | Const    | ructing the Finite State Representation                     | 95  |  |  |

|   |                            | 4.2.1    | Satisfiability of Design Constraints                        | 99  |  |  |

|   | 4.3                        | Repre    | sentation of CFFSM as a Transition Relation                 | 100 |  |  |

|   |                            | 4.3.1    | Characteristic Functions and Transition Relation            | 100 |  |  |

|   |                            | 4.3.2    | Representation of the CFFSM Using the Transition Relation . | 101 |  |  |

|   |                            | 4.3.3    | Computing Reachable States and Valid Transitions            | 107 |  |  |

|   | 4.4                        | Summ     | nary                                                        | 109 |  |  |

| 5            | $\mathbf{Syn}$              | thesis of Control-Units                            | 110 |

|--------------|-----------------------------|----------------------------------------------------|-----|

|              | 5.1                         | Obtaining Control-Units from the CFFSM             | 111 |

|              | 5.2                         | Scheduling Operations in Basic Blocks              | 114 |

|              | 5.3                         | Static Scheduling Operations in CFFSMs             | 118 |

|              |                             | 5.3.1 Extracting Constraints from the CFFSM        | 119 |

|              |                             | 5.3.2 Exact Scheduling for Basic Blocks            | 132 |

|              | 5.4                         | Dynamic Scheduling Operations in CFFSMs            | 139 |

|              |                             | 5.4.1 Selecting the Cost Function                  | 143 |

|              |                             | 5.4.2 Derivation of Control-Unit                   | 146 |

|              | 5.5                         | Comparison with Other Scheduling Methods           | 149 |

|              | 5.6                         | Summary                                            | 151 |

| 6            | Exp                         | perimental Results                                 | 153 |

|              | 6.1                         | The Effects of Encoding on the Synthesis Procedure | 155 |

|              | 6.2                         | Protocol Conversion                                | 156 |

|              | 6.3                         | Control-Unit for Xmit_frame                        | 161 |

|              | 6.4                         | FIFO Controller                                    | 164 |

| 7            | Conclusions and Future Work |                                                    |     |

|              | 7.1                         | Summary                                            | 168 |

|              | 7.2                         | Future Work                                        | 170 |

| Bi           | bliog                       | graphy                                             | 172 |

| $\mathbf{A}$ | Alg                         | ebra of Synchronous Processes                      | 182 |

| В            | Bin                         | ary Decision Diagrams                              | 185 |

## List of Tables

| 1 | Link between Verilog HDL constructs and control-flow expressions       | 30  |

|---|------------------------------------------------------------------------|-----|

| 2 | Axioms of control-flow expressions                                     | 33  |

| 3 | One-hot encoding for decision variables                                | 155 |

| 4 | Binary encoding for decision variables                                 | 156 |

| 5 | Gray encoding for decision variables                                   | 157 |

| 6 | PCI/SDRAM protocol conversion example                                  | 160 |

| 7 | Results for the synthesis of xmit_frame                                | 164 |

| 8 | Results for the synthesis of xmit_frame with dynamic variable ordering |     |

|   | of BDDs                                                                | 164 |

| 9 | Axioms for ASP                                                         | 184 |

# List of Figures

| 1  | System-level tasks                                                | 6  |

|----|-------------------------------------------------------------------|----|

| 2  | Ethernet controller block diagram                                 | 9  |

| 3  | Abstracted behaviors for DMArcvd, DMAxmit and enqueue             | 12 |

| 4  | System architecture                                               | 14 |

| 5  | Writing cycles for synchronous DRAM (a) and for synchronous FIFO  |    |

|    | (b)                                                               | 15 |

| 6  | Thesis outline                                                    | 18 |

| 7  | Partitioning of specification into control-flow/dataflow          | 24 |

| 8  | Greatest-common divisor example                                   | 35 |

| 9  | Hierarchical View of a CFE                                        | 38 |

| 10 | Conversion between $C$ constructs and $ECFE$ disable constructs   | 40 |

| 11 | Exception handling in Verilog HDL                                 | 41 |

| 12 | Dataflow for Differential Equation Fragment                       | 43 |

| 13 | Program-State Machine Specification                               | 44 |

| 14 | (a) Specification and (b) Reduced dependency graph                | 45 |

| 15 | (a) Dataflow graphs for program-state machine and (b) reduced de- |    |

|    | pendency graph                                                    | 48 |

| 16 | Static and dynamic decision variables                             | 59 |

| 17 | Minimum (a) and maximum (b) execution times for the operations of |    |

|    | the differential equation CDFG                                    | 61 |

| 18 | Process P and its Environment                                                  | 65  |

|----|--------------------------------------------------------------------------------|-----|

| 19 | Path-activated constraint                                                      | 73  |

| 20 | Exception handling in Verilog HDL                                              | 75  |

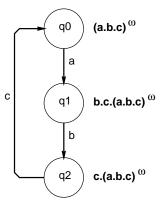

| 21 | Mealy machine for control-flow expression $(a \cdot b \cdot c)^{\omega}$       | 80  |

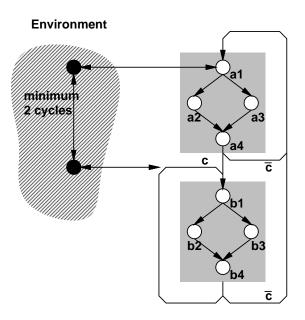

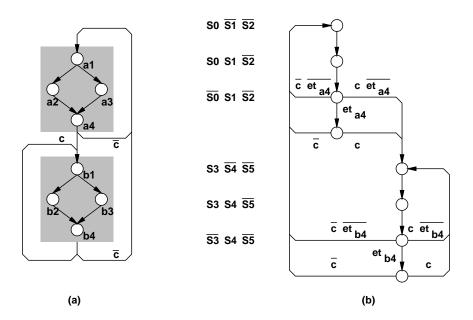

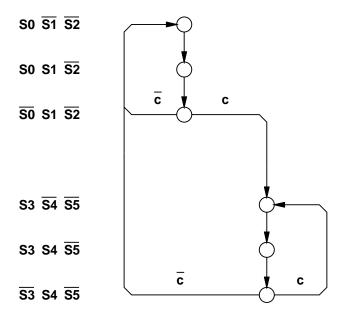

| 22 | Finite-state representation for synchronization synthesis problem              | 96  |

| 23 | Algorithm to construct finite-state representation                             | 98  |

| 24 | Finite-state representation observing synchronization constraints              | 99  |

| 25 | Encoding for Basic Block of Differential Equation                              | 102 |

| 26 | Encoding for Sequential/Parallel Blocks                                        | 103 |

| 27 | Exception Handling in CFFSMs                                                   | 106 |

| 28 | Algorithm to Compute Transition Relation of a CFE                              | 107 |

| 29 | Algorithm to Compute Reachable States of a CFFSM                               | 108 |

| 30 | Methodology for synthesizing control-units                                     | 112 |

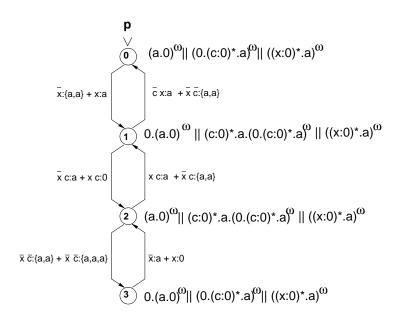

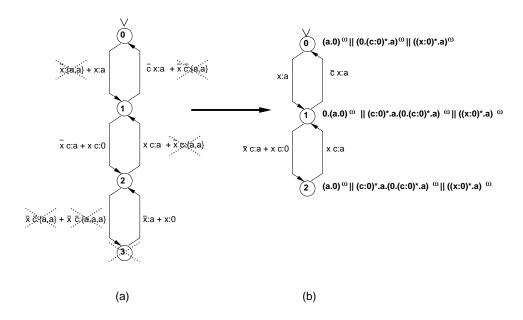

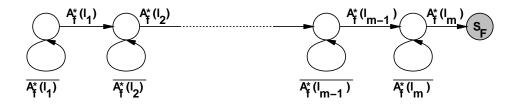

| 31 | (a) Graphical representation of CFE $p$ and (b) CFFSM for $p$                  | 123 |

| 32 | Finite-State Machine Representing the Path-Activated Constraint                | 124 |

| 33 | Algorithm to Compute a Minimum Path-Activated Constraint in a                  |     |

|    | CFFSM                                                                          | 127 |

| 34 | Algorithm to Compute a Maximum Path-Activated Constraint in a                  |     |

|    | CFFSM                                                                          | 128 |

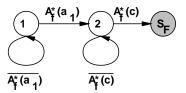

| 35 | Path-Activated Constraint FSM for min $(2, [a_1, c])$                          | 129 |

| 36 | Algorithm to Compute Solve                                                     | 137 |

| 37 | Implementation for CFFSM                                                       | 138 |

| 38 | Path cost selection in CFFSM                                                   | 146 |

| 39 | Implementations for control-flow expression $p_3 = ((x:0)^*.a)^{\omega} \dots$ | 148 |

| 40 | Block diagram of Parnassus Synthesis System                                    | 154 |

| 41 | Protocol conversion for PCI bus computer                                       | 158 |

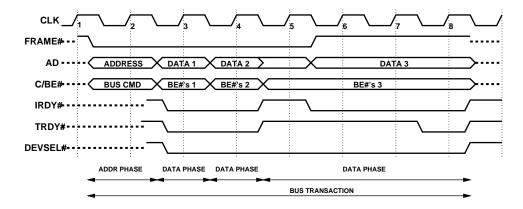

| 42 | PCI write cycle                                                                | 159 |

| 43 | PCI read cycle                                                                          | 159 |

|----|-----------------------------------------------------------------------------------------|-----|

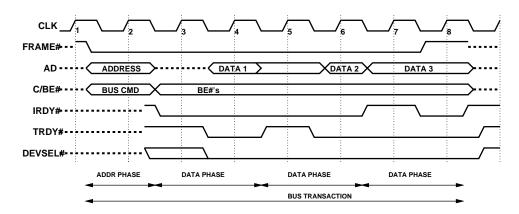

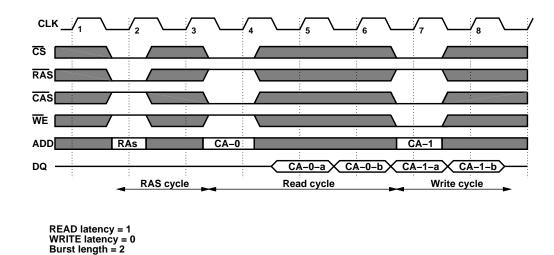

| 44 | SDRAM read and write cycles                                                             | 160 |

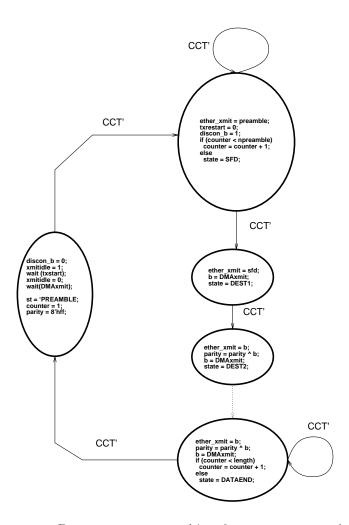

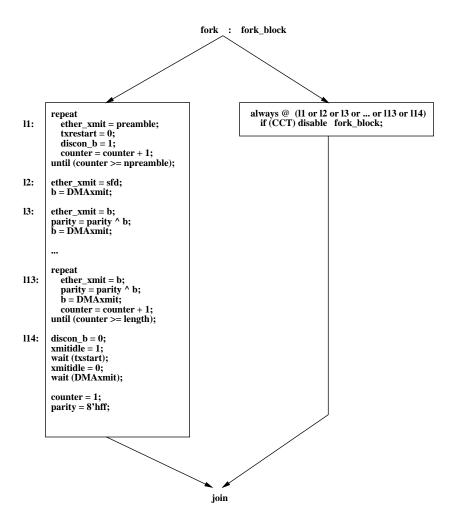

| 45 | Program state machine for process xmit_frame                                            | 161 |

| 46 | $Implementation \ of \ program \ state \ machine \ with \ exception \ handling \ . \ .$ | 163 |

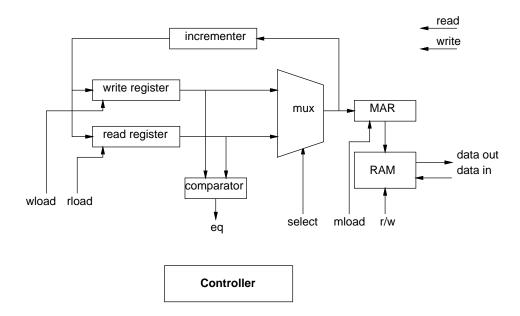

| 47 | Datapath for FIFO controller                                                            | 165 |

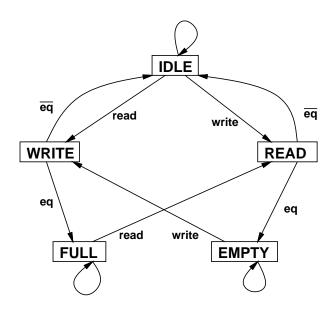

| 48 | High-level view of FIFO controller                                                      | 166 |

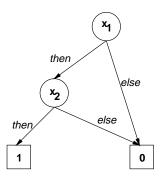

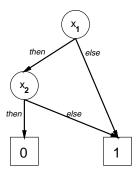

| 49 | Binary Decision Diagram for function $x_1x_2 \ldots \ldots \ldots$                      | 186 |

| 50 | BDD representing the constraint $4x_1 + 5x_2 \le 8$                                     | 187 |

#### Chapter 1

#### Introduction

The use of synthesis tools in synchronous digital designs at the logic and higher levels has gained large acceptance in industry and academia. Three of the reasons for its acceptance are the increasing complexity of the circuits, the need for reducing time to market and the requirement to design circuits correctly and optimally. In order to meet these requirements of today's marketplace, designers have to rely on the ability to specify their designs at higher levels of abstraction. In particular, designers depend upon models that describe the specification at a level higher than logic level and RTL level [Mic94].

Above the logic level of abstraction, circuit designs have been described at high-level and system-level. We denote by high-level abstraction the modeling style based on the representation of a circuit design by blocks of operations and their dependencies. High-level abstraction has been used effectively for representing designs in digital signal processing applications [VRB+93]. However, when representing designs that are better specified as a set of concurrent and interacting components, this abstraction level will not be able to capture the synchronization introduced by the components executing concurrently.

We call system-level abstraction a modeling style based on the description of concurrent and interacting modules and system-level synthesis the corresponding task of deriving a logic-level description from such a model. Concurrency allows designers to reduce the complexity by partitioning the circuit into smaller components. Communication guarantees that these concurrent parts will cooperate to determine the correct circuit behavior. For example, communication processors, such as the MAGIC chip [KOH+94] and an ethernet coprocessor [HLS], are representative designs of systems specified at this level of abstraction. These descriptions consist of several protocol handlers that execute concurrently and interact through data transfers and synchronization.

Traditionally, system-level designs have been synthesized by high-level synthesis tools [MPC90], where synthesis is performed by partitioning the circuit description into sequential blocks containing operations, which are scheduled over a discrete time and bound to components [KM92]. This technique is called *single process synthesis* in [WTHM92], since it ignores concurrency and communication in the beginning, thus focusing only on the sequential parts of the design. After the synthesis is performed on each concurrent component, they are combined at the lower levels, i.e. at RTL or logic-level. Note that at this level the results are already suboptimal and harder to optimize.

Single process synthesis imposes severe restrictions on system-level designs. First, since only one sequential component is synthesized at a time, the synthesis tool cannot consider the degrees of freedom available in other concurrent parts of the design. Second, the interface uses a model that does not consider communication. As a result, intricate relations between a model and its environment cannot be enforced during synthesis. Finally, single process synthesis targets area or delay optimization of each sequential block, which may not yield an optimal design since the design contains concurrent and interacting components. For example, the minimization of

the execution time in a concurrent specification requires the minimization of delays over execution paths.

This dissertation focuses on modeling, analysis and synthesis of concurrent and communicating systems. In particular:

- We present an algebraic model for concurrent and communicating systems that gives a formal interpretation for system-level descriptions, such that these systems can be abstracted, analyzed and synthesized.

- We present a technique for scheduling operations subject to complex interface constraints and synchronizations.

- We present a technique for synchronizing the concurrent parts of the design by dynamically scheduling operations or blocks of operations.

#### 1.1 Overview of System-Level Synthesis

System-level design contains sub-components showing sequential, alternative, concurrent, repetition and exception handling behaviors [GVNG94]. We assume that the design is originally specified by a description language supporting these behaviors, such as VHDL [LSU89], Verilog HDL [TM91], HardwareC [KD90], StateCharts [DH86], Esterel [BS91].

Synthesis of system-level designs differs from standard high-level synthesis [DKMT90, CBH+91, WTHM92, KLMM95] because the emphasis of the tool is placed on concurrent models and their interactions. In addition, implementation of system-level designs are often not confined to a single chip or a hardware implementation alone [Gup93]. As a result, the steps of partitioning, scheduling, synchronization, interface synthesis, and datapath generation in system-level synthesis will focus in the generation of

controllers subject to constraints crossing the concurrent models of the specification and different implementation paradigms.

In system-level synthesis, partitioning involves the selection of clusters of operations and models that should be synthesized together [DGL92, TWL95] and clusters that should be synthesized separately. A good partition will be obtained by clustering parts of the specification that are tightly coupled and share the same critical resources of the design. This will allow the tools used at the later stages of the design to better optimize the cluster.

Another important task of system-level synthesis is scheduling. Scheduling denotes the assignment of operations over discrete time slots. Although high-level synthesis also considered scheduling as a synthesis task, we emphasize here the differences between scheduling in high-level synthesis and scheduling in system-level synthesis. In high-level synthesis, the main emphasis is put into the scheduling of operations within a basic block. Optimality of a design in high-level synthesis is usually given in terms of the optimality of the execution time in basic blocks or the cost of resources in basic blocks, such as the number of multipliers, adders or multiplexors. In systemlevel synthesis, on the other hand, we have to consider the interactions that cross basic block boundaries as well. When the system is partitioned in clusters some of the interactions of the system are converted into environment constraints, which should guide the tool in finding feasible and optimal implementation. Whenever these environmental constraints cross implementation paradigms (such as hardware and software), appropriate synchronization must be added as well. In addition to this, the optimality criteria in system-level synthesis shifts from basic blocks to whole parts of the design. For example, in a cache controller, the specification can be divided into a hit and miss case, both of which can share some parts of the specification. Since the hit case is going to be executed more often than the miss case, the primary optimization goal should be the minimization of the execution time of the hit path, and using the minimization of the execution time of the miss case as a secondary goal.

Synchronization and interface synthesis refers to the generation of protocol converters for some parts of the design. At the system-level of the specification, the user may have not committed to a protocol for the communication of the events across concurrent parts of the design, or the specification of the protocol may already exist in the form of libraries. In synchronization synthesis, the tool produces protocols for the communication among different parts of the specification, and generates converters between protocol libraries and the specification, according to the design constraints.

Finally, in datapath generation we obtain datapaths for the operations and their dependencies in the specification. During datapath generation, the tool selects components for an implementation, binds the components to operations, and binds the variables of the specification into registers.

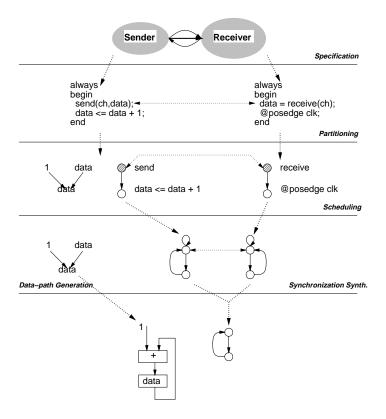

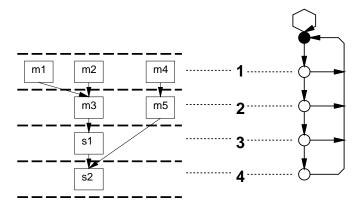

Figure 1 gives an example of the tasks involved in the synthesis of system-level designs. From the specification of a concurrent system, a system-level tool first partitions the description and generates a set of crossing these partitions, then the tool schedules the operations over a discrete time according to the environmental constraints, synthesizes the synchronization skeletons and protocols for the different parts of the specification, and generates datapaths for the operations and variables.

#### 1.2 Synthesis Tools used for System-Level Designs

Many systems implemented by Application Specific Integrated Circuits (ASICs) are control-dominated applications [Keu89]. In such applications, high-level synthesis techniques have been used previously to synthesize control-units for system-level designs.

Figure 1: System-level tasks

The Olympus Synthesis System [DKMT90] targets control-dominated ASIC designs. Starting from the high-level language HardwareC, the system performs the high-level synthesis tasks of scheduling operations over discrete times, binding operations to components and variables to registers. One of the unique features of the Olympus Synthesis System is that it allows the user to specify synchronization and data transfers using high-level message passing communication constructs. In this system, send and receive operations are used to generate synchronizations and to transfer data across concurrent models. Although HardwareC allows the system to be specified using concurrent and communicating modules, the synthesis technique applied in these modules considers only one module at a time, preventing the synthesis of a single module.

The HIS System [CBH+91] was developed at IBM to synthesize mixed dataflow intensive/control-flow intensive specifications. The system being synthesized was first partitioned into its control-flow/dataflow components, for which a control unit and datapath were generated, respectively [Cam91]. In path-based scheduling, operations in a path can be scheduled into a single discrete time as long as it does not have any conflicts with the other operations scheduled in the same discrete time. Because scheduling is performed on a path-basis, this algorithm is able to schedule operations across sequential, alternative and repetitive control-flow structures.

The Princeton University Behavioral Synthesis System [WTHM92] (PUBSS) and the Synopsys Behavioral Compiler [KLMM95] were conceived using ideas similar to those of the HIS system. Both systems allow control-flow with arbitrary sequential, alternative and repetitive behaviors. In addition to that, PUBSS is able to consider more aggressive timing constraints than the previous systems described in this section, called *path activated constraints*. PUBSS is also able to handle the tightly coupled parts of the design by merging them together during synthesis. Nevertheless, it is not able to cross parallel composition barriers, which may exist in Verilog or StateChart descriptions.

The Clairvoyant system [Sea94] was designed for the specification and control generation of control-dominated applications using a grammar-based specification language. The system is specified using a grammar languages supporting sequential, alternative and parallel composition, loops, synchronization and exception handling. Since the Clairvoyant system does not allow the incorporation of any design constraints, the synthesis technique is limited to a syntax-directed translation from the grammar specification to the control-unit, and thus all timing information must be already present and scheduled during the specification of the design.

We will describe in this thesis a tool called *Thalia* <sup>1</sup> for system-level synthesis

<sup>&</sup>lt;sup>1</sup>The muse of comedy

that will be unique because it will be able to handle several of the design issues regarding system-level designs, some of which were mentioned in this section. We will consider specifications containing sequential, alternative, parallel compositions, loops and exception handling mechanisms. Such constructs are present in Verilog, StateCharts, and VHDL. We will not limit the specifications to contain concurrency only at the highest levels of the specification, as it is the case in IBM Synthesis System, PUBSS and Synopsys Behavioral Compiler. We will be also consider general forms of design constraints, which will help us to model the environment, and flexible objective functions, which will help us to better cast our design goal.

In the next section, we will present some design problems that will help us to better understand the issues in system-level synthesis.

#### 1.3 Issues in System-Level Synthesis

This section presents examples of designs that either cannot be synthesized or are synthesized sub-optimally by typical high-level synthesis tools. We show intuitively that valid and optimal implementations can be obtained only if synchronization, dynamic scheduling and scheduling with complex timing and resource constraints are considered during the design space exploration.

One of the major problems of using current synthesis tools to implement systemlevel designs is that the tool must consider how the environment affects the model being synthesized. Since the specification of the environment in which the circuit is going to execute is generally a formidable task, the user must have a better control over the synthesis tool in order obtain optimal results. With *Thalia*, the user can specify complex environment constraints and flexible cost functions.

In the next three examples, we motivate the reader about the need for tools that can handle concurrent and communicating systems.

#### 1.3.1 Synchronization Synthesis

In this example, we show how we can synchronize multiple processes sharing the same critical resource. We will see that this synchronization can be synthesized only if we consider the degrees of freedom among the different processes that share the critical resource. We are going to see that the model being synthesized will have to dynamically reconfigure itself in order to allow other models to use the same resource at different times. In this example, in order to obtain a feasible solution, we have to specify a constraint that spans across concurrent models, i.e., the critical resource should not be used by more than one model at a time.

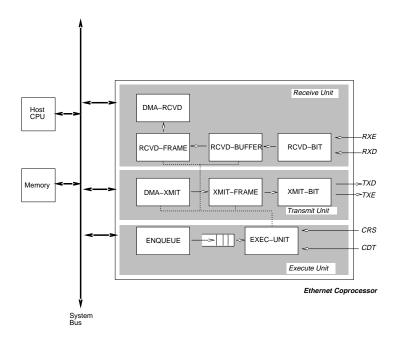

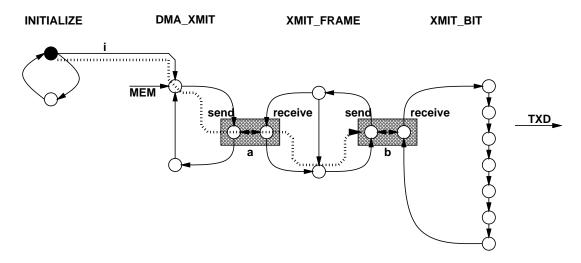

Figure 2: Ethernet controller block diagram

The block diagram of an ethernet coprocessor is shown in Figure 2. This coprocessor contains three units: an execution unit, a reception unit and a transmission unit. These three units are modeled by thirteen concurrent processes, with three processes accessing the bus: DMAxmit, DMArcvd, and enqueue. The problem we want to

solve is the synthesis of the synchronization among the three processes such that any bus access for the three processes is free of conflicts. Note that the difficulty in solving this problem comes from the transfers that are non-deterministic over time, i.e., we do not know a priori when each process accesses the bus, since this operation is control dependent. Also, the transfers of different processes are uncorrelated, i.e. knowing that one process accesses the bus at a specific time does not imply the transfers in other processes are known.

#### Related Work in Synchronization Synthesis

The problem of synchronizing critical resources across concurrent models has been solved for the simplified assumption that the models are dataflows executing at the same rate [HP92]. Note that in the problem described here, however, we do not know when each bus access will take place, since we may have arbitrary control-flow specifications that will make the bus accesses to be dependent on the environment and to execute at different rates. Thus, the approach described in [HP92] cannot be used for the bus accesses of the ethernet coprocessor described here.

Filo et al. [FKJM93] addressed the problem by rescheduling transfers inside a single loop or conditional to reduce the number of synchronizations among processes. This method is restrictive because all transfers that are optimized must be enclosed in the same loop or conditional, and only the synchronizations due to the transfers are considered during the simplification. A synchronization is eliminated if its execution is guarded by a previous synchronization. As we are going to show later, our formalism allows processes to be specified by their control-flow with an abstraction on the dataflow parts, and thus will subsume the solutions found by the two approaches previously discussed. Also, our formalism achieves the simplification of synchronization that crosses loops and conditionals, and we do not restrict this simplification to only transfers present in single loops or conditional branches, as in [FKJM93].

In [CE81], the system was specified by a set of finite state machines and a set of properties specified using CTL (Computation Tree Logic) formulae. These formulae characterized the desired behavior of the system in terms of safety ("nothing bad ever happens") and liveness ("something good eventually happens") properties. Each machine of the system was considered to execute asynchronously with respect to the other machines, and a product machine was obtained by combining the machines of all specifications. A synchronizer was extracted from the product machine such that this sub-machine satisfied the set of CTL formulae. A similar method was also reported in [Wol82], but using linear time temporal logic formulae for specifying the temporal properties of the system. This model considered concurrency of the specifications as an interleaving of executions, as opposed to the model we will define in the next chapter, which will consider true concurrency. As a result, the synchronizers generated by these procedures will be subject to much stricter constraints than they will experience.

Zhu et al. [ZJ94, ZJ93a] used timing expressions to capture synchronizations of models. A timing expression is an expression containing timing relations between a set of signals, which are expressed using traces of executions. In his descriptions, the system is specified by a set of timing expressions and the synchronization is specified by a set of constraints a system has to satisfy. These constraints have been solved by [Zhu92] using an algorithm that returns a set of timing expressions for the synchronizers. Timing expressions can be useful for determining relationships among signals in a timing diagram, as shown in [ZJ94], when every signal of a timing diagram is represented by a timing expression and the synchronization constraints represents how these signals interact. However, timing expressions will not be able to capture the intricate relations that are present in higher-level descriptions.

#### Synchronization Synthesis for the Ethernet Coprocessor

Let us first consider an abstraction of the original specification that captures only the bus accesses. Furthermore, in order to be able to discuss this problem throughout this paper, we will assume a set of reduced behaviors for *DMArcvd*, *DMAxmit* and enqueue such that the resulting behavior is small enough that can be easily understood. Figure 3 presents the behaviors we assume for these descriptions in this paper, in a pseudo-Verilog code. In this figure, the constructs that do not belong to the language, such as write bus, are represented in typewriter style; reserved words of Verilog are represented in bold; and other legal syntactic constructs are represented in italics. The signal transmission ready is assumed to be set by the environment surrounding the three processes, and free bus represents the waiting period for process enqueue.

```

module DMAxmit;

module DMA rcvd;

module enqueue;

always

always

always

begin

begin

begin

write bus;

initialize variables

wait (free bus);

data = receive(from\_xmit\_frame);

wait (transmission ready);

read bus;

end

read bus;

end

end mod ule

endmodule

end

endmodule

```

Figure 3: Abstracted behaviors for DMArcvd, DMAxmit and enqueue

The processes shown in the figure are control-dominated specifications where the flow of control is modified by some set of wait statements. In this example, also, note that the priority of *enqueue* should be the smallest one, since the execution of the bus access in this process may be delayed. On the other hand, if the bus accesses of the other processes are delayed, the controller will not be able to deliver data at the interface at the proper rate.

We assume that processes *DMArcvd* and *DMAxmit* have already been synthesized,

and their cycle-based behaviors are presented in the figure. We are interested in obtaining a control-unit for process enqueue such that it will not have conflicting bus accesses with neither DMArcvd nor DMAxmit. Note that in order to synthesize the waiting period for enqueue we must know when the other process will access the bus. Therefore, enqueue must have a global view of the bus accesses of the other processes in order to decide when it can access the bus.

If we assume that every operation takes one clock cycle, an implementation for the synchronization mechanism of the bus should establish a temporal relation between enqueue and the two other processes DMAxmit and DMArcvd. This temporal relation should include any data-dependent operation of the two other processes, such as the conditional  $transmission\ ready$ , and it should also consider when the other processes access the bus. A possible solution to this problem would be:

In this implementation, we have to wait the first cycle because *DMArcvd* is accessing the bus in the first cycle. During the second cycle, *enqueue* will be able to access the bus only if *DMAxmit* is not accessing it. In the following cycle, however, *DMArcvd* will be accessing the bus again, and *enqueue* will have to wait for another cycle. We will show later how this controller could be obtained automatically for the process *enqueue*.

# MEMORY ASIC send(addr,data)

#### 1.3.2 Scheduling under Complex Interface Constraints

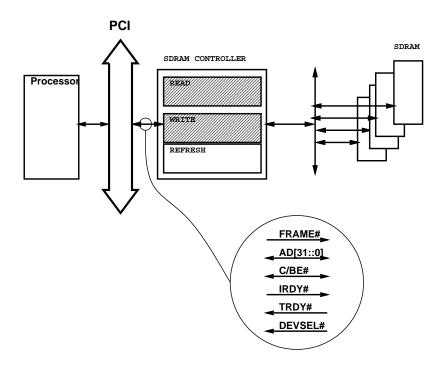

Figure 4: System architecture

In this example, we show how we can specialize a design by incorporating dynamic scheduling constraints from an interface. Splitting the interface specification from the design specification was addressed in [NG95, KM92, NT86, Bor88]. One of the main advantages of abstracting interface implementation details at the higher levels of abstraction is that more degrees of freedom can be explored during synthesis.

In such techniques, the transfers among processes are abstracted in terms of communication operations (such as a *send* operation). During synthesis, the best protocol and communication medium is selected to implement a particular transfer. The selection and synthesis of the protocol interface will impose complex scheduling constraints to the design, as we will see below.

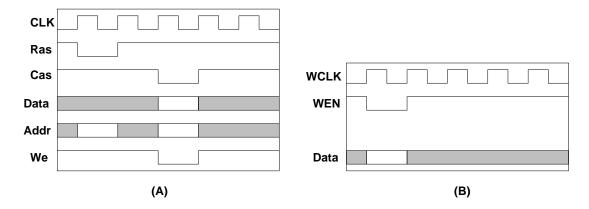

Consider a system that has an ASIC and an embedded processor, such as the one given in Figure 4. Assume the ASIC communicates with the microprocessor either through a synchronous memory or through a synchronous FIFO. For example, this structure has been used in hardware-software codesign [GJM92, GJM94]. In this system, the transfers to the memory and to the FIFO are determined at run-time by the proper selection of the address. The interface timing is also determined at run-time, since the timing specifications for these two components are different, as

Figure 5: Writing cycles for synchronous DRAM (a) and for synchronous FIFO (b)

given in Figure 5. In essence, a data transfer may take either one or three cycles to complete. Thus, the timing constraint specification should also reflect the mismatch between the timing of the components.

The specification of interface constraints has been used in the past by Nestor [NT86], Ku [KM92] and Borriello [Bor88]. They used min/max scheduling constraints to annotate the design specification. The use of these constraints, however, is limited to static constraints. In the example presented above, the specification of the interface requires the design to contain implementation details, which is not desirable for the reasons given previously.

Assuming that the address selection for the memory module is called s, the constraint that we need to specify is a three-cycle operation or a one-cycle operation, depending on s. Thus, the interface can no longer be specified in terms of fixed minimum/maximum delay between operations, since the execution time of the operation is dependent on the address selection. In order to synthesize the protocol for the send operation given above, we must consider a dynamic schedule for this operation.

This can be achieved by using the alternative composition in the constraint specification. For example, one possible representation for this constraint could be:

```

synchronize with "send" operation

if (s)

delay for "send" is 3 cycles

else

delay for "send" is 1 cycle

```

We will show that using the algebra of control-flow expressions, we can represent this constraint as the following compact representation:

$$s: Ras \cdot 0 \cdot \{Cas, data\} + \overline{s}: data$$

where Ras is an abstraction to the RAS cycle of the RAM, Cas is an abstraction of the CAS cycle of the RAM, 0 is a one-cycle delay operation, data is an abstraction of the data transfer, and  $\overline{s}$  means that s is false.

During the synthesis procedure, the send operation is bound to an implementation that observes this constraint. In this case, the implementation is exactly the control that waits either one or three cycles, depending on s.

In this example, the two different communications mechanisms assume different possible behaviors for the environment. Depending on how the environment requires data, one mode should be highlighted over the other for some transfer by the proper selection of an objective function.

#### 1.4 Objectives and Contributions

In this thesis, we present a formal model to analyze system-level designs targeted to control-flow intensive applications, and a methodology to synthesize the control-units for the concurrent parts of the design. Because many applications found in Application Specific Integrated Circuits are control-dominated applications [Keu89], we will address the following issues regarding control-flow dominated system-level designs.

- Modeling. We will present a model to represent the control-flow of concurrent systems that includes most of the control-flow constructs present in specification languages, such as sequential, parallel and alternative compositions and loops. In addition to that, our model will support exception handling mechanisms which are present in languages such as Verilog HDL, Esterel and StateCharts. We will also allow systems to be specified with programming languages, such as C. Finally, we will include in our model some of the variables of the specifications, since in some cases these variables can give a better understanding of the control-flow behavior in such systems.

- Constraints. We will show how we can incorporate complex constraints of the design. The constraints of the design will not be limited to the constraints usually specified in high-level synthesis tools, but we will also allow the model's environment to be specified and to synchronize with the model being synthesized.

- Analysis. We will present techniques for analysis of the specification and its environment in a finite-state machine representation, and we will show how we can efficiently represent this finite-state machine. In this finite-state machine, we will be able to detect when no control-unit can be obtained for a specification when the specification is composed with its environment.

- Synthesis. We will present two techniques for solving the scheduling and synchronization synthesis problems. In the first technique, we will schedule operations statically over time to satisfy complex interface constraints. In the second technique, we will dynamically schedule the interacting parts of the specification in order to synchronize them. These schedules and the specification can be used to obtain a control-unit for the circuit description that optimizes a design goal, while satisfying the environment constraints.

#### 1.5 Thesis Outline

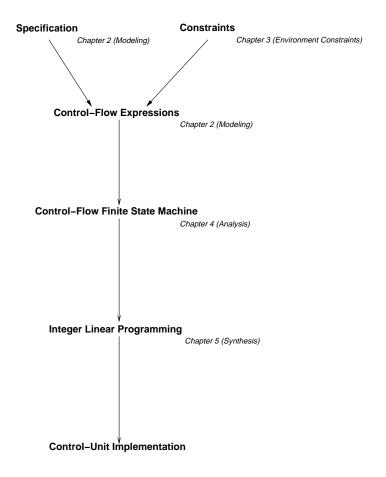

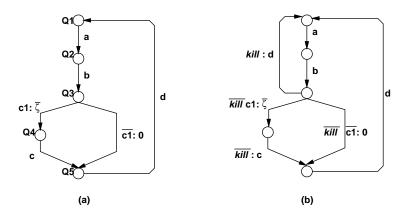

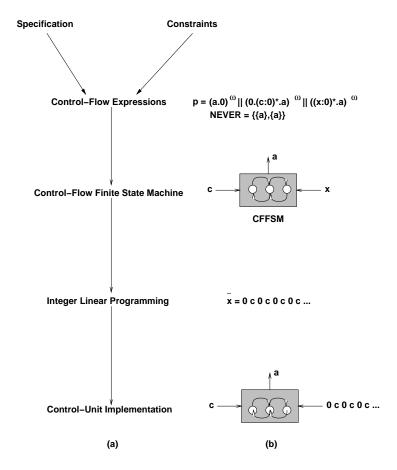

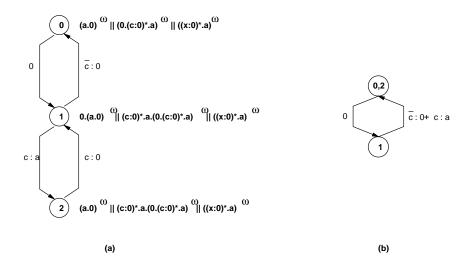

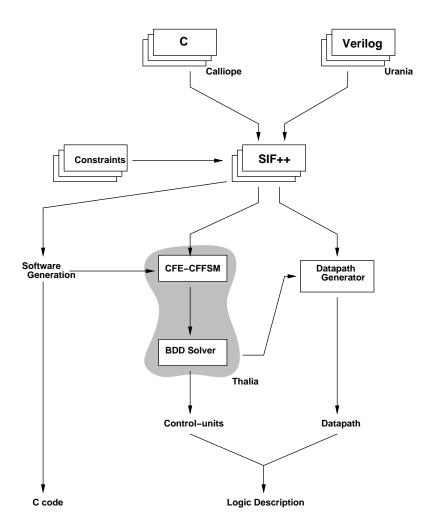

The outline of this thesis (which is also the outline of the tool we developed) can be seen in Figure 6.

Figure 6: Thesis outline

After the introduction and motivation described in this chapter, Chapter 2 describes our model for concurrent control-dominated systems, called *control-flow expressions*. There, we present the algebra of control-flow expressions, and we show how this algebra can be used to model the control-flow aspects of a specification. Then, we present extensions to the algebra of control-flow expressions that will allow us to consider more realistic system-level designs, by incorporating some variables into the

control-flow model, and by allowing the specification to contain exception handling mechanisms.

Since our model assumes that the system will be interacting with other models and with the environment, in Chapter 3 we will present techniques to incorporate design constraints into control-flow expressions. These constraints will include timing, resource and synchronization constraints.

Chapter 4 presents a method to analyze the system consisting of control-flow expressions by converting the system into a specification automaton that contains all degrees of freedom of the system being synthesized. We will also show how to represent this specification automaton in terms of a transition relation, and how to efficiently encode the different constructs of the control-flow expressions into the transition relation.

Chapter 5 describes two synthesis methods for scheduling operations and synchronizing parts of the description. Both of these algorithms are implemented as restrictions on the behavior of the specification automaton obtained in the previous chapter.

Chapter 6 presents some design examples and how they could be solved using the formulation presented in this thesis. Finally, in Chapter 7, we will present some concluding remarks and some ideas for future research.

#### Chapter 2

# Modeling of Concurrent Synchronous Systems

We will be focusing in this chapter on a model for control-dominated system-level descriptions. Since system-level descriptions are usually specified as sets of concurrent components interacting among themselves and with the environment, an optimal controller can be obtained only if we understand the underlying behavior of the system to be synthesized, and its relation to the environment.

We model the system in terms of control-flow and dataflow for each concurrent component. We will first attempt to restrict the control-flow to the control-flow constructs of conventional structured languages, and we will restrict the dataflow model to the variables, and their corresponding operations. This abstraction model is presented in Section 2.1.

In Section 2.2, we present the algebra of *control-flow expressions*, which is an algebraic model for representing the control-flow of system-level designs, while abstracting away the dataflow details. In Section 2.3, the axioms of control-flow expressions will be introduced. These axioms form the basis for the analysis technique we will develop in the next chapter.

In order to better analyze the control-flow of system-level designs, it will be shown in Section 2.4 that variables and operations may play a fundamental role in defining the control-flow behavior, and we will show which parts of the dataflow must be considered during analysis and synthesis of control-flow dominated specifications. In addition to that, in order to capture basic blocks of traditional programming languages and hardware description languages, we will introduce blocks in control-flow expressions. Finally, exception handling mechanisms will also be added to control-flow expressions in order to capture the rupture of structured control-flow in the designs, usually due to the occurrence of exceptions that is common to most hardware description languages.

In Section 2.5, we compare extended control-flow expressions with existing formalisms that capture the control-flow of concurrent systems.

#### 2.1 Abstraction Model

We consider in this thesis system-level designs that will be synthesized as synchronous digital circuits running under the same clock. In the synthesis of these designs, we need to represent the interactions among the concurrent parts, which can be best modeled at the control-flow level.

We assume in our computation model that the specification will be partitioned in terms of a control-flow and a dataflow, as described in [DGL92, Mic94, ZJ93b]. In this model, variables, their operations and operands are placed in the dataflow, and the constructs determining the flow of control of the specification language are placed in the control-flow. I/O operations between a process and the process external environment will be placed in the dataflow. We formalize this model below.

#### Dataflow

We define a dataflow by its structure, without considering the meaning of the operations in the specification, similarly to the definitions of [ZJ93b]. Let  $\mathcal{V} = \{v_1, \ldots, v_n\}$ be a set of variables, and let v be a generic element of  $\mathcal{V}$ . We assume that constant values are specified by variables whose names are represented by the constant value. Let  $\mathcal{F}$  be a set of functions whose typical elements are f and  $f_i$ .

**Definition 2.1** An operation is defined as  $v \leftarrow f(v_1, \ldots, v_n)$ , i.e., variable v is assigned the result of function f, when the function's parameters are set to the variables  $v_1, \ldots, v_n$ .

We call the set of operations  $\mathcal{O}$ . A dataflow can be defined as a set of operations and a partial order among them. It can be depicted as a directed acyclic graph in which vertices are operations and edges correspond to dependencies among the operations. Each edge is annotated with the variable that creates the dependency.

#### Control-Flow

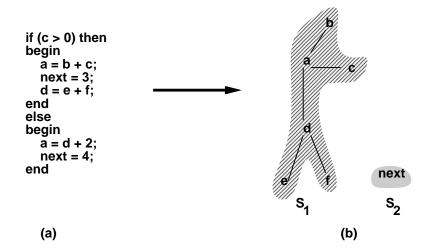

In a hardware specification, as well as in a software program, the sequencing of the operations is determined by control-flow constructs, such as procedure calls, branching and iteration. In particular, descriptions can be made hierarchical by using procedure calls, which encapsulate portions of the behavior. Such a hierarchy may be abstracted as a directed acyclic graph, whose root corresponds to the overall system, whose internal vertices correspond to sequential, parallel, alternative and iterative compositions, and whose leaves are either operations, or groups of operations and dataflow models.

Different models [DGL92, Mic94, GVNG94] have been proposed to represent branching and iteration. In this thesis, we represent branching and iteration hierarchically, with their bodies being modeled as procedure calls, i.e. at a lower level in the representation hierarchy. Such calls are invoked conditionally according to the value of the branching or iterative clauses.

Note that in the control-flow and dataflow models defined above, the execution of the control-flow is data-dependent, and because the dataflow is conditionally executed, according to the control-flow, the dataflow is control-dependent. Since at this level of abstraction, the execution time for the operations is not known yet, in order to consider the communication between the dataflow and the control-flow we model the interface by instantaneous events. The control-flow generates output events to the dataflow that sensitize the execution of operations in the dataflow. The dataflow generates input events to the control-flow that trigger the different execution paths.

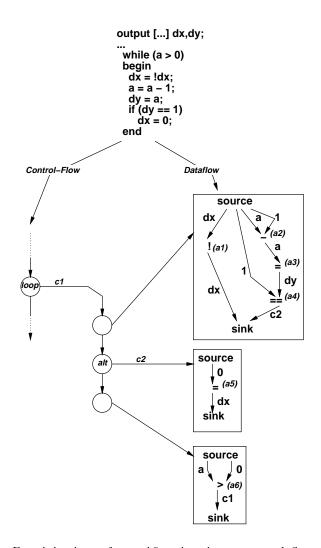

**Example 2.1.1**. In Figure 7, we show the representation of a specification in terms of its control-flow and dataflow graphs.

The vertices *loop* and *alt* in the control-flow graph represent iterative and alternative behavior, respectively.

We labeled each operation in the dataflows by events  $a_1, \ldots, a_6$ . Such events are generated by the control-flow and determine when the corresponding operations will execute. Event  $a_1$ , for example, triggers the execution of the negation of dx. These events determine the dependency of the dataflow with respect to the control-flow. Each dataflow also contains two vertices, *source* and *sink* that do not correspond to any operation in the specification. They mark the beginning and end of execution of the dataflow, respectively.

The dataflow of Figure 7 generates input events  $c_1$  and  $c_2$  that trigger the execution of the loop and the execution of the alternative path, respectively. These events determine the dependency of the control-flow in terms of the dataflow.

The reader should note that the control-flow does not make any assumptions on the possible values of its input events over time. In this example, we assume that entering the loop (when event  $c_1$  is generated) and exiting the loop are equally probable, for example.  $\square$

We model a concurrent system by looking at the interface between the dataflow and the control-flow, i.e. at the events the control-flow generates and consumes. As a result, we need to abstract dataflow details from our model. We abstract the details

Figure 7: Partitioning of specification into control-flow/dataflow

from the dataflow by considering three mappings at the interface between the dataflow and control-flow: a timing mapping, a binding mapping and a synchronization mapping. The timing mapping associates an execution time with every computation or component. The binding mapping associates the possible functions of a computation with their possible implementations. Finally, the synchronization mapping specifies how the concurrent parts interact. The control-flow and the three mappings defined

in this paragraph provide the means by which we can analyze the validity of the specification with respect to design constraints, as well as the means to generate possible implementations.

# 2.2 Algebra of Control-Flow Expressions

The algebra of control-flow expressions (CFEs) is defined by the abstraction of the specification in terms of the sensitization of paths in the dataflow, and by the compositions that are used among these operations. As presented in the previous section, we view the communication between the dataflow and control-flow as an event generation/consumption process. More formally, we call the output events generated from the control-flow actions (from some alphabet  $\mathcal{A}$ ). We assume that each action will execute in one-unit of time (or cycle). If an operation executes in multiple cycles, they will be handled by a composition of single-cycle actions.

**Example 2.2.2**. The C fragment presented below corresponds to a part of a differential equation solver found in [Mic94].

```

xl = x + dx;

ul = u - (3 * x * u * dx) - (3 * y * dx);

yl = y + u * dx;

c = x1 < a;

```

During the compilation of this description, the expressions are broken into a set of predefined operations including addition, multiplication, subtraction and comparison.

```

m1 = 3 * x;

/* m1 */

/* m2 */

m2 = u * dx;

m3 = m1 * m2;

/* m3 */

/* m4 */

m4 = 3 * y;

m5 = m4 * dx;

/* m5 */

/* m6 */

m6 = u * dx;

/* a1 */

a1 = x + dx;

y1 = y + m6;

/* a2 */

```

```

c = a1 < a; /* lt */

s1 = u - m3; /* s1 */

u1 = s1 - m5; /* s2 */

```

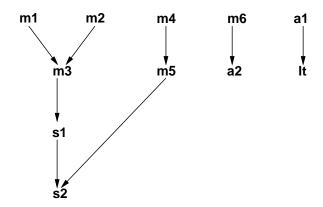

If we assume that each operation described above executes in one cycle, we can represent the operations above by actions  $m_1, m_2, m_3, m_4, m_5, m_6, a_1, a_2, lt, s_1$  and  $s_2$ , according to the comments to the right of the code.  $\Box$

We represent the input events of a control-flow by conditionals, which are symbols from an alphabet C. The conditionals in a control-flow expression will enable different blocks of the specification to execute. Guards will be defined as the set of the Boolean formulas over the set of conditionals.

**Definition 2.2** A guard is a Boolean formula on the alphabet of conditionals. We will use  $\mathcal{G}$  to denote the set of guards over conditionals.

We assume that each guard and conditional is evaluated in zero time. At the end of this section, we compare the assumptions on the execution time of actions, conditionals and guards with the synchrony hypothesis.

**Example 2.2.3**. In the specification if  $(x \ge y)$  x = y \* z, a conditional c abstracts the binary relational computation  $x \ge y$ . If at some instant of time, the *guard* c is *true*, x = y \* z is executed. If at some instant of time, the *guard*  $\neg c$  is *true*, the else branch (which is null in this case) is executed.  $\square$

Using control-flow expressions, we model systems by a set of operations, dependencies, concurrency and synchronization. We encapsulate sub-behaviors of this system in terms of processes, which are represented by control-flow expressions and correspond to an HDL model. In our representation, each process is a mapping from labels of the alphabet  $\mathcal{F}$  to control-flow expressions.

We define the set  $\Sigma$  as the alphabet of actions, conditionals and processes  $\Sigma = \mathcal{A} \cup \mathcal{C} \cup \mathcal{F}$ .

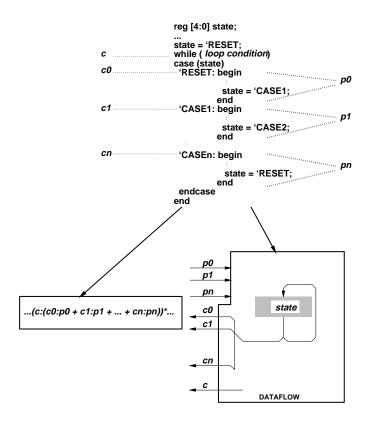

The compositions that are defined in the algebra of control-flow expressions are the compositions supported by existing HDLs which were captured by the control-flow model described earlier. Verilog HDL, for example, supports sequential composition, alternative composition, loops, parallelism and unconditional repetition. The same set of compositions is also supported in VHDL and HardwareC, and thus is supported by control-flow expressions. Since alternative compositions and loops in these languages are guarded, their corresponding compositions in CFEs will also be guarded.

The set  $\mathcal{O} = \{sequential(\cdot), alternative(+), guard(:), loop(*), infinite(\omega), parallel(||)\}$  is defined to be the valid compositions of control-flow expressions. The formal definition of the algebra of control-flow expressions is presented below:

## **Definition 2.3** Let $(\Sigma, \mathcal{O}, \delta, \epsilon)$ be the algebra of control-flow expressions where:

$\Sigma$  is an alphabet that is subdivided into the alphabet of actions, conditionals and processes;

O is the set of composition operators that define sequential, alternative, guard, loop, infinite and parallel behavior;

$\delta$  is the identity operator for alternative composition;

$\epsilon$  is the identity operator for sequential composition.

We can now define the control-flow expressions recursively.

### **Definition 2.4** Control-flow expressions are:

- Actions  $a \in \mathcal{A}$ .

- Processes  $p \in \mathcal{P}$ .

- $\delta$  and  $\epsilon$ .

- If  $p_1, \ldots, p_n$  are control-flow expressions, and  $c_1, \ldots, c_n$  are guards, then the following expressions are control-flow expressions.

- The sequential composition, represented by  $p_1 \cdot \ldots \cdot p_n$

- The parallel composition, represented by  $p_1 \| \dots \| p_n$

- The alternative composition, represented by  $c_1: p_1 + \ldots + c_n: p_n$

- Iteration, represented by  $(c_1:p_1)^*$

- Unconditional repetition, represented by  $p_1^{\omega}$ .

Nothing else is a control-flow expression.

Informally, we define the behavior of the compositional operators of CFEs as follows: the sequential composition of  $p_1, \ldots, p_n$  means that  $p_{i+1}$  is executed only after  $p_i$  is executed, for  $i \in \{1, \ldots, n \Leftrightarrow 1\}$ . The parallel composition of  $p_1, \ldots, p_n$  means that all  $p_i$ 's begins execution at the same time for  $i \in \{1, \ldots, n\}$ . The alternative composition of  $p_1, \ldots, p_n$  guarded by  $c_1, \ldots, c_n$ , respectively, means that  $p_i$  only begins execution if the corresponding  $c_i$  is true. Iterative composition means that  $p_1$  begins execution while the guard  $c_1$  is true. The infinite composition means that  $p_1$  begins execution infinitely many times upon reset.

We introduced in the previous definition the symbol  $\delta$  that is called here  $deadlock^1$ . The symbol  $\delta$  is defined as  $\delta \triangleq false : p$ , where p is any control-flow expression. The deadlock symbol is an identity for alternative composition. This means that the branch of the alternative composition represented by the deadlock is never reachable. Later we show that these branches can in fact be removed.

<sup>&</sup>lt;sup>1</sup>Deadlock was the name given to  $\delta$  in process algebras. In synthesis,  $\delta$  denotes code that is unreachable due to synchronization. Since its properties are the same as the properties for deadlock in process algebras, we used the latter name, for the sake of uniformity.

We also introduced the symbol  $\epsilon$ , which is called here the *null computation*. The *null computation* symbol is defined as a computation that takes zero time. For example, this symbol can be used to denote an empty branch of a conditional. This symbol behaves as the identity symbol for sequential composition.

Note that in our definition of the syntax of CFEs, every loop and every alternative branch is guarded by ":", which makes the different branches of alternative and loops distinct. We also assume that only one alternative branch will be taken at any given time. This restricts the specification of loop bodies and alternative branches to only accept deterministic choices with respect to the guards.

For the sake of simplicity, we restrict the sets of behaviors definable in control-flow expressions in the following way: it should always be possible to obtain a control-flow expression without any process variables, i.e. we should be able to eliminate recursion from a control-flow expression by substituting process variables by their respective CFE, with the recursion on a process variable being replaced by iterative or unconditional repetition. In this thesis, whenever we refer to a CFE p, we are referring to the CFE without recursion defined by the process variable p.

Although this assumption seems to constrain the representation model using CFEs, in practice this will not impose problems because CFEs captures exactly the control-flow constructs of structured languages such as Verilog HDL and VHDL. With respect to C, we use a subset of C that does not allow a function to be defined recursively in order to avoid the possibility of having a CFE with process variables for which no CFE without process variables can be obtained. Later in this chapter we will enrich control-flow expressions by allowing CFEs to break the conventional flow of control, as in the case of breaks, continues and returns of the C programming language, or as in the case of disables of the Verilog HDL.

In control-flow expressions, we consider a special action called 0, which corresponds to a no-operation or abstraction of the computation. Action 0 executes in one

| Composition | HL Representation                                                            | CF Expression        |

|-------------|------------------------------------------------------------------------------|----------------------|

| Sequential  | $\mathbf{begin}\ p;q\ \mathbf{end}$                                          | p.q                  |

| Parallel    | fork $p; q$ join                                                             | p  q                 |

| Alternative | $\begin{array}{c} \mathbf{if}(c) \\ p ; \\ \mathbf{else} \\ q ; \end{array}$ | $c:p+\overline{c}:q$ |

| Loop        | $\begin{array}{c} \mathbf{while}\;(c) \\ p \; ; \end{array}$                 | $(c:p)^*$            |

|             | $\begin{array}{c} \mathbf{wait} \ (!c) \\ p \ ; \end{array}$                 | $(c:0)^*.p$          |

| Infinite    | always  p;                                                                   | $p^{\omega}$         |

Table 1: Link between Verilog HDL constructs and control-flow expressions

unit-delay (just as any other action), but it corresponds either to an unobservable operation of a process with no side effects or to a unit-delay between two computations.

Whenever possible, we will relate the HDL constructs to control-flow expressions, instead of using the control-flow/dataflow model described earlier for sake of simplicity.

The semantics of the major control-flow constructs in HDL are related to control-flow expressions in the table in the Table 1, where p and q are processes  $(p, q \in \mathcal{F})$  and c is a conditional  $(c \in \mathcal{C})$ . In this figure, we relate CFEs to the control-flow structure of Verilog HDL [TM91]. In this thesis, we assume that guards (:) have precedence over all other composition operators; loops and infinite composition  $(*,\omega)$  have precedence over the remaining compositions; sequential composition  $(\cdot)$  has precedence over alternative and parallel composition; alternative composition (+) has precedence over the parallel composition. In addition to that, we use parentheses

to overrule this precedence and for ease of understanding. Although it is not necessary, we will at times replace parentheses by square brackets for clarity.

We will use the following shorthand notation for control-flow expressions. The control-flow expression  $p^n$  will denote n instances of p composed sequentially  $(\underline{p \cdot \ldots \cdot p})$ , which corresponds, for example, to a counting loop that repeats n times in some HDL. The control-flow expression  $(x:p)^{\leq n}$  will denote a control-flow expression in which at most  $n \Leftrightarrow 1$  repetitions of p may occur. This CFE is equivalent to  $(x:p+\overline{x}:\epsilon)^{n-1}$ .

In our original specification, we assumed that every action in  $\mathcal{A}$  takes a unit-time delay in CFEs, and that every guard takes zero time delay. Then, we could possibly design a system where after choosing a particular branch of an alternative composition (e.g., after choosing c is true in  $c: p + \overline{c}: q$ ) and executing the first action of process p, the execution of this action would make  $\overline{c}$  true and thus also enable the execution of q. In order to avoid this erroneous behavior, we adopt a weaker version of the  $synchrony\ hypothesis\ [BS91]$ .

**Assumption 2.1** Let p be a process and c be a guard that guards the execution of p (defined as c:p). Any action of p is assumed to execute after c has been evaluated to true. In order words, c:p can be viewed as  $(c:e)\cdot p$ . First, the conditional is evaluated to true, then the process p that is guarded by c is executed, and other assignments to c will possibly affect future choices only.

## 2.3 Axioms of Control-Flow Expressions

The algebra of control-flow expressions inherits its formalism from a subset of process algebras [Bae90] that is suitable for describing synchronous reactive systems, called the algebra of regular synchronous processes. We further extend this algebra by specifying Boolean variables as guards of processes. We refer the reader to Appendix A for a definition of the algebra of synchronous processes similar to the one

found in [Bae90]. The following proposition relates control-flow expressions to the algebras of synchronous processes.

### **Proposition 2.1** CFEs are a subset of regular synchronous process algebras.

In this section, we present the axioms for the algebra of control-flow expressions by extending the axioms definitions of process algebras to handle actions and conditionals. These axioms provide the theoretical background that will be used to build the finite-state machine representation for control-flow expressions in Section 4.1.

In Table 2, we present the axioms of control-flow expressions, where a and b are multisets of actions,  $p, q, r \in \mathcal{F}$  (processes) and  $c_1, c_2, c_3 \in \mathcal{G}$  (guards).

The alternative composition has  $\delta$  as its identity component. It is commutative, and associates to the right or left. The sequential composition has  $\epsilon$  as its identity component. It associates to both the right and left, and it is only distributive to the left with respect to the alternative composition. This implies that  $p \cdot (c_1 : r + c_2 : s) \neq c_1 : p \cdot r + c_2 : p \cdot s$ . The intuitive meaning for  $p \cdot (c_1 : r + c_2 : s)$  being different from  $c_1 : p \cdot r + c_2 : p \cdot s$  is that we abstracted away the computation of p,  $c_1$  and  $c_2$ , and thus we cannot answer the question on whether an action in p affects the choice of  $c_1$  or  $c_2$ , or if the environment needs some value from p for making a decision on whether  $c_1$  or  $c_2$  should be true. If we assumed this transformation were valid, we could make the decision for all branches of the specification upon start by propagating the guards towards the beginning.

On the other hand, if we assumed that  $p \cdot (c_1 : r + c_2 : s)$  were equivalent to  $p \cdot c_1 : r + p \cdot c_2 : s$ , we would be in fact assuming that system were non-causal (its current choices depending on the future value of conditionals) and in this case we could also have propagated all those decisions to the initial start time of the system modeled by the CFE.

```

(+ is commutative)

(c_1:p+c_2:q)+c_3:r = c_1:p+(c_2:q+c_3:r) (+ is associative)

= c_1: p + c_2: q + c_3: r

(c_1: p+c_2: q) \cdot r = c_1: p \cdot r + c_2: q \cdot r (· distributes to the left with +)

(· is associative)

=

p \cdot q \cdot r

c_1:p+c_1:p

= c_1 : p

(+ is idempotent)

1 : p

0:p

c_1: p+\delta = c_1: p

(\delta is the identity element for +)

\delta \cdot p

(\delta is the zero element for \cdot)

(\epsilon is the identity element for \cdot)

\epsilon \cdot p

= (c_1 \wedge c_2) : p

c_1 : c_2 : p

if a \cup b synchronize

a||b|

= (a \cup b)

a||b| = \delta

if a \cup b does not synchronize

a||b|

= b||a|

a||0

a \mid \epsilon

a \cdot p||b \cdot q| = (a||b) \cdot (p||q)

a \cdot p || b = (a||b) \cdot p

(c_1: p + c_2: q)||r|| = c_1: (p||r) + c_2: (q||r)

```

Table 2: Axioms of control-flow expressions

The parallel composition assumes synchronous execution semantics, also known as maximal parallelism semantics. In these execution semantics, if two processes are executed in parallel, then one action of each process is executed atomically at the same time. We represent the actions that execute together by multisets of actions. For example, if multiset a defines  $\{a_1, \ldots, a_n\}$ , where each  $a_i \in \mathcal{A}$ , actions  $a_1, \ldots, a_n$  are executed at the same time. The set consisting of multisets of actions is represented here by the symbol  $\mathcal{M}^{\mathcal{A}}$ . If two multisets  $a = \{a_1, \ldots, a_n\}$  and  $b = \{b_1, \ldots, b_m\}$  are composed in parallel, the resulting multiset  $\{a_1, \ldots, a_n, b_1, \ldots, b_m\}$  is represented by  $a \cup b$ . We sometimes abuse our notation for multisets and use  $a_i$  for  $\{a_i\}$  if it can be

inferred by the context that  $a_i$  represents the multiset  $\{a_i\}$ .

In the definition of the axioms of CFEs, we showed that the result of the parallel composition of two multisets a and b is dependent on some synchronization between a and b. Although a formal definition of synchronization will be presented in the next chapter, we will give an informal definition that will allow the reader to understand its meaning.

Processes synchronize in control-flow expressions in two ways. The first way is by defining multisets of actions that always have to execute at the same time, or by defining multisets of actions that should never execute at the same time. The second method of synchronization is achieved by defining guards that generate a deadlock when conjoined.

Loops and infinite computations can be defined by control-flow expressions with process variables. The loop composition  $(c:p)^*$  is equivalent to recursive process  $q = c: p \cdot q + \overline{c}: \epsilon$ , where p is a process variable. The infinite composition  $p^{\omega}$  is equivalent to the recursive process  $q = p \cdot q$ . Their axioms can be determined by applying those equations into axioms of the original algebra.

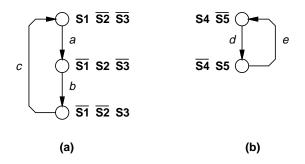

**Example 2.3.4.** We provide here an example of the representation of Verilog HDL constructs in control-flow expressions. The specification shown in Figure 8 consists of an algorithmic representation of a greatest common divisor. Its control-flow expression is represented by process p, where the labels on the right correspond to the actions being executed or the conditionals on alternative compositions.

$$p = [(r:0)^* \cdot b \cdot (c_1:(c_2:(c_3:c)^* \cdot d)^* \cdot e + \overline{c_1}:\epsilon)]^{\omega}$$

# 2.4 Extended Control-Flow Expressions

In the previous section, we presented the basic constructs for control-flow expressions capturing most of the control-flow constructs of structured languages. In this

```

module\ GCD(Xin, Yin, ready, result);

input [7:0] Xin, Yin;

input ready;

output [7:0] result;

reg [7:0] result, x, y;

always

begin

// conditional r

wait (ready)

\{x,y\} = \{Xin, Yin\};

// action b

if (x! = 0 \&\& y! = 0)

// conditional c1

begin

// conditional c2

while (y! = 0)

begin

// conditional c3

while (x >= y)

// action c

x = x - y:

\{x,y\} = \{y,x\};

// action d

\mathbf{end}

// action e

result = x;

\mathbf{end}

end

endmodule

```

Figure 8: Greatest-common divisor example

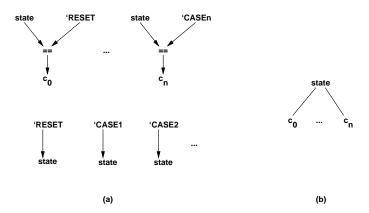

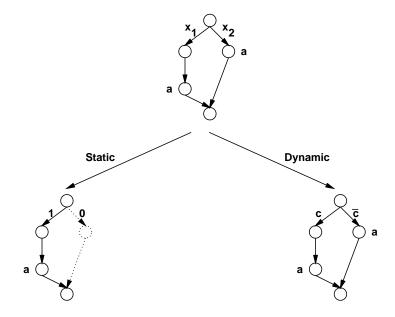

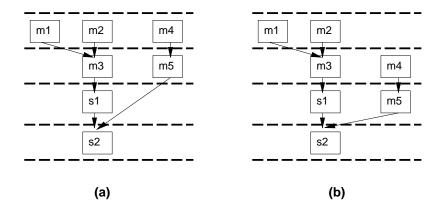

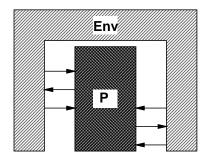

section we revise the control-flow expression model, and we extend it to incorporate exception handling mechanisms encountered in hardware description languages. Extended control-flow expressions (ECFEs) will be formally defined in Section 2.4.4, after having presented their motivation and usage.