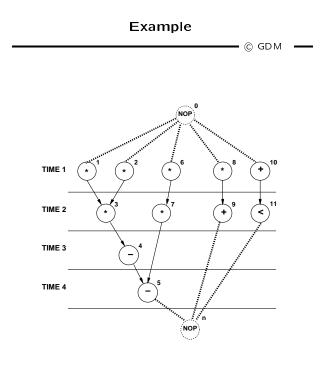

- Example: logic gate interconnection.

- Series/parallel execution of operations.

## Architectural-level synthesis

\_\_\_\_\_ © gdm \_\_

- Translate HDL models into sequencing graphs.

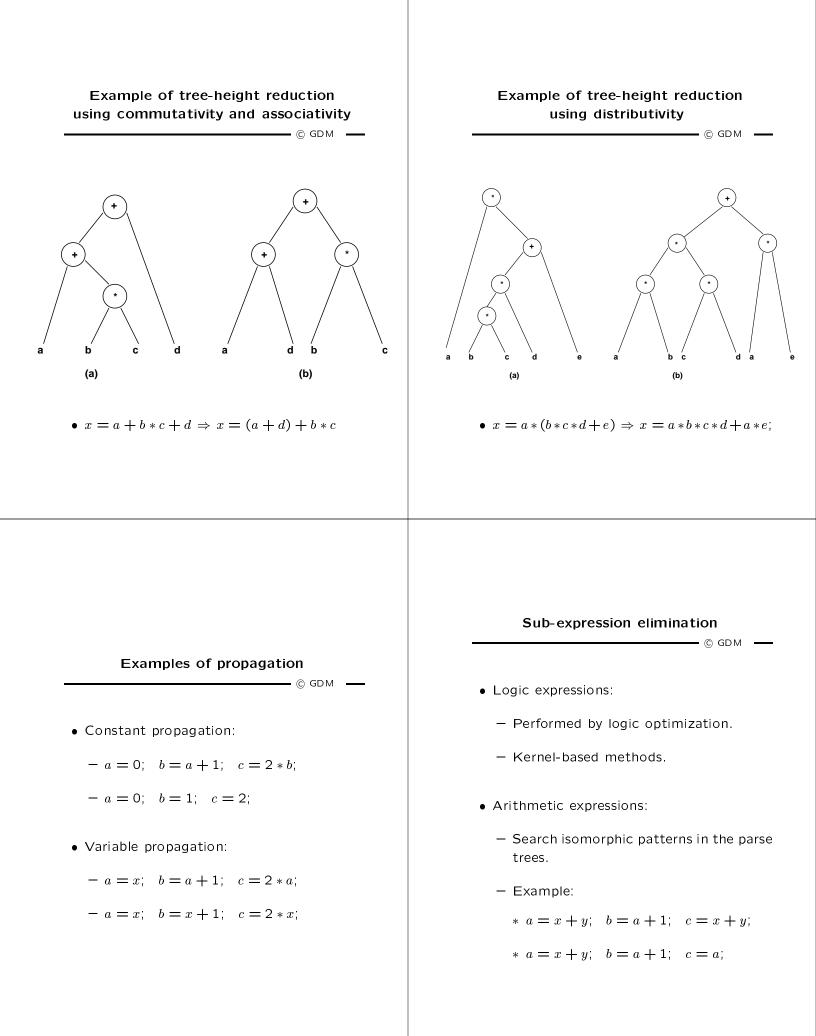

- Behavioral-level optimization:

- Optimize abstract models independently from the implementation parameters.

- Architectural synthesis and optimization:

- Create macroscopic structure:

- \* data-path and control-unit.

- Consider area and delay information of the implementation.

### Compilation and behavioral optimization

— © GDM -

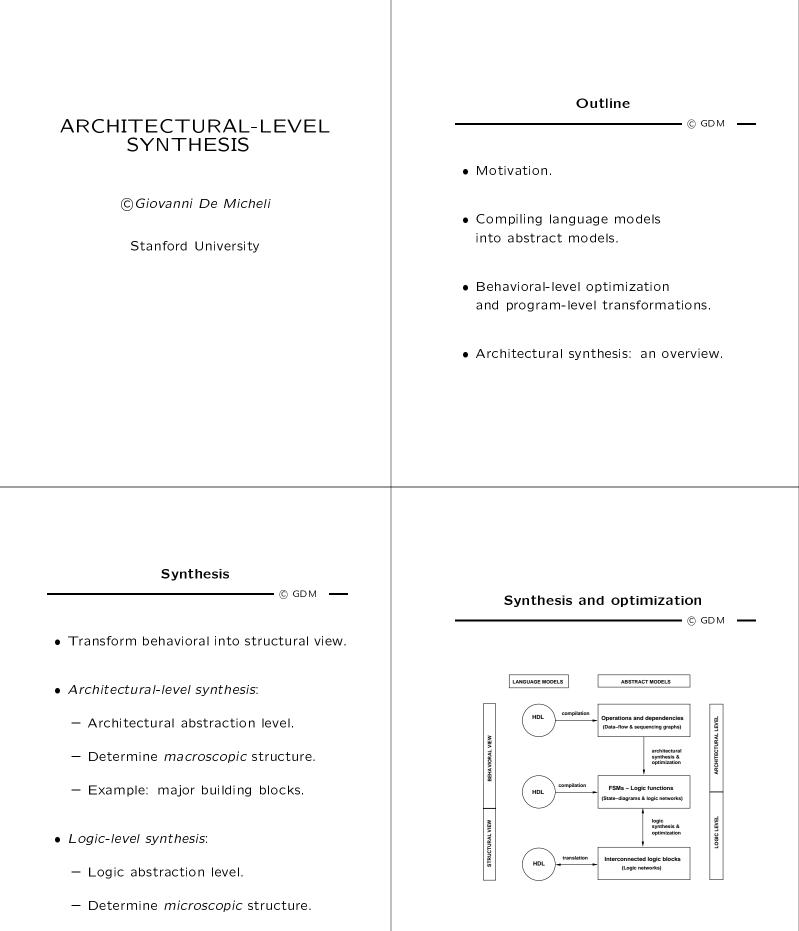

- Software compilation:

- Compile program into intermediate form.

- Optimize intermediate form.

- Generate target code for an architecture.

- Hardware compilation:

- Compile HDL model into sequencing graph.

- Optimize sequencing graph.

- Generate gate-level interconnection for a cell library.

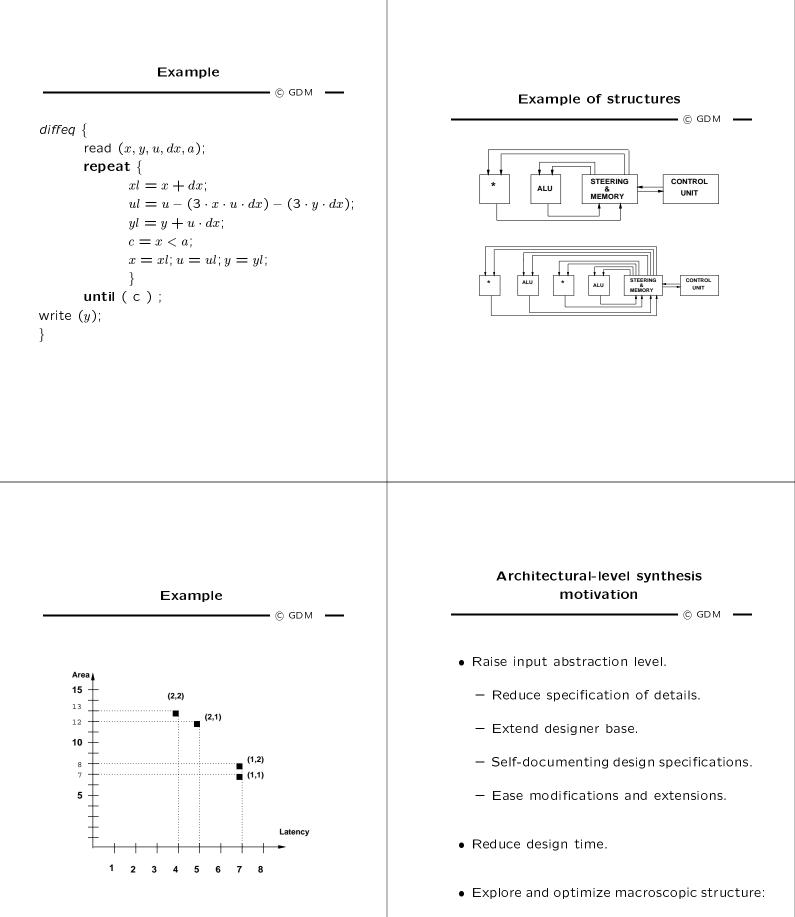

- © GDM • Front-end: - Lexical and syntax analysis. - Parse-tree generation. - Macro-expansion. - Expansion of meta-variables. • Semantic analysis:

- Data-flow and control-flow analysis.

- Type checking.

- Resolve arithmetic and relational operators.

- Standard resources:

- Existing macro-cells.

- Well characterized (area/delay).

- Example: adders, multipliers, ...

- Application-specific resources:

- Circuits for specific tasks.

- Yet to be synthesized.

- Example: instruction decoder.

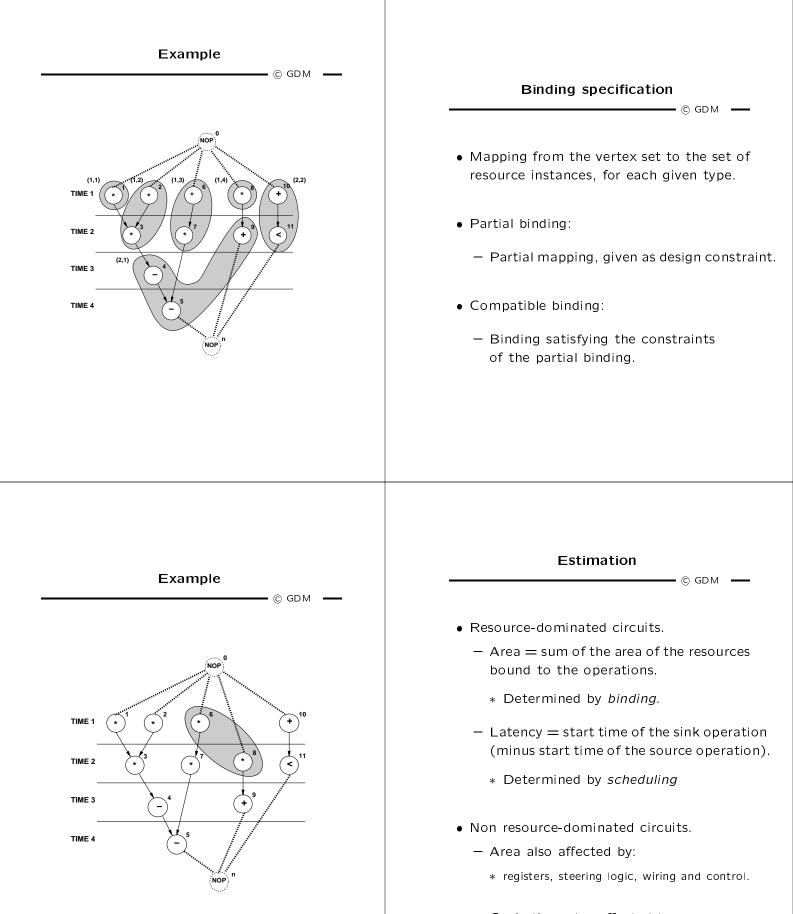

- Resource-dominated circuits.

- Area and performance depend on few, well-characterized blocks.

- Example: DSP circuits.

- Non resource-dominated circuits.

- Area and performance are strongly influenced by sparse logic, control and wiring.

- Example: some ASIC circuits.

## Implementation constraints

\_\_\_\_\_ © GDM \_\_\_

- Timing constraints:

- Cycle-time.

- Latency of a set of operations.

- Time spacing between operation pairs.

- Resource constraints:

- Resource usage (or allocation).

- Partial binding.

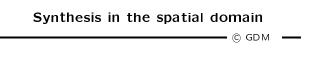

- Binding:

- Associate a resource with each operation with the same type.

- Determine area of the implementation.

- Sharing:

- Bind a resource to more than one operation.

- Operations must not execute concurrently.

- Bound sequencing graph:

- Sequencing graph with resource annotation.

- Cycle-time also affected by:

- \* steering logic, wiring and (possibly) control.

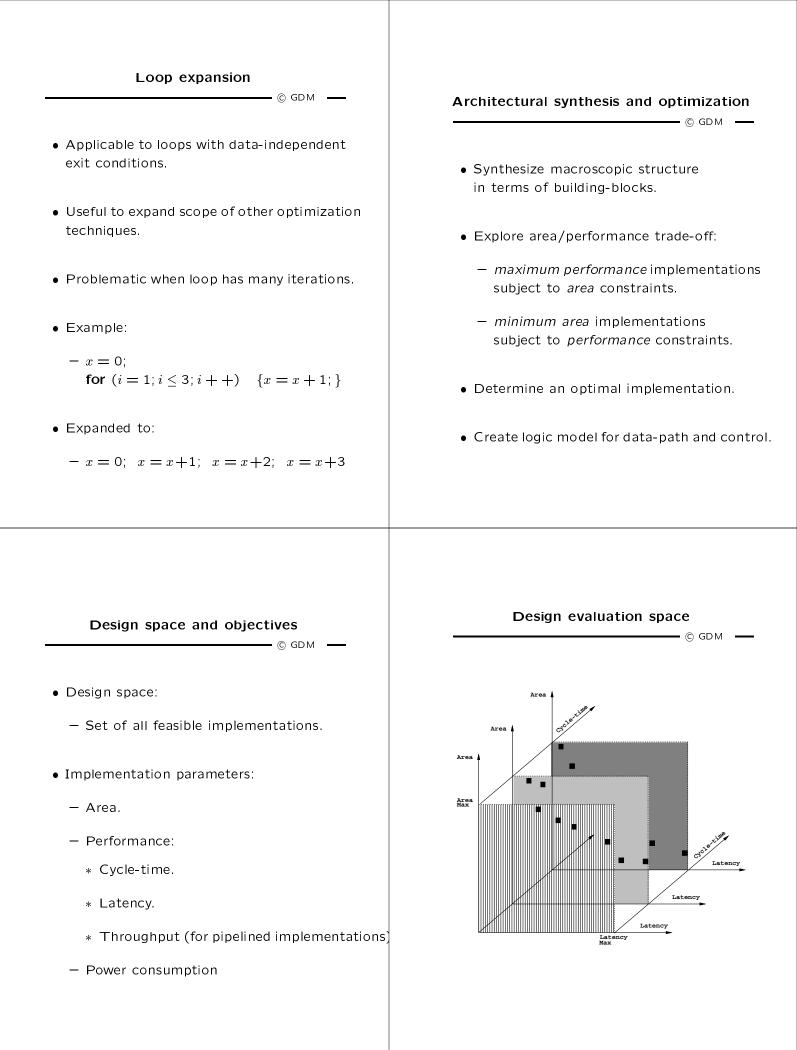

# Approaches to architectural optimization

\_\_\_\_\_ © GDM \_\_\_\_

- *Multiple-criteria* optimization problem:

- area, latency, cycle-time.

- Determine Pareto optimal points:

- Implementations such that no other has all parameters with inferior values.

- Draw trade-off curves:

- discontinuous and highly nonlinear.

# Approaches to architectural optimization

— © GDM —

- Area/latency trade-off,

- for some values of the cycle-time.

- Cycle-time/latency trade-off,

- for some binding (area).

- Area/cycle-time trade-off,

- for some schedules (latency).

### Area/latency trade-off

- Resource-dominated circuits:

- Area is determined by resource usage.

- Approaches:

- Schedule for minimum latency under resource constraints

- Schedule for minimum resource usage under latency constraints

- \* for varying constraints.

## Summary

\_\_\_\_ © GDM \_\_\_\_

- Behavioral optimization:

- Create abstract models from HDL models.

- Optimize models without considering implementation parameters.

- Architectural synthesis and optimization.

- Consider resource parameters.

- Multiple-criteria optimization problem:

- \* area, latency, cycle-time.