## **Practical Compilation of Quantum Programs**

Présentée le 12 août 2022

Faculté informatique et communications Laboratoire des systèmes intégrés (IC/STI) Programme doctoral en informatique et communications

pour l'obtention du grade de Docteur ès Sciences

par

### **Bruno SCHMITT ANTUNES**

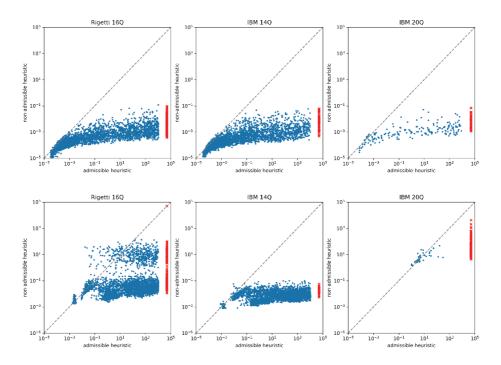

Acceptée sur proposition du jury

Prof. P. lenne, président du jury

Prof. G. De Micheli, Dr M. Soeken, directeurs de thèse

Prof. F. T. Chong, rapporteur

Prof. R. Wille, rapporteur

Prof. E. Charbon, rapporteur

# Acknowledgements

First, I wish to thank my advisor, Prof. Giovanni De Micheli, for accepting me into his research lab and providing guidance and support throughout my time at EPFL. I want to extend my most profound appreciation to my co-advisor, Dr. Mathias Soeken, whom I now consider a friend, for bringing me to EPFL, introducing me to the field of quantum computing, and for all the valuable ideas and discussions. This thesis would not have been possible without his help.

I also wish to thank my jury members Prof. Paolo Ienne, Prof. Edoardo Charbon, Prof. Frederic T. Chong, and Prof. Robert Wille, for judging the thesis and their helpful comments and suggestions.

I'm grateful to Dr. Martin Roetteler, Dr. Stephen Jordan from Microsoft, and Dr. Ali Javadi-Abhari from IBM for the opportunities to work on exciting summer internships. I'm also thankful to all colleagues I interacted with during these internships.

Throughout my years as a graduate student, I have worked alongside talented researchers and fellow students who have helped me in my research. For that, I wish to thank Alan Mishchenko, Heinz Riener, Siang-Yun (Sonia) Lee, Eleonora Testa, Giulia Meuli, Kaitlin Smith, Winston Haaswijk, Fereshte Mozafari, and all other LSI members.

My time in Lausanne would have been far less joyful if not for the friends I made there. I thank Delio, Fabian, Luis Henrique, Manuella, Jason, and Rabei. A big *obrigado* to my family and friends in Brazil, Netherlands, and Italy— especially Carmen Schmitt, Bruna Lacerda, Fabricio Pavan, Virgilio Peixoto, and Daniel Campelo for visiting me. I'm also grateful to my cousin Guilherme, his wife Juliana, and their son Noah for bringing great happiness to my weekends when they moved there: Thanks for all the family lunches.

Finally, I thank my parents and brothers, to whom I dedicate this thesis, for their immeasurable support during this journey. They are the inspiration that keeps me aiming at higher goals in my life.

Lausanne, June 16, 2022

Bruno Schmitt

## Abstract

It's been a little more than 40 years since researchers first suggested exploiting quantum physics to build more powerful computers. During this time, we have seen the development of many quantum algorithms and significant technological advances to make these devices. As a result, at this point, large-scale quantum computers, capable of providing valuable solutions to complex problems, seem like a certainty, even if still distant.

Nonetheless, there is a great gap between the communities of quantum algorithms and quantum devices researchers. On the one hand, algorithm designers most often describe algorithms in a high level of abstraction, using a mixture of natural language, pseudocode, and mathematical formulas—a form deriving asymptotic complexity estimates while shielding researchers from the low-level complexities and restrictions. On the other hand, physical devices only understand algorithms implemented using the primitive low-level abstractions they support.

Most programming systems available for quantum computing are intertwined with the quantum circuit model, so developers must implement algorithms in terms of low-level unitary operators. Not surprisingly, the implementation of quantum algorithms on such a low level of abstraction is very time-consuming, error-prone, and results in non-portable programs—given the technological diversity of quantum devices.

In this thesis, I study problems related to the compilation of quantum programs, seeking forms of augmenting the expressive power of current frameworks and narrowing the gap between algorithmic research and concrete implementations. I focus on scalability and practicality—in particular, together with theoretical investigations, I developed concrete algorithms that are performant and scalable. The embodiment of my research contribution is a compiler companion library for the synthesis and compilation of quantum circuits called tweedledum.

**Keywords:** design automation, logic synthesis, reversible logic, compilation, quantum computing, quantum programming.

# Zusammenfassung

Es ist etwas mehr als 40 Jahre her, dass Wissenschaftler zum ersten Mal Quantenphysik als Grundlage für leistungsstarke Computer vorgeschlagen haben. Seitdem beobachten wir die Entwicklung vieler Quantenalgorithmen sowie signifikante technologische Durchbrüche. All dies führt heutzutage zu einer hohen Zuversicht, dass leistungsstarke Quantencomputer in der Zukunft-wenn auch weit entfernt-wertvolle Lösungen zu komplexen Problemen liefern werden.

Nichtsdestotrotz existiert eine große Abstraktionsdifferenz zwischen Wissenschaftlern im Bereich von Quantenalgorithmen und denen, die an physikalischen Quantencomputern arbeiten. Entwickler von Quantenalgorithmen beschreiben jene mit einer Mischung aus natürlicher Sprache, Pseudocode, sowie mathematischen Formeln oft auf einer sehr hohen Abstraktionsebene. Dabei leiten sie asymptotische Komplexitätsergebnisse her, ohne auf die Implementierungsdetails unterer Abstraktionsebenen einzugehen, die von konkreten physikalischen Quantencomputern verstanden werden.

Die meisten Programmiersysteme für Quantencomputer sind stark mit dem Quantenschaltkreis Modell verflochten. Daher müssen Programmierer Algorithmen auf Basis von maschinennahen unitären Operationen implementieren. Es überrascht nicht, dass dies sehr zeitintensiv und fehleranfällig ist. Zudem lassen sich die Programme nicht einfach portieren, da verschiedene Quantencomputer sehr unterschiedliche Fähigkeiten haben.

In dieser Dissertation untersuche ich Compiler von Quantenprogrammen. Diese erweitern existierende Programmiersysteme durch Ausdrucksmöglichkeiten auf höheren Abstraktionsebenen und führen schlussendlich dazu, dass die Abstraktionsdifferenz zwischen algorithmischen Beschreibungen und konkreten Implementierungen verringert wird. Den Fokus lege ich auf Erweiterbarkeit, Performanz, und praktische Anwendbarkeit. Basierend auf theoretischen Untersuchungen habe ich neue performante und universelle Algorithmen entwickelt. Die Softwarebibliothek tweedledum fasst meine Arbeit zusammen und erlaubt die Integration meiner wissenschaftlichen Beiträge in existierende Programmiersysteme für Quantencomputer.

Schlüsselwörter: Entwurfsautomatisierung, Logiksynthese, reversible Logik, Compilation, Quantencomputer, Programmierung von Quantencomputern

# Contents

|    |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $egin{array}{c} { m ements} \\ { m nglish/Deutsch)} \end{array}$ | ii         |

|----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|------------|

|    |      | `                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                  | 11         |

| In |      | uction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                  |            |

|    | Con  | tributio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $\mathrm{ons}$                                                   |            |

|    | Out  | line .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                  | '          |

| Ι  | Ba   | ckgrou                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ound                                                             | Į.         |

| 1  | Log  | ic syn                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | nthesis                                                          | ,          |

|    | 1.1  | Boole                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ean functions                                                    |            |

|    | 1.2  | Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | e data structures                                                |            |

|    |      | 1.2.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Truth table                                                      |            |

|    |      | 1.2.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Two-level expressions                                            |            |

|    |      | 1.2.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Binary decision diagrams                                         |            |

|    |      | 1.2.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Multi-level logic networks                                       | 1          |

|    | 1.3  | Boole                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ean satisfiability                                               | 1          |

| 2  | Qua  | antum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | o computing                                                      | 1          |

|    | 2.1  | Quant                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ntum bits                                                        |            |

|    | 2.2  | Quant                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | tum operators                                                    | $\dots$ 10 |

|    | 2.3  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | circuit model                                                    |            |

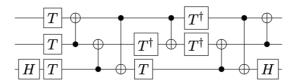

|    | 2.4  | Repre                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | esentation of quantum functionality                              |            |

|    | 2.5  | Oracle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | les                                                              | 20         |

| II | Sy   | $ olimits_{nthes} olimits_{nt$ | sis                                                              | 23         |

| 3  | Intr | oduct                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | tion to quantum circuits synthesis                               | 2          |

|    | 3.1  | Synth                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | hesis problems                                                   | 20         |

viii CONTENTS

| 4 | ESC | OP-based synthesis                              |

|---|-----|-------------------------------------------------|

|   | 4.1 | Motivation                                      |

|   | 4.2 | Contributions                                   |

|   | 4.3 | Previous work                                   |

|   | 4.4 | Divide-and-conquer extraction                   |

|   |     | 4.4.1 Selection heuristics                      |

|   | 4.5 | Experimental results                            |

|   | 4.6 | Use case: ESOP-based reversible logic synthesis |

|   |     | 4.6.1 Experimental results                      |

|   | 4.7 | Summary                                         |

| 5 | XA  | G-based synthesis                               |

|   | 5.1 | Motivation                                      |

|   | 5.2 | Contributions                                   |

|   | 5.3 | Previous work                                   |

|   | 5.4 | Synthesis flow                                  |

|   | 5.5 | Experimental results                            |

|   | 5.6 | Summary                                         |

| 6 | Syn | abolic algorithms for permutation synthesis     |

|   | 6.1 | Motivation                                      |

|   | 6.2 | Technical background                            |

|   |     | 6.2.1 Graphs                                    |

|   |     | 6.2.2 Permutation                               |

|   |     | 6.2.3 Reconfiguration problems                  |

|   |     | 6.2.4 State space                               |

|   |     | 6.2.5 Decision diagrams                         |

|   | 6.3 | Contributions                                   |

|   | 6.4 | A*-based algorithm                              |

|   | 6.5 | SAT-based algorithm                             |

|   | 6.6 | $\pi$ DD-based algorithm                        |

|   | 6.7 | Experimental results                            |

|   | 6.8 | Summary                                         |

| 7 | SAT | Γ-based linear synthesis                        |

|   | 7.1 | Motivation                                      |

|   | 7.2 | Technical background                            |

|   | 7.3 | Previous work                                   |

|   | 7.4 | Contributions                                   |

|   | 7.5 | Synthesis algorithm                             |

|   | 7.6 | Discussion                                      |

| CONTENTS | ix |

|----------|----|

|----------|----|

| III | <b>C</b> | ompilation                                  | <b>7</b> 5 |

|-----|----------|---------------------------------------------|------------|

| 8   | Intr     | oduction to compilation of quantum programs | 77         |

|     | 8.1      | Contributions                               | 79         |

| 9   | The      | tweedledum library                          | 81         |

|     | 9.1      | The intermediate representation             | 81         |

|     |          | 9.1.1 Fundamental concepts                  | 81         |

|     | 9.2      | Synthesis                                   | 83         |

|     | 9.3      | Compilation                                 | 85         |

|     |          | 9.3.1 Utility                               | 85         |

|     |          | 9.3.2 Decomposition                         | 86         |

|     |          | 9.3.3 Mapping                               | 87         |

|     |          | 9.3.4 Optimization                          | 91         |

|     | 9.4      | Show case: Boolean function compilation     | 93         |

|     |          | 9.4.1 IBM's challenge: The Zed city problem | 97         |

|     | 9.5      | Show case: Mapping                          | 99         |

|     | 9.6      | Summary                                     | 101        |

| 10  | Con      | clusion                                     | 103        |

|     | 10.1     | Future directions                           | 104        |

| Bil | bliog    | raphy                                       | 107        |

| Cu  | ırricı   | ılum Vitae                                  | 123        |

## Introduction

The history of quantum computing dates back to the early 1980s when Paul Benioff demonstrated a quantum mechanical model of a Turing machine [23]. Around the same time, Yuri Manin and Richard Feynman argued about the inherently exponential cost of simulating generic quantum systems using conventional classical digital computers [89, 60]. Feynman suggested, in his work, that a computer that uses quantum mechanical phenomena for computation might simulate quantum systems more efficiently. Since then, a series of papers [53, 39, 27, 8] have formalized an abstract model of quantum computation and the concept of a quantum Turing machine, and many researchers have striven to build such devices.

Technology advances have motivated a new wave of investment in quantum research in the past few years. Today we are in the Noise Intermediate-Scale Quantum (NISQ, [110]) era, characterized by the appearance of quantum computers with sizes ranging from fifty to a few hundred qubits—e.g., IBM recently announced a 127-qubit device [3]. At this point, large-scale quantum computers, capable of providing valuable solutions to complex problems, seem like a certainty, even if still distant. As a result, we have seen a rapid increase in research to create new quantum algorithms and research to develop design tools for quantum computers. I refer to the "Quantum Algorithm Zoo" website for algorithmic advances [76]; It holds a comprehensive list of quantum algorithms with their respective speed-up factors. On the design tool front, we have seen the appearance of a large variety of programming environments—for instance Q# [145], Silq [28], Quipper [68], Qiskit [150], Cirq [55] PyQuil/Forest [131], Pennylane [26], ProjectQ [142], StrawberryFields [78]. Such frameworks aim to bridge the gap between algorithm researchers and developers by providing ways of implementing quantum algorithms using a programming language or API, which a compiler translates into an executable format for a quantum device.

Nonetheless, the gap between these communities is still significant. Quantum algorithm designers often work at a high level of abstraction and do not consider current frameworks and hardware capabilities a limiting factor when conceiving and describing new algorithms [41]. On the other hand, most programming systems available for quantum computing are intertwined with the quantum circuit model, so developers must implement algorithms in terms of low-level unitary operators. Not surprisingly, the implementation of quantum algorithms on such a low level of abstraction is very time-consuming, error-prone, and results in non-portable programs—given the technological

2 CONTENTS

diversity of quantum devices.

Besides being essential for executing programs on physical devices, designs tools also play an indispensable role in resource estimation, i.e., estimating resources required to implement quantum algorithms on future fault-tolerant hardware. There is a whole field of resource estimation that is motivated by the need to understand better the power of quantum computing to make policy decisions, stimulate investment, and guide research towards technological advances that will lead to scalable devices.

In this thesis, I study problems related to the compilation of quantum programs, seeking forms of augmenting the expressive power of current frameworks and narrowing the gap between algorithmic research and concrete implementations. I focus on scalability and practicality—in particular, alongside theoretical investigations, I developed concrete algorithms that are performant and scalable. The embodiment of my research contribution is a compiler companion library for the synthesis and compilation of quantum circuits called tweedledum. In contrast to most solutions, I designed it to enhance other compilers and frameworks, and some of these tools indeed use it already. The following section briefly outlines the contributions.

#### CONTRIBUTIONS

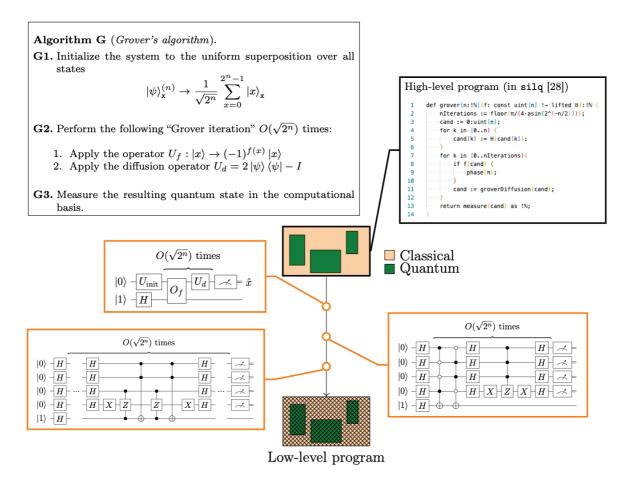

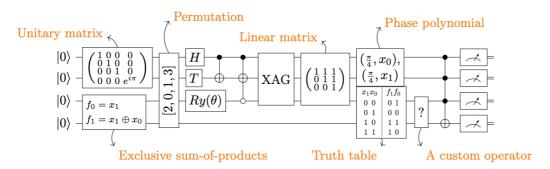

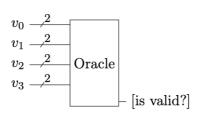

Many quantum algorithms use operations with classically described behavior, particularly oracular ones [70, 40, 88, 118, 143, 46]. An algorithm uses an oracle to access a Boolean function, i.e., it queries the oracle on some input to obtain the corresponding function's output.

Researchers use oracles extensively when studying quantum algorithms' complexity because counting the number of queries required to evaluate a function is more straightforward than counting the number of computational steps. Thus, to try inferring nontrivial lower bounds more readily, investigators characterize the computational complexity by the asymptotic growth rate of the number of queries with growing input size—an analysis that only assumes the existence of an oracle.

However, a developer needs to provide a concrete implementation of the whole algorithm, oracles included, to execute it on an actual device or accurately estimate the resources necessary to perform such algorithms. Such an implementation must consist of a sequence of elementary quantum operators supported by the underlying hardware. Furthermore, due to the physical properties of quantum states, all quantum operations need to be reversible; thus, a classical function that defines the oracle's behavior must be reversible, a characteristic not often found in real-world problems. On the contrary, we often employ quantum oracles defined by complex, irreversible functions.

Using most of today's frameworks, we have an impractical situation. We are demanding developers to reversibly implement the desired function using low-level quantum operations while attempting to minimize quantum resources usage, i.e., the number of qubits and operations.

This thesis aims at remedying this situation by allowing designers to implement the

CONTENTS 3

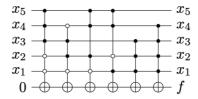

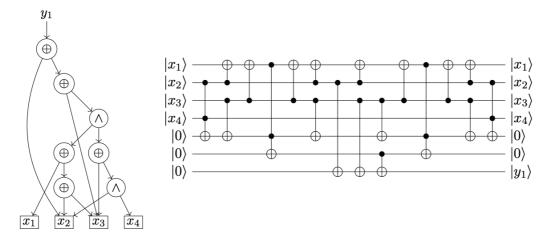

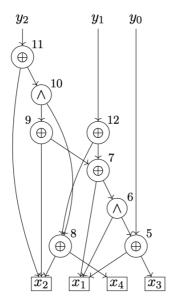

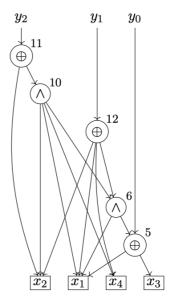

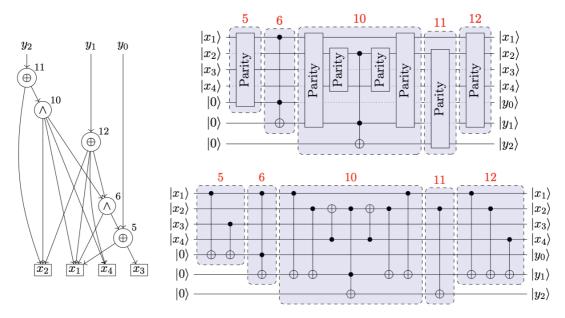

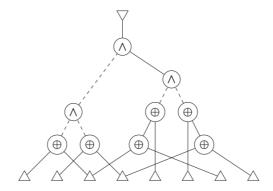

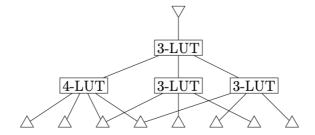

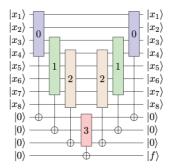

complicated classical subroutines on a high level of abstraction and then automatically translate such implementations into low-level quantum circuits. We present various contributions that support our goal. The first tackles the problem of ESOP-based synthesis scalability [137], a technique capable of generating reversible circuits with an optimal number of qubits due to a natural affinity between exclusive sum-of-products (ESOP) expressions and Toffoli gates. We describe a new algorithm that outperforms state-of-the-art methods in both scalability and effectiveness. This improvement also benefits some hierarchical synthesis techniques, specifically those relying on direct synthesis to generate circuits for small logic functions decomposed from a large one, e.g., LUT-based hierarchical reversible logic synthesis (LHRS) [138]. It enables those methods to split a logic function into fewer pieces, which, in turn, can minimize the number of required qubits.

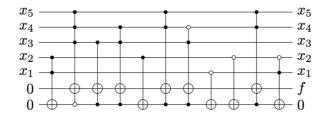

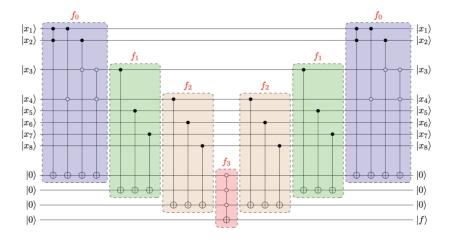

The second contribution is an improvement to a hierarchical synthesis algorithm specifically designed to work on xor-and inverter graphs (XAG). This technique synthesizes circuits over a fault-tolerant gate set, Clifford+T, and focuses on minimizing the total number of gates and, more specifically, the number of T gates, which are more expensive to error correct [11, 63]. The improved technique can significantly reduce the number of qubits and Clifford gates. Crucially, these improvements are possible without increasing the number of T gates or the execution time.

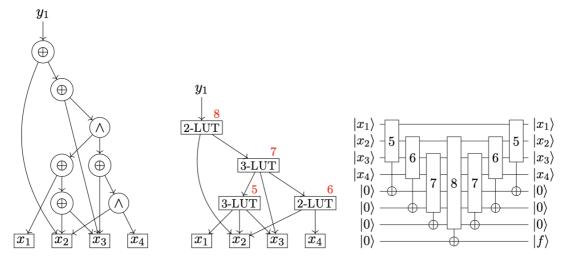

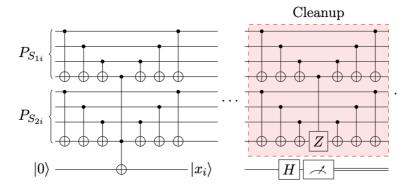

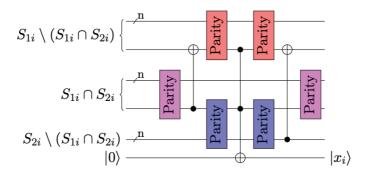

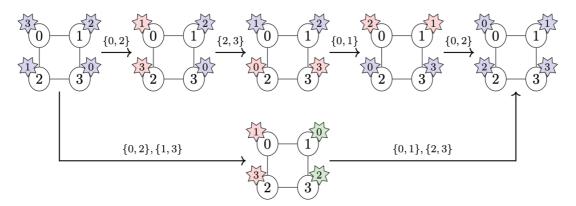

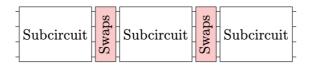

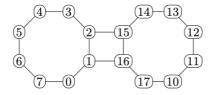

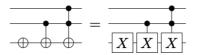

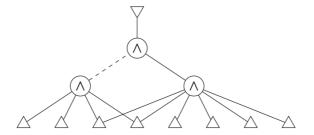

The thesis also presents the results of research directed towards the development and analysis of symbolic algorithms for solving two reconfiguration problems [12, 155] that appear in the context of quantum circuit mapping, which is the process of modifying a high-level circuit that assumes full qubit connectivity, into a lower-level one that respects the device's connectivity (or coupling) constraints. This process is an essential step during the compilation and frequently requires the inclusion of additional operations, in this case, SWAP operations. We can use the three proposed algorithms to do the mapping itself or as a post-mapping optimization technique. All three algorithms guarantee local optimality, i.e., they generate permutation circuits with the optimal number of SWAPs or optimal depth.

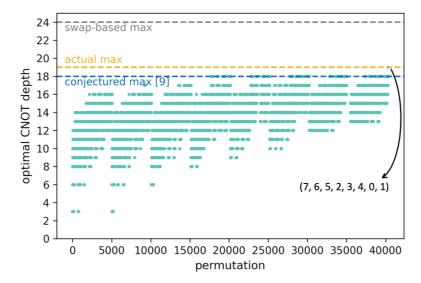

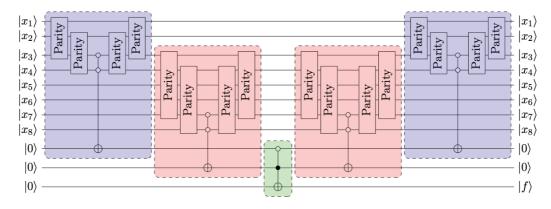

While performant, SWAP-based mappers and the synthesis of permutation circuits using SWAPs are suboptimal. The reason is that today's quantum hardware cannot execute SWAP gates directly. Thus, we must translate SWAPs into a sequence of CNOT gates during compilation. In various applications, the cost of these subcircuits dominates the total costs. Fortunately, we can improve the implementation of permutation circuits by leveraging the properties of the CNOT gate. The last synthesis technique we present in this thesis is the SAT-based method for generating linear reversible circuits [108], i.e., those that are composed only of CNOT gates. Although this technique is much more general, we mainly employ it to synthesize permutation circuits and disprove a 15-year-old conjecture that reversal is at least as depth-intensive to synthesize with CNOTs as any other permutation on a path [83].

Finally, we present tweedledum, an extensible and efficient open-source library for quantum circuit synthesis and compilation. It has state-of-the-art performance in many 4 CONTENTS

compilation tasks relevant to NISQ and fault-tolerant applications. We describe most of its state-of-the-art techniques for synthesizing and compiling quantum circuits, alongside practical implementation improvements to some of them, and the library's core: an intuitive and flexible intermediate representation that supports different abstraction levels across the same circuit structure.

The contributions above are published in [123, 124, 120, 119, 37]. In addition to the work described here, other publications completed during my doctoral studies include [136, 135, 93, 130, 113, 134, 122].

#### **OUTLINE**

This thesis is divided into three parts:

- Part I (Chapters 1 and 2) covers background material most of necessary for this thesis. Chapter 1 introduces concepts from the field of classical logic synthesis and some of the various ways employed to represent Boolean functions. Chapter 2 provides a brief introduction to quantum computing.

- Part II (Chapters 3 to 7) covers synthesis algorithms. In Chapter 3, we introduce quantum circuit synthesis. Chapters 4 and 5 tackle the problem of synthesizing large, complex, irreversible Boolean functions into quantum circuits. Chapter 6 studies two problem on graphs that appear in the context of quantum circuit mapping and provide three SWAP-based algorithms to synthesize permutation circuits. Lastly, Chapter 7 deals with the optimal synthesis of linear circuits.

- Part III (Chapters 8 and 9). Chapter 8 briefly introduces the whole compilation process for quantum programs. In Chapter 9 we describe tweedledum—an compiler companion library for the synthesis and compilation of quantum circuits that embodies our research. We demonstrate its power using two show case examples: oracle synthesis and quantum circuit mapping.

# Part I Background

## Chapter 1

# Logic synthesis

As general notation, we are using  $[n] = \{1, ..., n\}$ .

#### 1.1. BOOLEAN FUNCTIONS

A Boolean variable x is a variable that takes one of the two values from the domain  $\{\text{false}, \text{true}\}$ , or  $\{0,1\}$ . Variables are often denoted by  $x_1, x_2, x_3, \ldots$ ; but we will often find it convenient to use just the numerals  $1, 2, 3, \ldots$  to stand for variables, or write just j instead of  $x_j$ , because it takes less space. A positive literal is the Boolean variable x and a negative literal is its complement  $\bar{x}$ . Similarly to variables, we can write '2' to denote the ' $x_2$ ' literal, and ' $\bar{2}$ ' for its complement. The Boolean AND of k literals is a cube, or product, i.e.,  $c = l_1 \wedge \cdots \wedge l_k$  (we may omit the symbol  $\wedge$  in forming cubes, e.g.,  $l_1 \wedge \cdots \wedge l_k = l_1 \cdots l_k$ ). If a variable is not represented by a positive literal or a negative literal in a cube, then its value is said to be a don't care literal. A minterm is a cube, in which every variable is represented by either a negative or positive literal. A cube with k don't care literal values covers  $2^k$  minterms.

A multiple-output Boolean function  $f: \{0,1\}^n \to \{0,1\}^m$  maps n Boolean input variables to m Boolean output values. We refer to

$$\mathbb{B}_{n,m} = \{ f \mid \{0,1\}^n \to \{0,1\}^m \}$$

(1.1)

as the set of all multiple-output Boolean functions with n inputs and m outputs, where  $m, n \geq 1$ . We write  $\mathbb{B}_n = \mathbb{B}_{n,1}$  to denote the set of all single-output Boolean functions. We can represent f as a m-tuple of n-variable Boolean functions  $(f_1, \ldots, f_m)$  where  $f_i \in \mathbb{B}_n$  for each  $i \in [m]$  and thus  $f(x) = (f_1(x), \ldots, f_m(x))$  for each  $x \in \{0, 1\}^n$ . We use  $y_1, \ldots, y_{m-1}$  to denote the outputs of a function.

The support of f is the subset of variables that influence the output value of the function f. Unless stated otherwise, we assume that a Boolean function is completely specified. The cofactors are derived from the function by substituting constant values for the input variables. For example, Boole's expansion of a function f, often called Shannon's expansion, where  $f_{\bar{x}_i} = f(x_i = 0)$  and  $f_{x_i} = f(x_i = 1)$  are the negative and

positive cofactors of the function f with respect to variable  $x_i$ , respectively.

#### 1.2. LOGIC DATA STRUCTURES

This section introduces the data structures used in this thesis for logic synthesis and optimization. These include truth tables, two-level expressions, binary decision diagrams, and multi-level logic networks.

#### 1.2.1 Truth table

A natural way of representing a Boolean function is through the exhaustive enumeration of its mapping, thus creating a table in which every truth assignment of its input variables has a corresponding function value listed. A *truth table* is precisely that.

**Example 1.1.** The function  $prime_3(x)$  takes a 3-bit number and returns true if this number is prime, i.e.,  $prime_3(x) = [(x_3x_2x_1)_2 \text{ is prime}]$ . We can represent it using the following truth table:

| $x_3$ | $x_2$ | $x_1$ | $prime_3$ |

|-------|-------|-------|-----------|

| 0     | 0     | 0     | 0         |

| 0     | 0     | 1     | 0         |

| 0     | 1     | 0     | 1         |

| 0     | 1     | 1     | 1         |

| 1     | 0     | 0     | 0         |

| 1     | 0     | 1     | 1         |

| 1     | 1     | 0     | 0         |

| 1     | 1     | 1     | 1         |

Note that the input side of a truth table is redundant, e.g., given two functions with the same number of inputs, their truth table will only differ on the output column. Hence, we can represent the truth table for a Boolean function f as a bitstring  $b_{2^n-1} \dots b_1 b_0$  where  $b_x = f(x)$  when  $x = (x_n \dots x_1)_2$ . In other words, each character in the bitstring corresponds to the function value of f evaluated at some assignment to its variables. The most-significant bit  $b_{2^n-1}$  corresponds to  $f(1, \dots, 1)$  and the least-significant bit  $b_0$  corresponds  $f(0, \dots, 0)$ . Thus the truth table representation for the prime<sub>3</sub>(x) function in Example 1.1 is 10101100, or 0xAC in hexadecimal.

Unfortunately, truth tables are impractical to represent large functions because their size grows exponentially with the number of input bits,  $2^n$ . Nonetheless, they are tremendously useful to represent and manipulate small functions. For functions with up to 16 variables, truth tables are typically much faster than alternative representations. Furthermore, truth tables are canonical representations of Boolean functions: Two Boolean functions are equivalent if and only if they have the same truth table. Canonicity is a valuable property in many applications.

#### 1.2.2 Two-level expressions

We can also use Boolean expressions composed of literals, an inner operator, and an outer operator to represent Boolean functions. For example, the sum-of-products (or SOP) representation has ' $\wedge$ ' (logical AND) as inner operator and ' $\vee$ ' (logical OR) as outer operator. An SOP for an n-variable Boolean function has the form:

$$f(x_n, \dots, x_1) = \bigvee_{i=1}^{m} (x_n^{p_{n,i}} \wedge \dots \wedge x_1^{p_{1,i}})$$

(1.2)

for some m and polarities  $p_{j,i} \in [3]$ , meaning  $x_j^0 = 1$  (a  $don't \ care$ ),  $x_j^1 = \bar{x}_j$ , and  $x_j^2 = x_j$ . Note that each term corresponds to a cube, and their order does not change the function. An SOP evaluates to true if  $at \ least \ one$  term is true. An SOP in which all terms are minterms and unique (i.e., without repetition) is canonical for a function up to the terms' order. However, such SOPs are not of much practical interest. In general, we are interested in finding the most concise SOP-form for a Boolean function. Such forms are not canonical, and finding them is an intractable problem (in fact, NP-complete []).

**Example 1.2.** The function  $prime_4(x)$  takes a 4-bit number and returns true if this number is prime, i.e.,  $prime_4(x) = [(x_4x_3x_2x_1)_2 \text{ is prime}]$ . We can represent it using the following SOP:

$$\begin{aligned} \text{prime}_4(x) &= \bar{x}_4 \bar{x}_3 x_2 \bar{x}_1 \vee \bar{x}_4 \bar{x}_3 x_2 x_1 \vee \bar{x}_4 x_3 \bar{x}_2 x_1 \\ &\vee \bar{x}_4 x_3 x_2 x_1 \vee x_4 \bar{x}_3 x_2 x_1 \vee x_4 x_3 \bar{x}_2 x_1 \end{aligned}$$

or, more concisely:

$$prime_4(x) = x_3\bar{x}_2x_1 \vee \bar{x}_3x_2x_1 \vee \bar{x}_4x_3x_1 \vee \bar{x}_4\bar{x}_3x_2.$$

In quantum computing, implementing logical exclusive-OR (XOR) is cheaper than implementing logical OR. Hence, the use of two-level forms focuses on a crucial variation of (1.2) that emerges when changing the outer operator ' $\vee$ ' to ' $\oplus$ '. Such an expression is called *exclusive-or sum-of-products* (ESOP).

**Example 1.3.** The function  $prime_4(x)$  takes a 4-bit number and returns true if this number is prime, i.e.,  $prime_4(x) = [(x_4x_3x_2x_1)_2 \text{ is prime}]$ . We can represent it using the following ESOP:

$$prime_4(x) = x_4x_2x_1 \oplus x_3x_1 \oplus \bar{x}_4\bar{x}_3x_2.$$

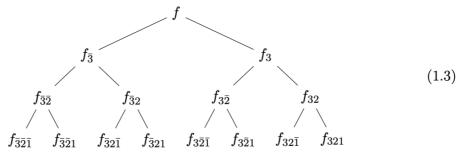

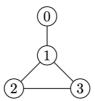

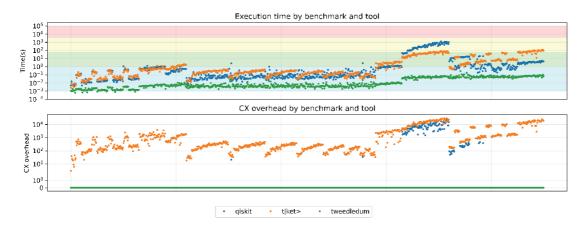

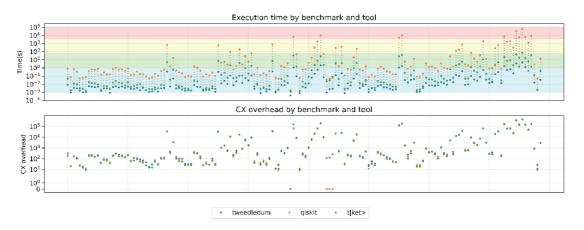

#### 1.2.3 Binary decision diagrams